FPGA-based IRIG-B(DC) fast decoding method

A decoding method and fast technology, applied in pulse conversion and other directions, can solve problems such as difficult debugging, large volume, and low integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

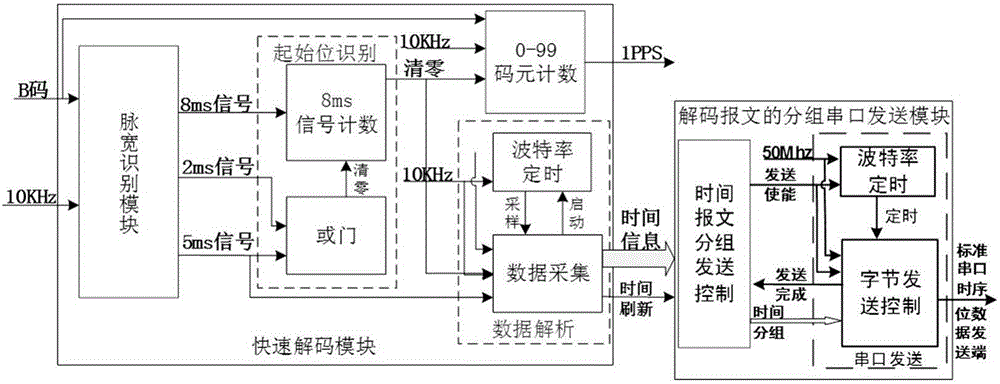

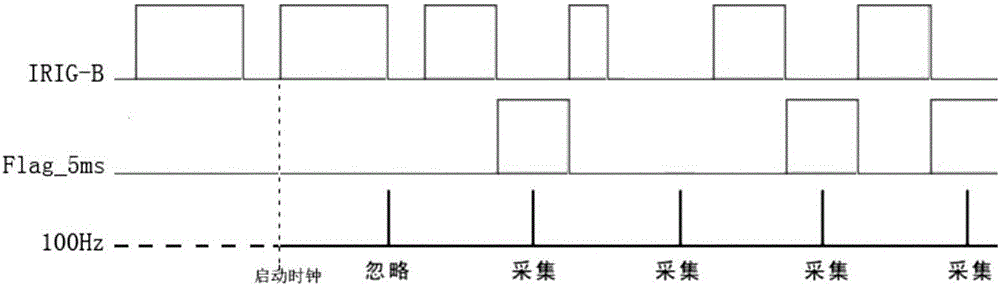

[0015] The embodiment of the present invention will be described in further detail below in conjunction with the accompanying drawings, and the following specific implementation content and figure 2 The realization schematic diagram of fast decoding of IRIG-B (DC) code will be included in the protection scope of the present invention.

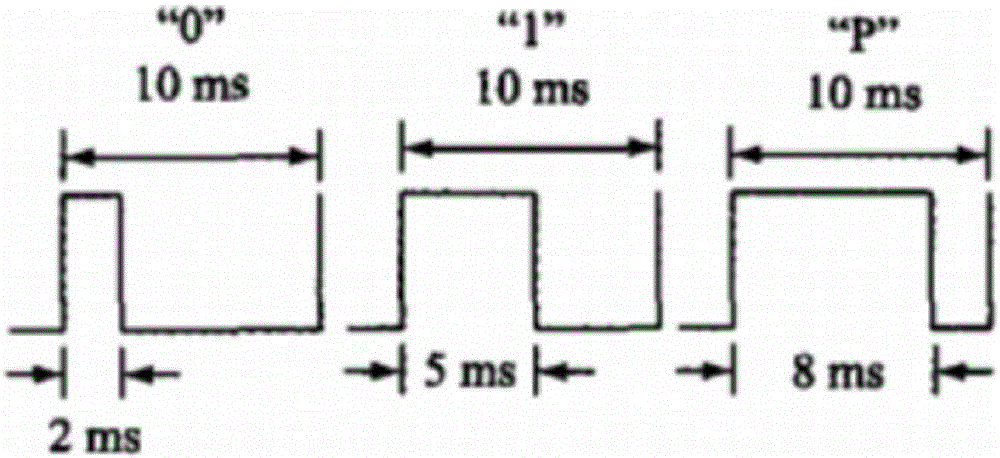

[0016] IRIG-B (DC) code (referred to as B code) is a BCD serial time code, each symbol width is 10ms, which is pulse width code (such as figure 1 As shown, the pulse width 2ms, 5ms and 8ms respectively represent the binary "0", "1" and the time frame reference mark P R or position identification mark P). A time frame period includes 100 symbols, and the "punctual" reference point of a symbol is its pulse leading edge, starting from the time frame reference mark P R Counting from the beginning, there is a position identification mark P every 10 symbols, and their pulse width is 8ms. Therefore, two consecutive pulses with a pulse width of 8ms...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More