Clock duty ratio adjusting circuit

A technology to adjust the circuit and duty cycle, which is applied in the direction of electrical components, generating electric pulses, and electric signal transmission systems, etc. It can solve the problems of inability to guarantee the stability of the clock signal duty cycle, affecting clock jumps and inversions, and functional errors. To achieve the effect of simplifying the signal output path, speeding up the start-up process, and offsetting errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

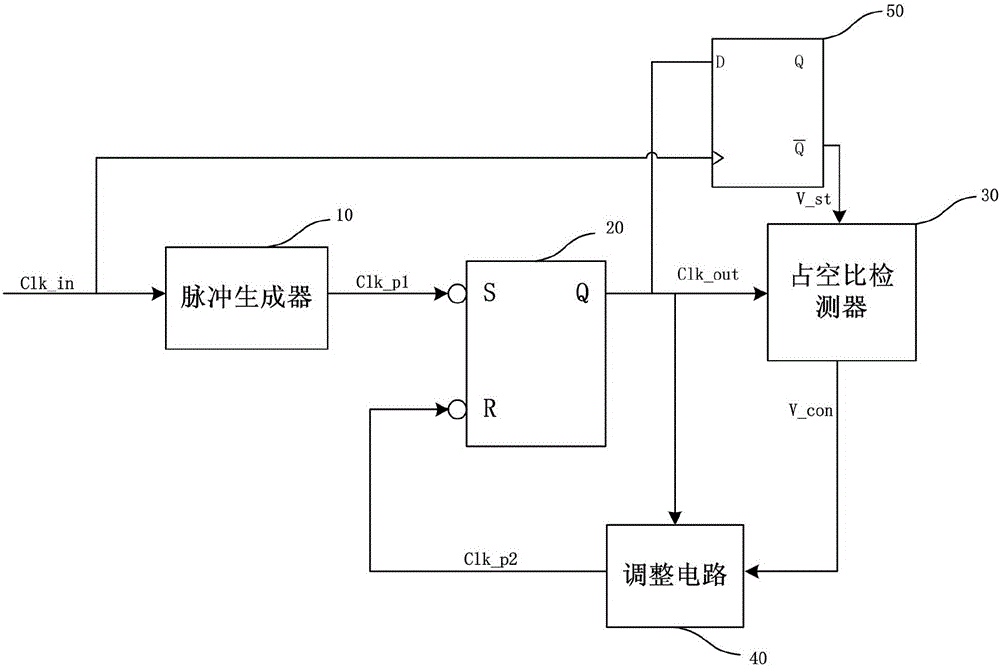

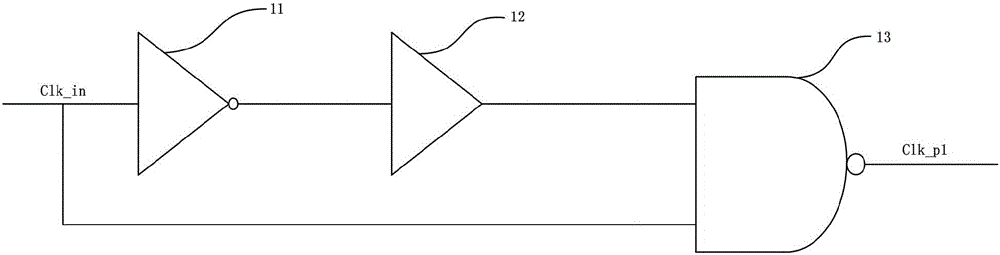

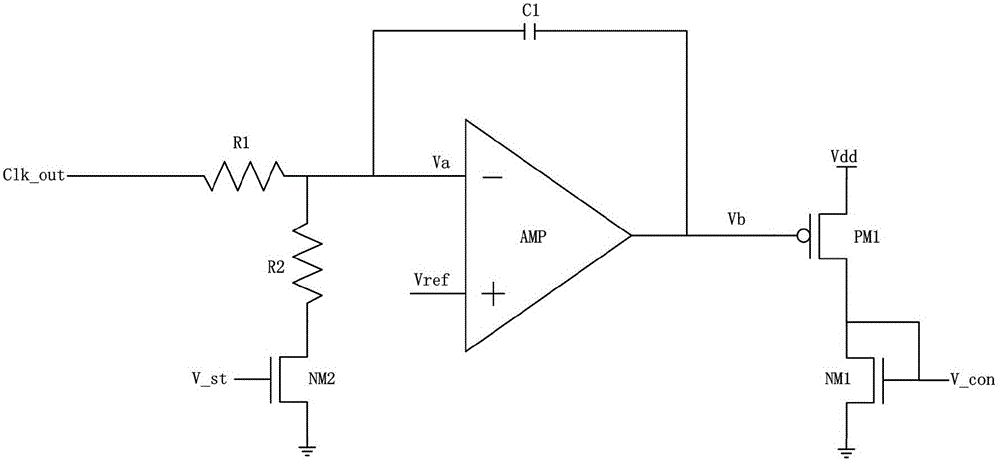

[0017] Such as Figure 1 to Figure 5 As shown, a clock duty ratio adjustment circuit according to the present invention includes a pulse generator 10 , an RS flip-flop 20 , a duty ratio detector 30 , an adjustment circuit 40 and a D flip-flop 50 . The pulse generator 10, the RS flip-flop 20 and the adjustment circuit 40 are connected in sequence. The output terminal of the pulse generator 10 is connected with the S input terminal of the RS flip-flop 20 . The output terminals of the RS flip-flop 20 are respectively connected with the input terminals of the D flip-flop 50 , the duty ratio detector 30 and the adjustment circuit 40 . The inverting output terminal of the D flip-flop 50 is connected with the input terminal of the duty cycle detector 30 . The output terminal of the duty ratio detector 30 is connected with the input terminal of the adjustment circuit 40 . The output terminal of the adjustment circuit 40 is connected with the R input terminal of the RS flip-flop 20 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More