Logic locking achieving device and method for multi-channel ultrasonic front-end chip

An implementation method and multi-channel technology, applied in the field of multi-channel ultrasound chip circuit and its function improvement, can solve problems such as the occupation of logic resources and PLL resources, it is difficult to find design deviations, and PCB wiring differences, etc., to improve the compilation. Performance, effects of optimizing timing constraint settings

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Preferred embodiments of the present invention are described in detail below.

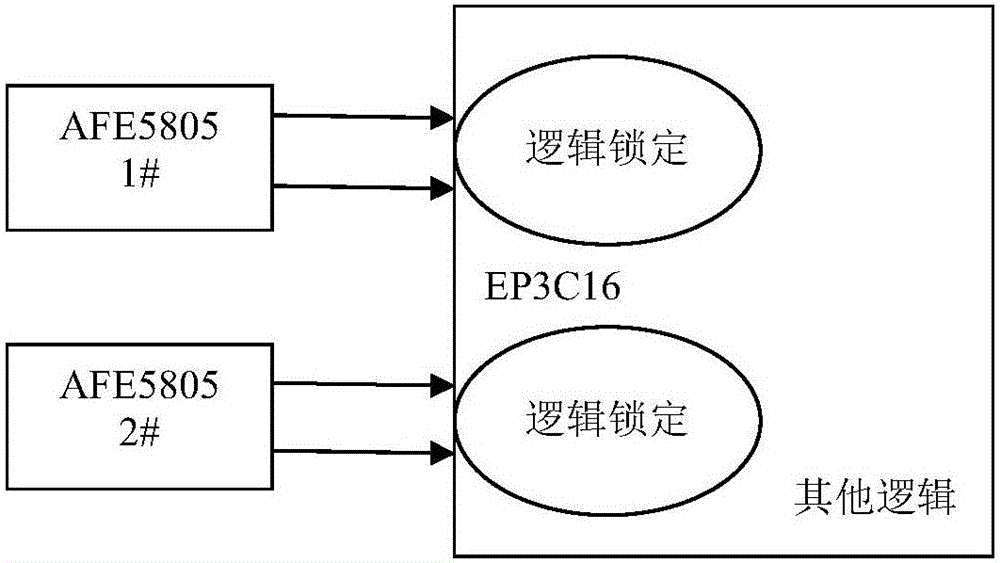

[0031] The device and method for implementing logic locking of a multi-channel ultrasonic front-end chip provided by the present invention are mainly aimed at improving the chip circuit in the multi-channel ultrasonic equipment. The front-end chip of ultrasonic simulation is mainly the AFE5805 chip of TI Company, and this front-end chip is connected with a programmable logic unit with a logic locking function, and the common one is FPGA, such as but not limited to the compiler Quartus10.1 of ALTERA Company, the present invention The low-voltage differential signal pins of the front-end chip must be directly connected to the logic lock pins of the programmable logic unit.

[0032] The differential clock bit_CLK of each front-end chip AFE5805 of the present invention is connected with the dedicated global clock of the FPGA, that is, the high-speed dedicated clock pin; the FPGA compiler is used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More