Double-layer wear-leveling method and system

A wear leveling, two-layer technology, applied in memory systems, memory address/allocation/relocation, instruments, etc., can solve problems such as ineffective defense against malicious attack programs

- Summary

- Abstract

- Description

- Claims

- Application Information

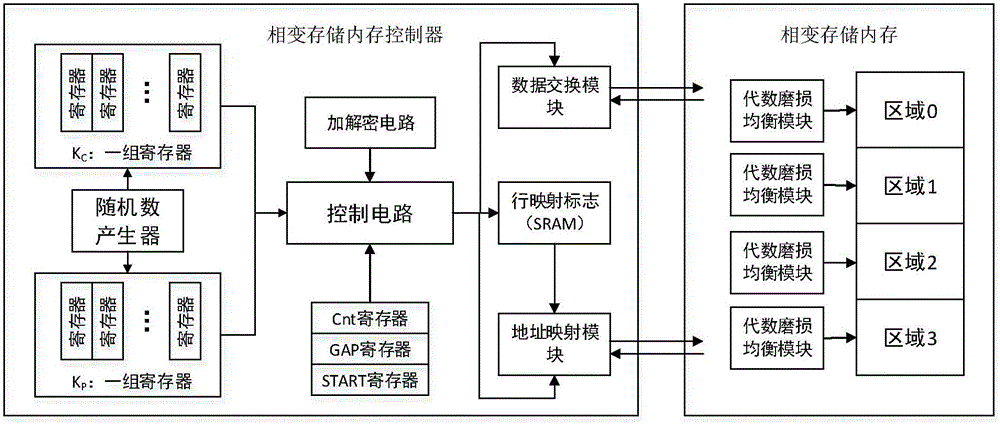

AI Technical Summary

Problems solved by technology

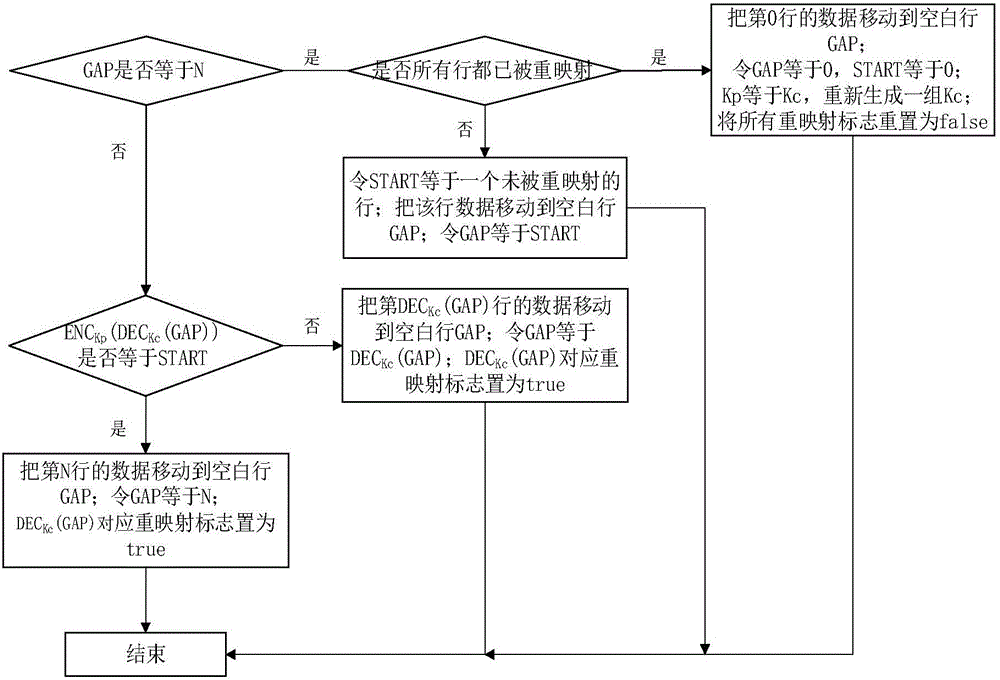

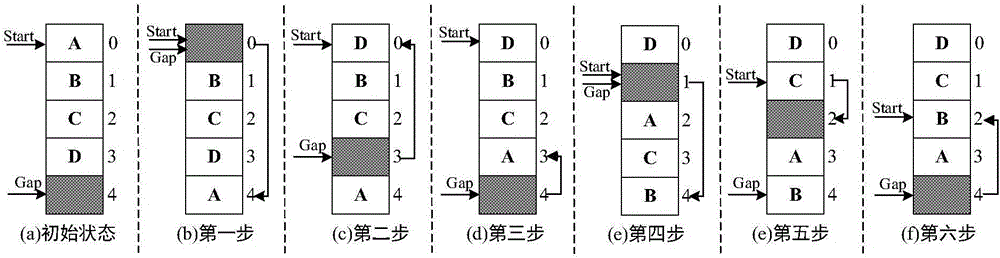

Method used

Image

Examples

Embodiment Construction

[0083] In order to facilitate understanding of the present invention, at first the following nouns appearing in the present invention are explained:

[0084] Physical row: The most basic access unit of the memory system. On different systems, the row size can be different. Usually a row size can be 64 bytes, 128 bytes, 256 bytes;

[0085] Region: A storage area in the memory space, consisting of several physical rows. Usually a region can consist of 2048, 4096 and 8192 rows;

[0086]Logical row address: the address requested by the upper layer application, which is a virtual address, recorded as LA

[0087] Middle row address: the address corresponding to the logical address after being mapped by the upper layer, which is a virtual address and is denoted as IA.

[0088] Physical row address: the address corresponding to the physical device, it is a real address, recorded as PA;

[0089] Remapping: Change the correspondence between logical row addresses and physical row ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More