Passivation layer etching method, manufacture method of pad and manufacture method of semiconductor device

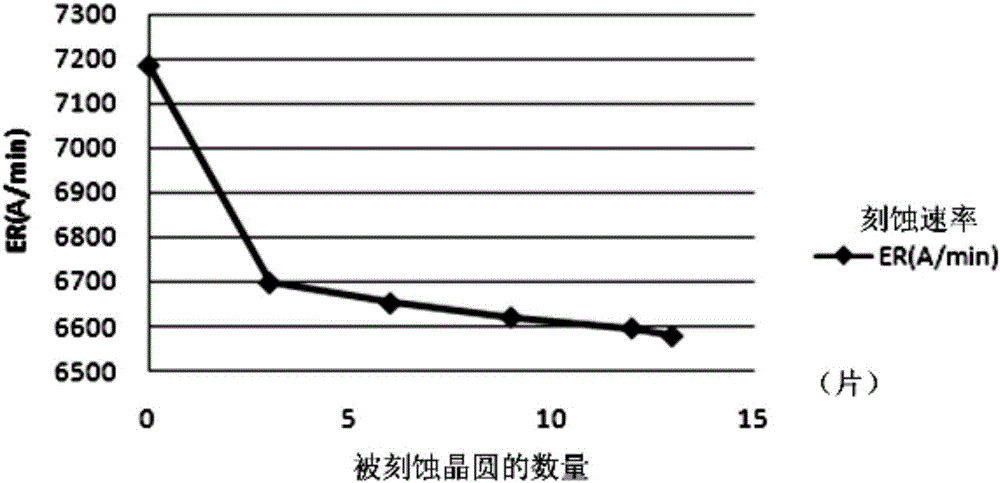

A passivation layer, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as the decline of etching rate, and achieve the effect of ensuring etching effect, solving the effect of reducing etching rate and ensuring performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

[0035] Please refer to image 3 , the invention provides a passivation layer etching method, comprising:

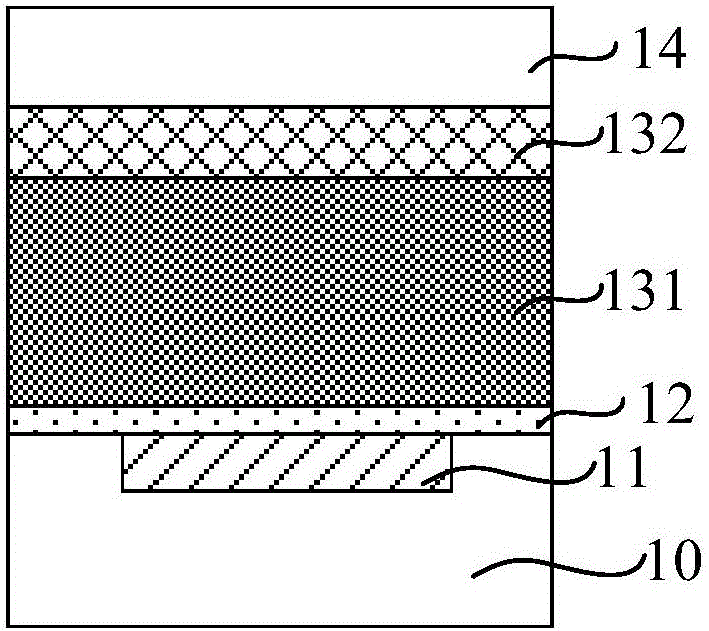

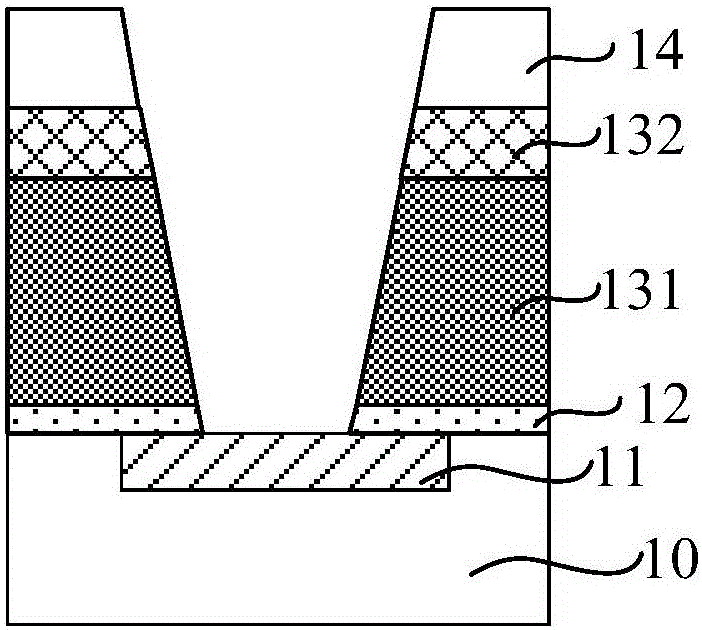

[0036] S1, sequentially forming an etch barrier layer, a first passivation layer and a second passivation layer on a semiconductor substrate with a top metal layer formed on the surface, the material of the first passivation layer and the second passivation layer are different and the thickness is greater than the second passivation layer;

[0037] S2, forming a patterned photoresist layer aligned with the top layer metal on the second passivation layer;

[0038] S3, using the patterned photoresist layer as a m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More