Low-power consumption power-on reset circuit

A technology of electric reset and low power consumption, which is applied in the field of low power power-on reset circuit, can solve the problems of reset signal generation, low power consumption, static power consumption, etc., and achieve the effect of strong anti-interference ability and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

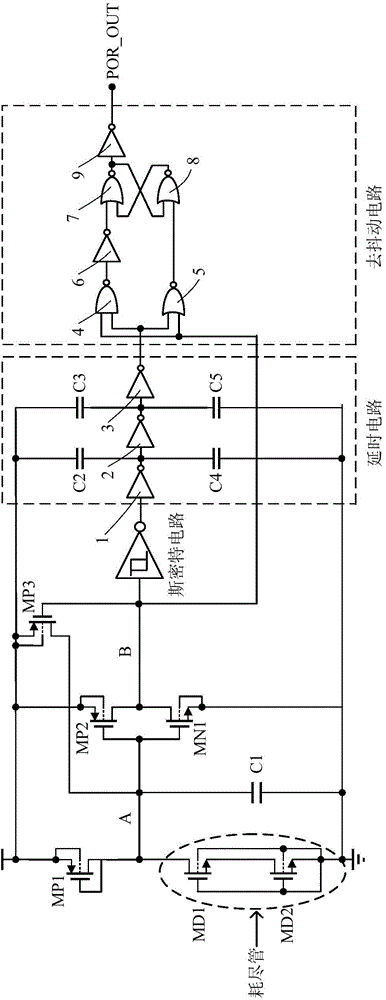

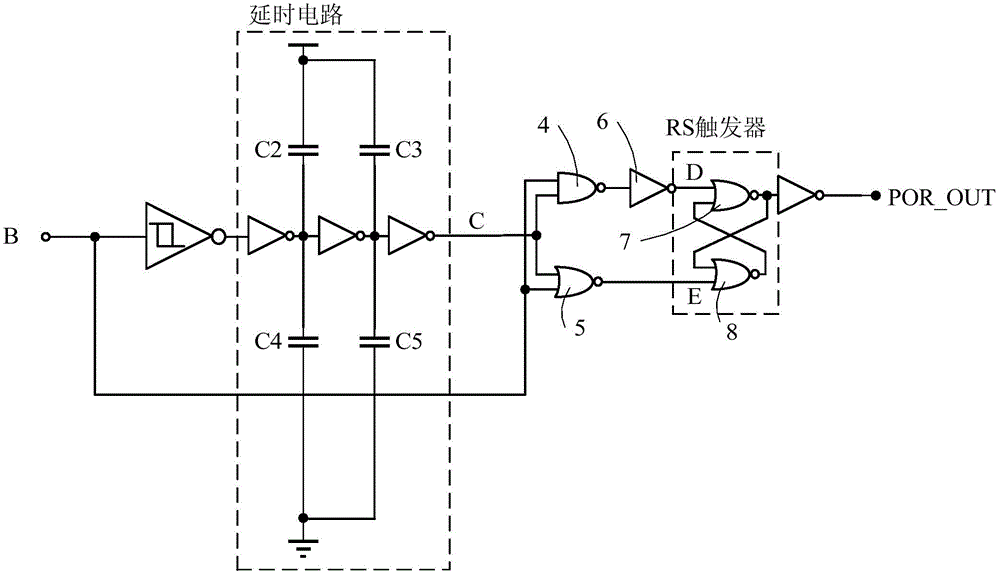

[0026] The structure and working principle of the low-power power-on reset circuit of the present invention will be described in detail below in conjunction with the accompanying drawings. Such as figure 1 As shown, in this embodiment, the power-on reset circuit includes a power-on reset signal generation circuit, a Schmidt circuit, a delay circuit and a debounce circuit that are connected to each other.

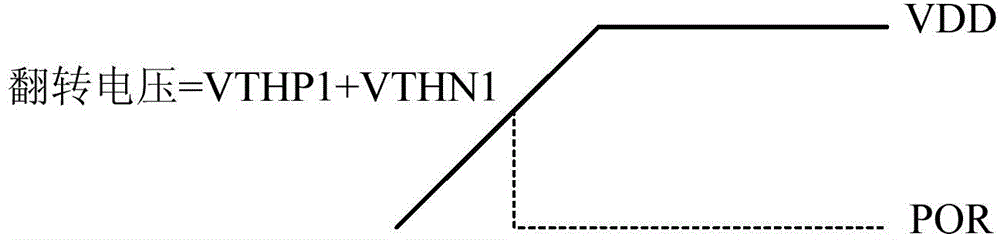

[0027] Specifically, the power-on reset signal generation circuit includes two branches connected in parallel, the first branch includes a first PMOS transistor MP1, its source is connected to the power supply, the gate is short-circuited to the drain, and the drain is connected to the first power consumption The drain of the depletion-type NMOS transistor MD1 is connected, the source of the first depletion-type NMOS transistor MD1 is connected to the drain of the second depletion-type NMOS transistor MD2, and the source of the second depletion-type NMOS transistor MD2 is gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More