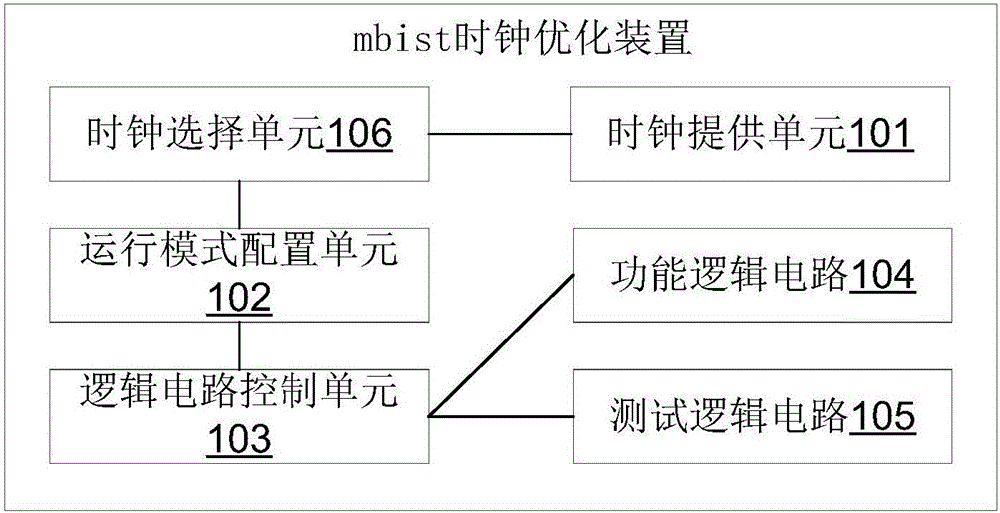

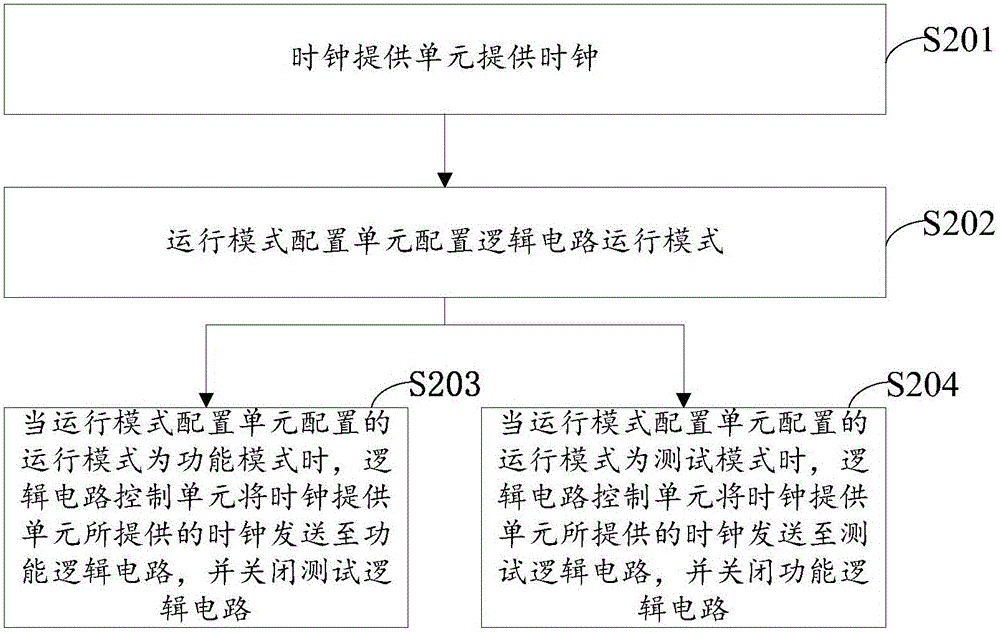

A mbist clock optimization method and device

An optimization device and optimization method technology, which is applied in the detection of faulty computer hardware, function inspection, etc., can solve the problems of insufficient test power supply, high power consumption, and unstable test.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to explain in detail the technical content, structural features, achieved goals and effects of the technical solution, the following will be described in detail in conjunction with specific embodiments and accompanying drawings.

[0034] DVFS (Dynamic Voltage and Frequency Scaling) dynamic voltage and frequency adjustment is a real-time voltage and frequency adjustment technology. Power consumption in CMOS circuits can be mainly divided into dynamic power consumption and static power consumption, the formula is as follows:

[0035] Power=∑(CV 2 αf+VI dq )

[0036] Among them, C represents the capacitance of the load capacitor, V is the operating voltage, α is the flip rate at the current clock frequency, f is the operating frequency, and I_dq represents the quiescent current. The first part of the formula represents the dynamic power consumption, and the latter part represents the static power consumption. It can be seen from the formula that if you want to...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap