fet and method of forming fet

A semiconductor and crystal technology, used in semiconductor devices, electrical components, circuits, etc., to solve problems such as reduced device performance and high leakage current of FinFETs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

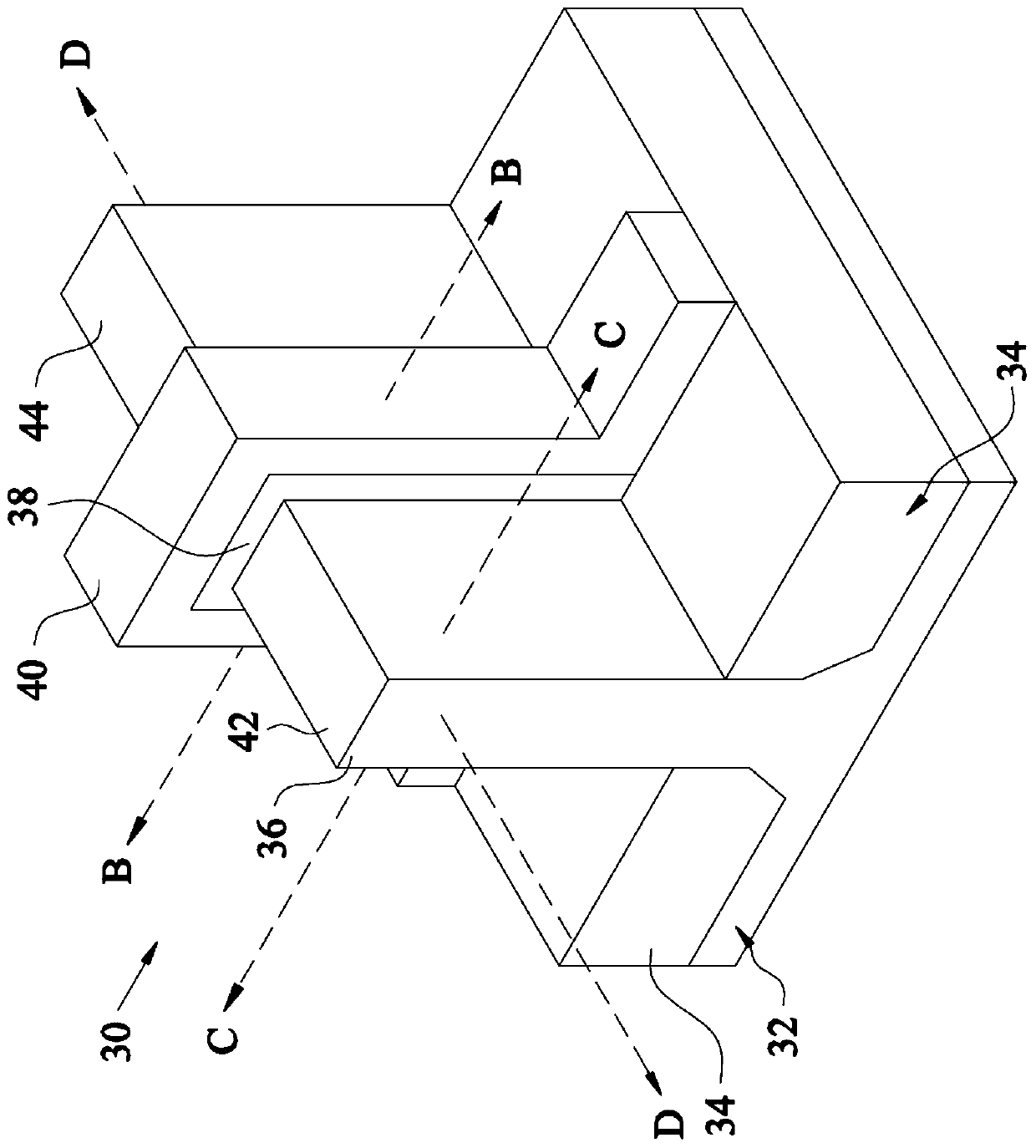

[0070] An embodiment is a method comprising forming a first fin and a second fin on a substrate, the first fin and the second fin each comprising a first crystalline semiconductor material on the substrate and a first fin over the first crystalline semiconductor material The second crystalline semiconductor material. The first crystalline semiconductor material in the second fin is converted to a dielectric material, wherein at least a portion of the first crystalline semiconductor material in the first fin remains untransformed after the converting step. A gate structure is formed over the first fin and the second fin, and source / drain regions are formed on opposite sides of the gate structure.

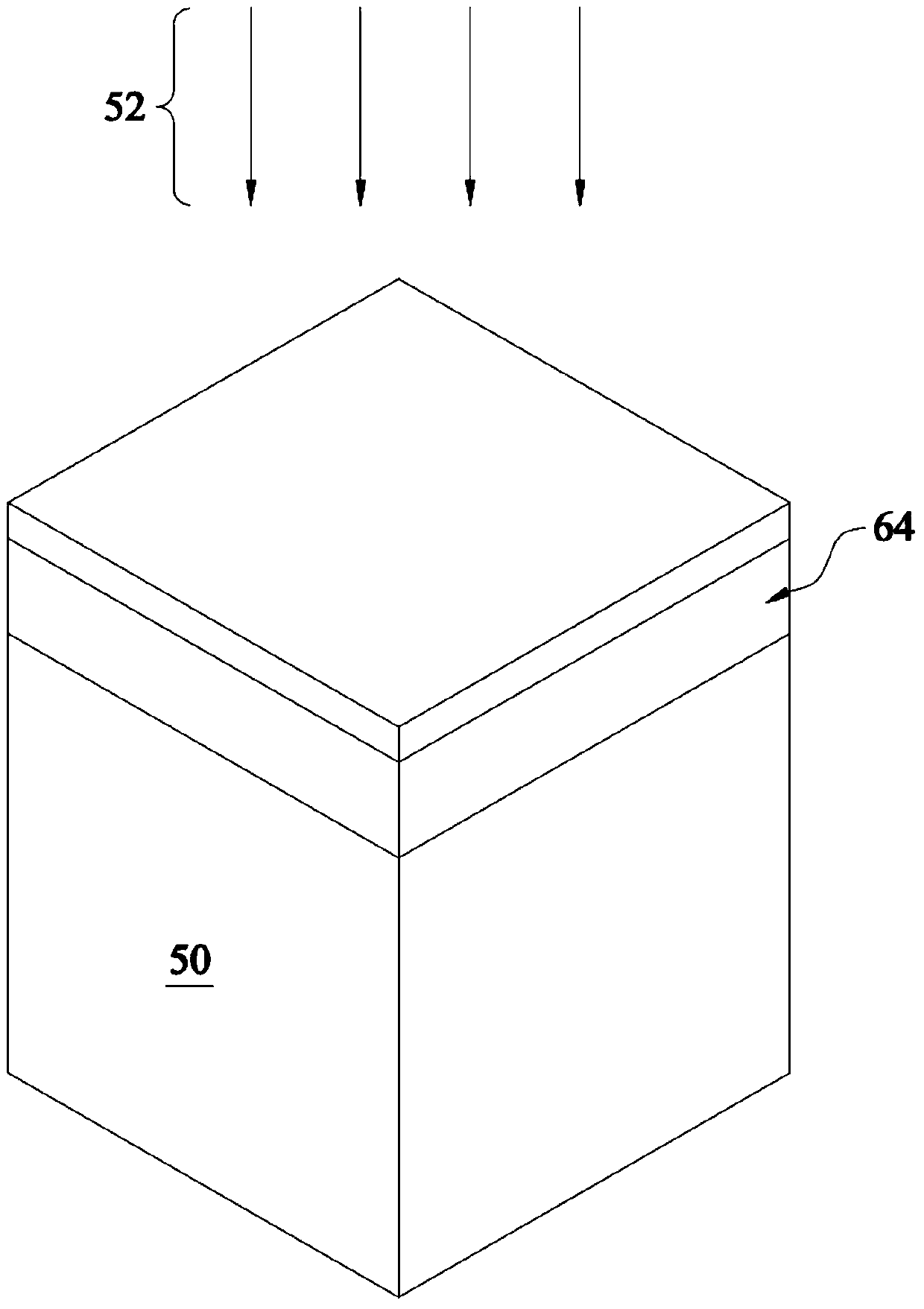

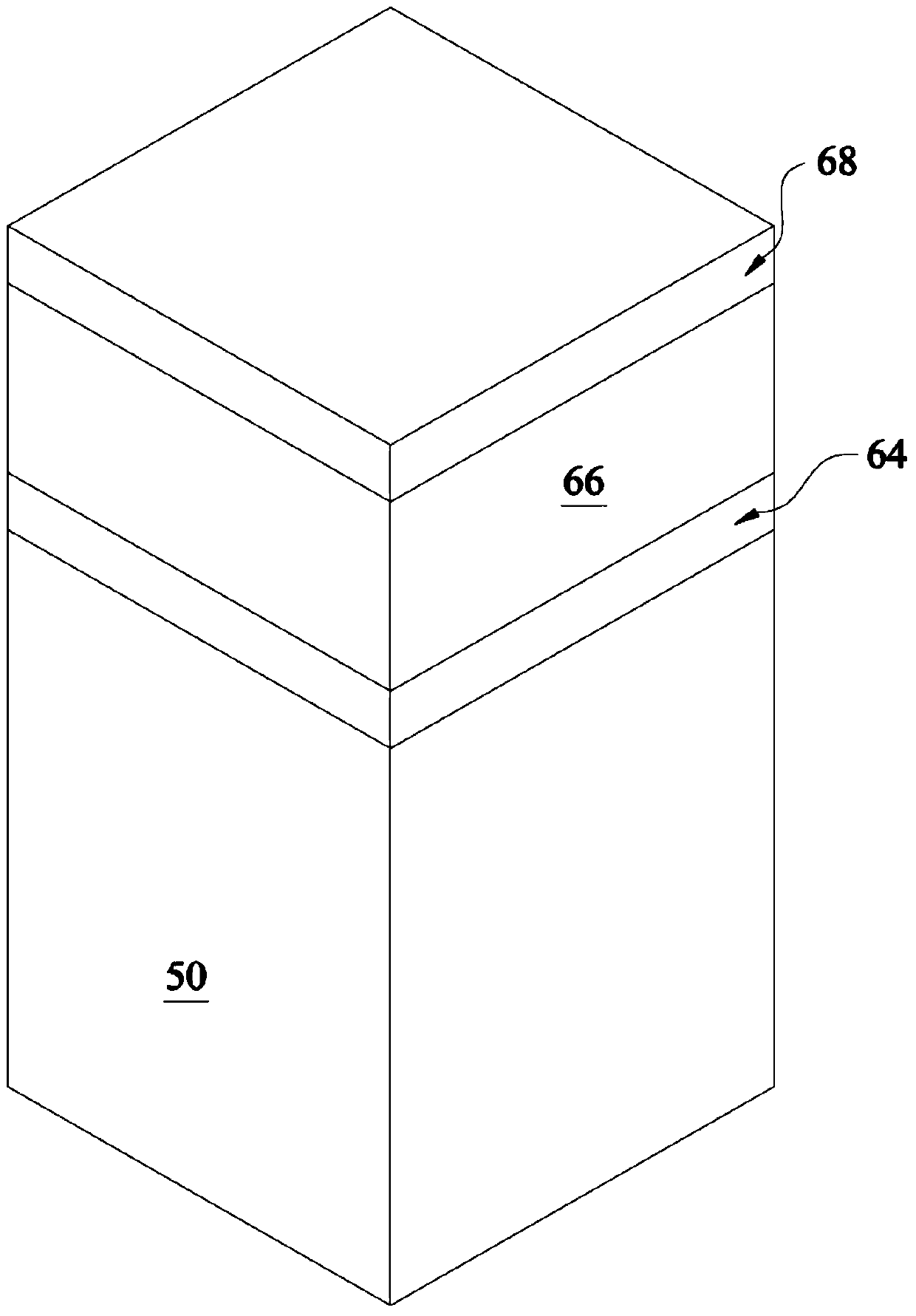

[0071] Another embodiment is a method comprising epitaxially growing a first crystalline semiconductor material on a substrate, epitaxially growing a second crystalline semiconductor material over the first crystalline semiconductor material, and patterning the first crystalline semi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More