A trench-structured vdmos

A trench and inner trench technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of restricting reverse withstand voltage, affecting device dynamic characteristics, source-drain capacitance Cds, etc., and improving reverse blocking voltage. , The effect of low gate-drain capacitance Cds and uniform lateral electric field distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

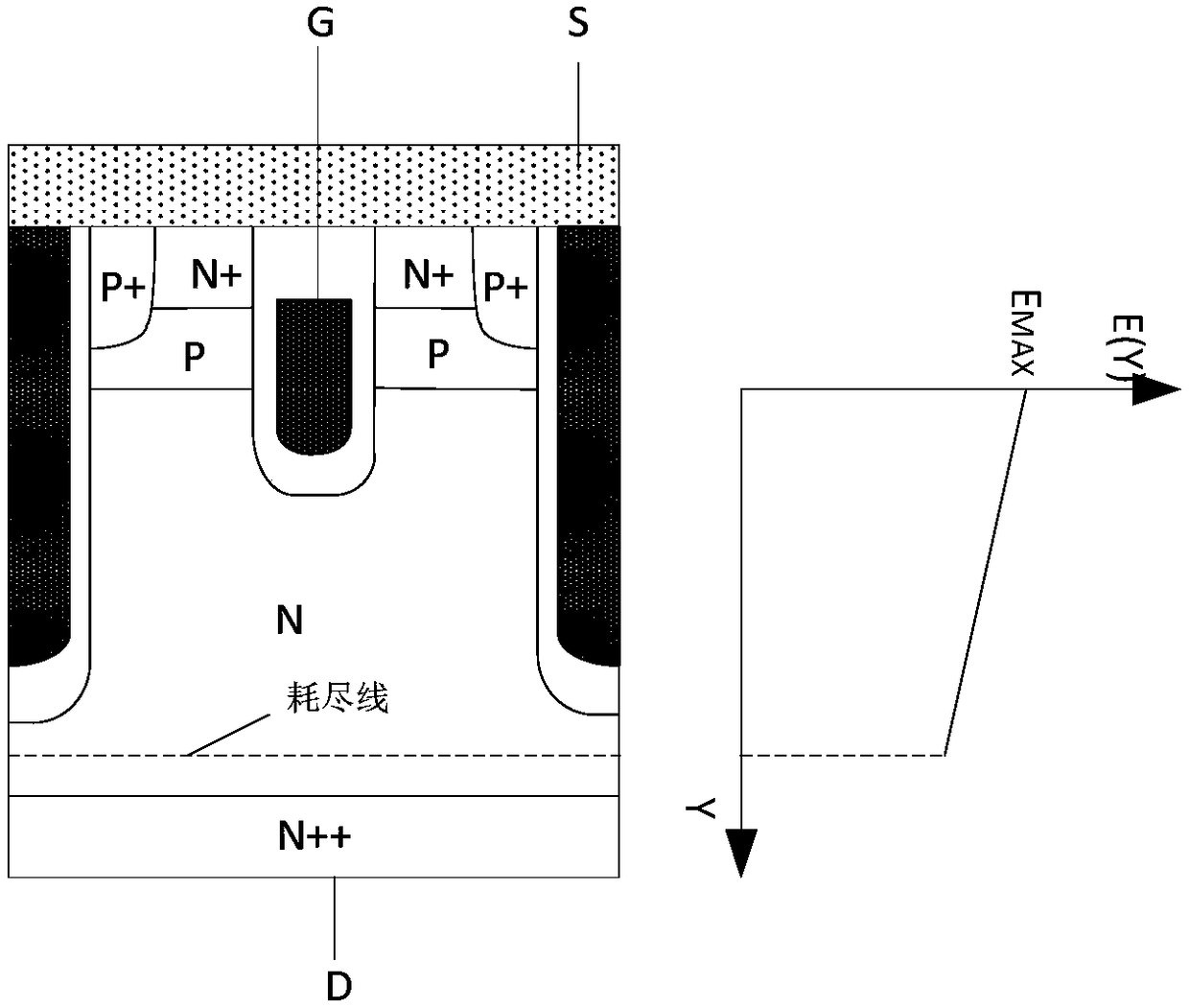

Problems solved by technology

Method used

Image

Examples

Embodiment 1

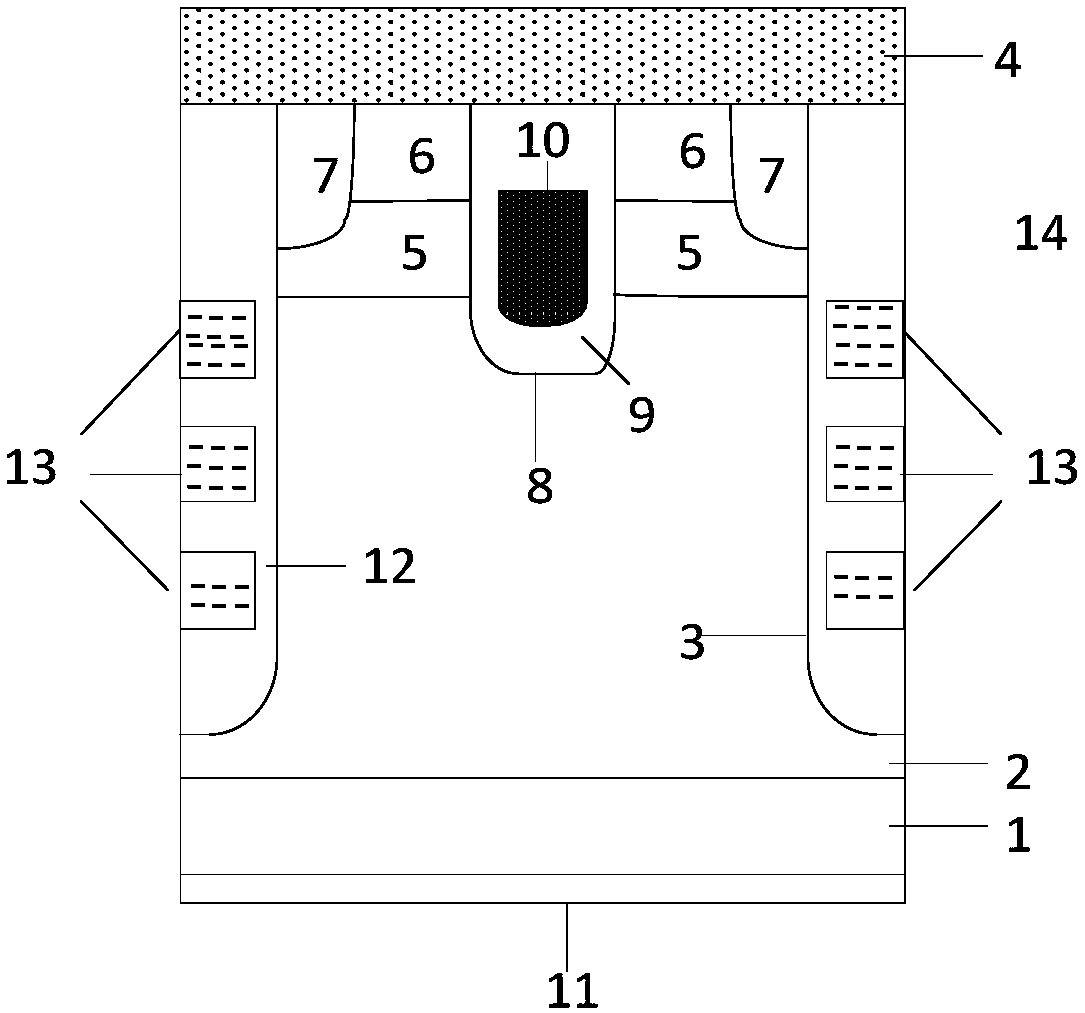

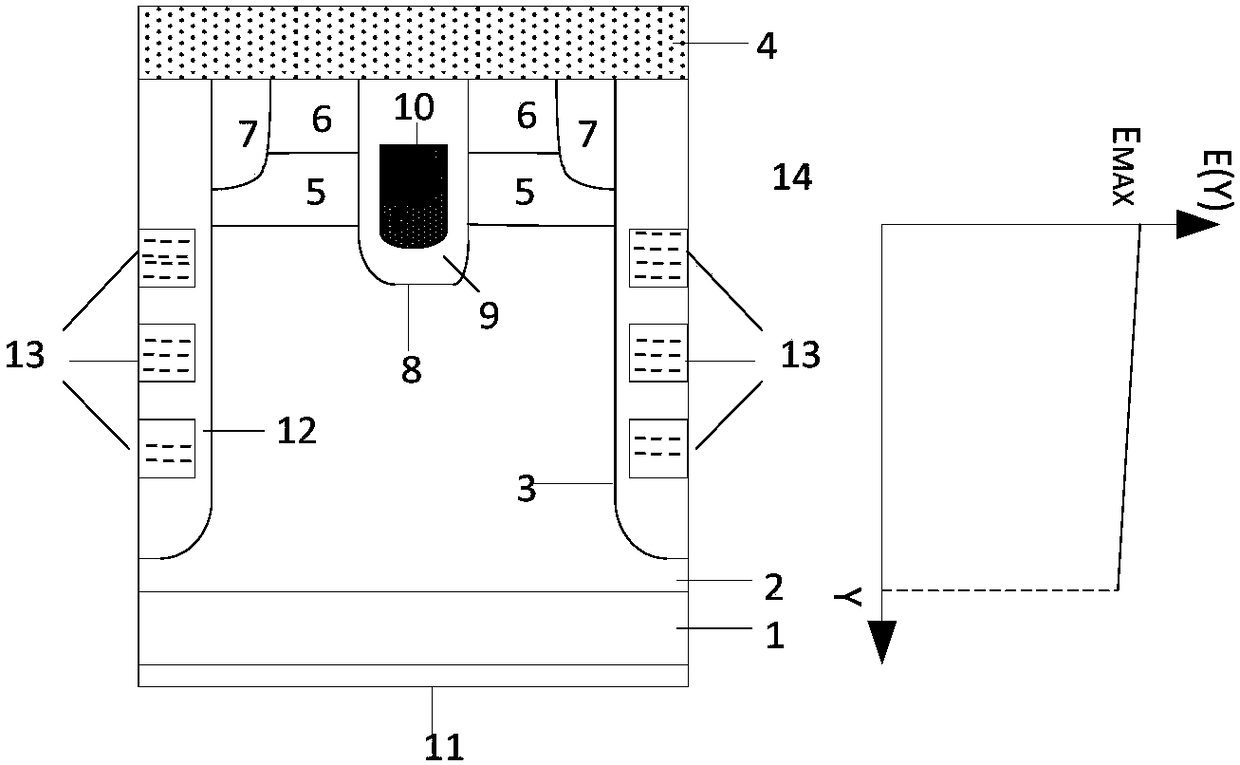

[0016] like image 3 As shown, a VDMOS with a trench structure in this example includes a metallized drain 11, an N+ substrate 1, an N-drift region 2, and a metallized source 4 that are sequentially stacked from bottom to top; Region 2 has internal trenches 3, P-type doped regions 5, N-type heavily doped regions 6, P-type heavily doped regions 7, and trenches 8, and the P-type doped regions 5 are located in the internal trenches on both sides. Between the grooves 3, and the side of the P-type doped region 5 is in contact with the side of the groove 3 in the body; the N-type heavily doped region 6 is located on the upper surface of the P-type doped region 5, and the N-type heavily doped region 6 The upper surface is in contact with the lower surface of the metallized source electrode 4; the P-type heavily doped region 7 is located between the internal trench 3 and the N-type heavily doped region 6 and is located between the internal trench 3 and the N-type heavily doped region ...

Embodiment 2

[0036] The structure of this example is based on Example 1. All N-type materials in Example 1 are replaced with P-type materials, all P-type materials are replaced with N-type materials, and negative charges in the polysilicon 13 are replaced with positive charges.

[0037] When making devices, semiconductor materials such as silicon carbide, gallium arsenide, or silicon germanium can also be used instead of silicon.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More