Fault detection equipment and fault detection method

A fault detection and equipment technology, applied in the direction of digital circuit testing, electronic circuit testing, etc., can solve problems such as the complexity of the fault detection process of digital processing modules, and achieve the effects of simplifying complexity, simplifying the operation process, and solving complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

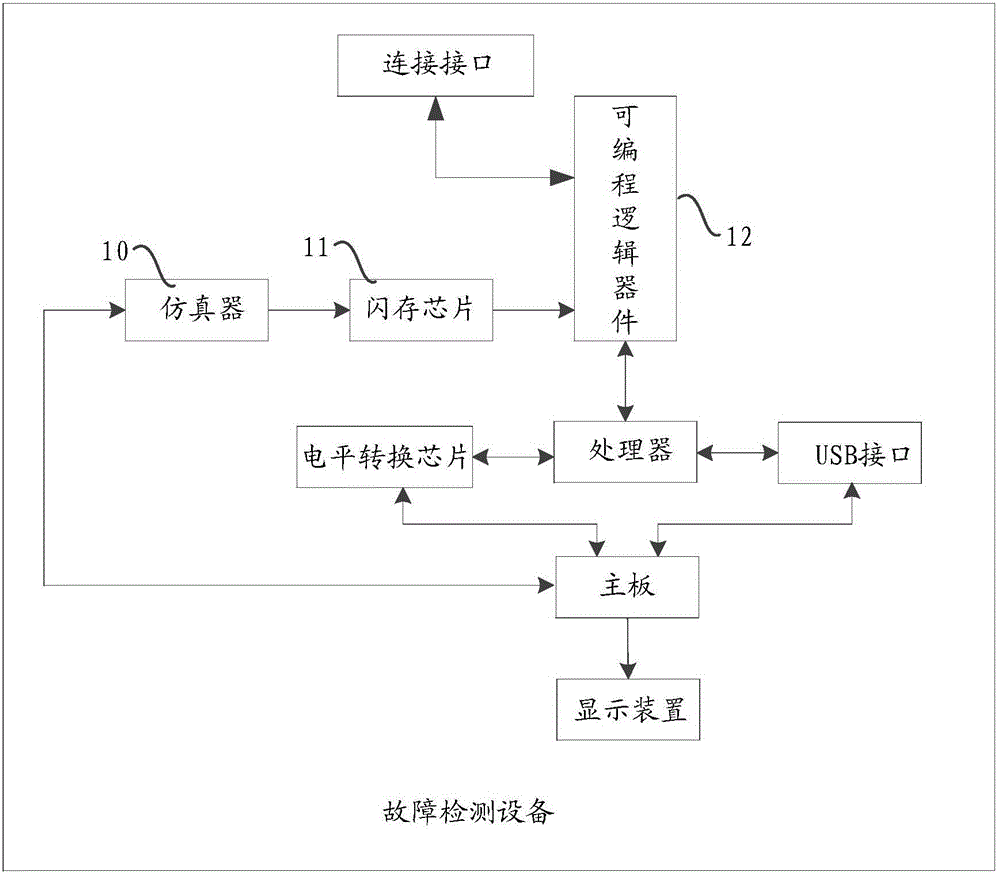

[0057] Please refer to figure 1 , Embodiment 1 of the present application provides a fault detection device, including:

[0058] Emulator 10, for downloading the first test program;

[0059] A flash memory chip 11, connected to the emulator 10, for storing the first test program;

[0060] A programmable logic device 12 is connected to the flash memory chip 11;

[0061] Wherein, when the fault detection device is connected with a digital processing device, the fault detection device reads and runs the first test program from the flash memory chip through the programmable logic device to determine the digital Whether the processing device is faulty.

[0062] In the embodiment of the present application, the emulator is connected between the motherboard and the flash memory chip, and the emulator may specifically be a BMD emulator or a JTAG emulator. In the specific implementation process, if the emulator takes a JTAG emulator as an example, the JTAG emulator and the motherbo...

Embodiment 2

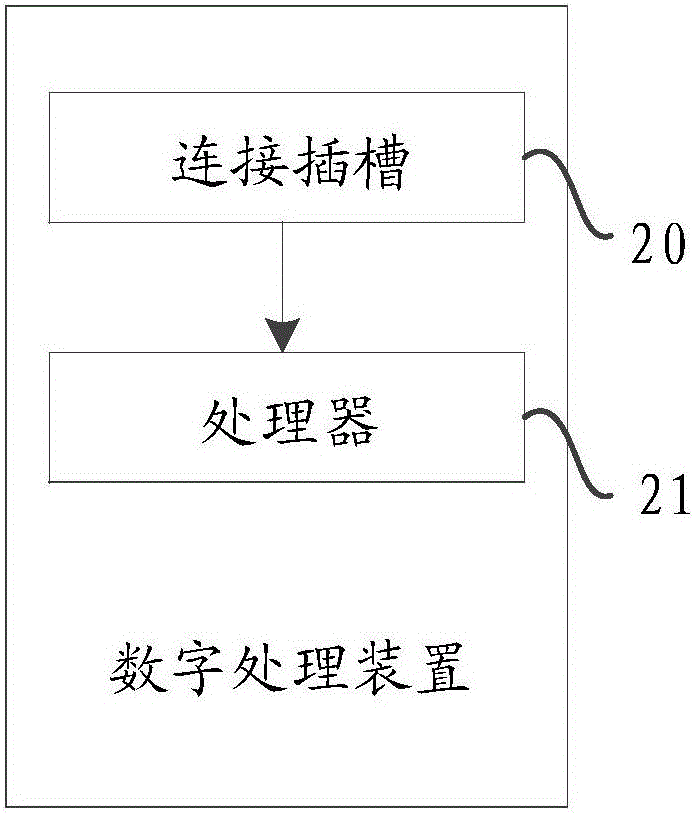

[0117] Please refer to figure 2 , a digital processing device is provided in an embodiment of the present application, including:

[0118] Connection slot 20 for connecting with fault detection equipment;

[0119] Processor 21, connected to the connection slot;

[0120] Wherein, when the digital processing device is connected to the fault detection device through the connection slot, download and run the first test program, and sequentially control each input / output port on the connection interface corresponding to the connection slot The level value of the switch jumps according to the preset time interval.

[0121] In the embodiment of the present application, the digital processing device is specifically a processing device including an FPGA chip, a DSP processor, and a power supply chip, and in the embodiment of the present application, the chips in the digital processing device, such as: FPGA and DSP are packaged by BGA way of encapsulation.

[0122] Further, the dig...

Embodiment 3

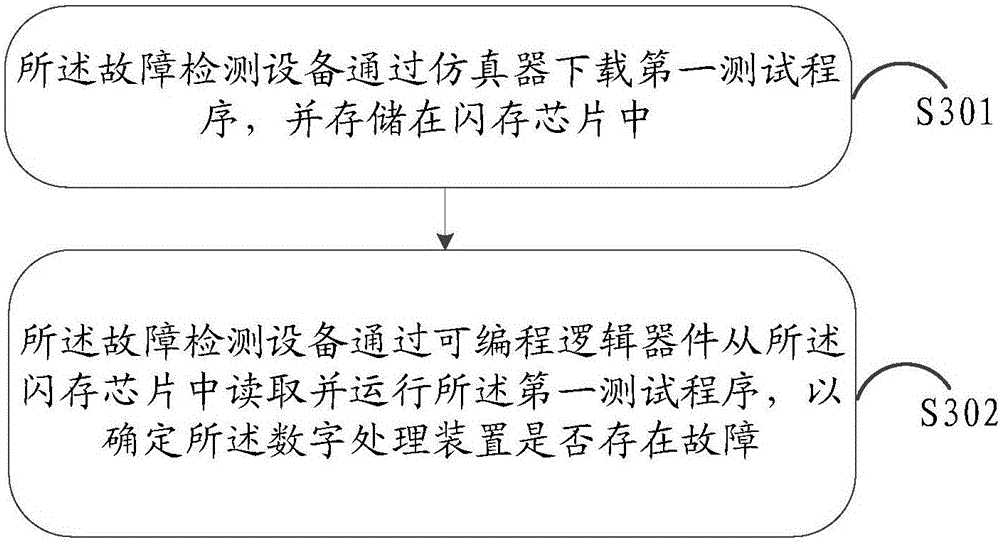

[0127] Please refer to image 3 , the embodiment of the present application provides a fault detection method applied to fault detection equipment, when the fault detection equipment is connected to a digital processing device, the method includes:

[0128] S301: The fault detection device downloads the first test program through the emulator, and stores it in the flash memory chip;

[0129] S302: The fault detection device reads and runs the first test program from the flash memory chip through a programmable logic device, acquires the pin working status of the pins of the digital processing device, and uses the The working status determines whether the digital processing device is faulty.

[0130] In the embodiment of the present application, step S301 is first performed: the fault detection device downloads the first test program through an emulator, and stores it in a flash memory chip.

[0131] In the embodiment of the present application, the emulator may specifically ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More