Semiconductor preparation method

A semiconductor and dielectric layer technology, applied in the field of semiconductor preparation, can solve problems such as poor wafer edge etching, film drop, and semiconductor device defects, and achieve the effect of being beneficial to protection, avoiding defects, and improving reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

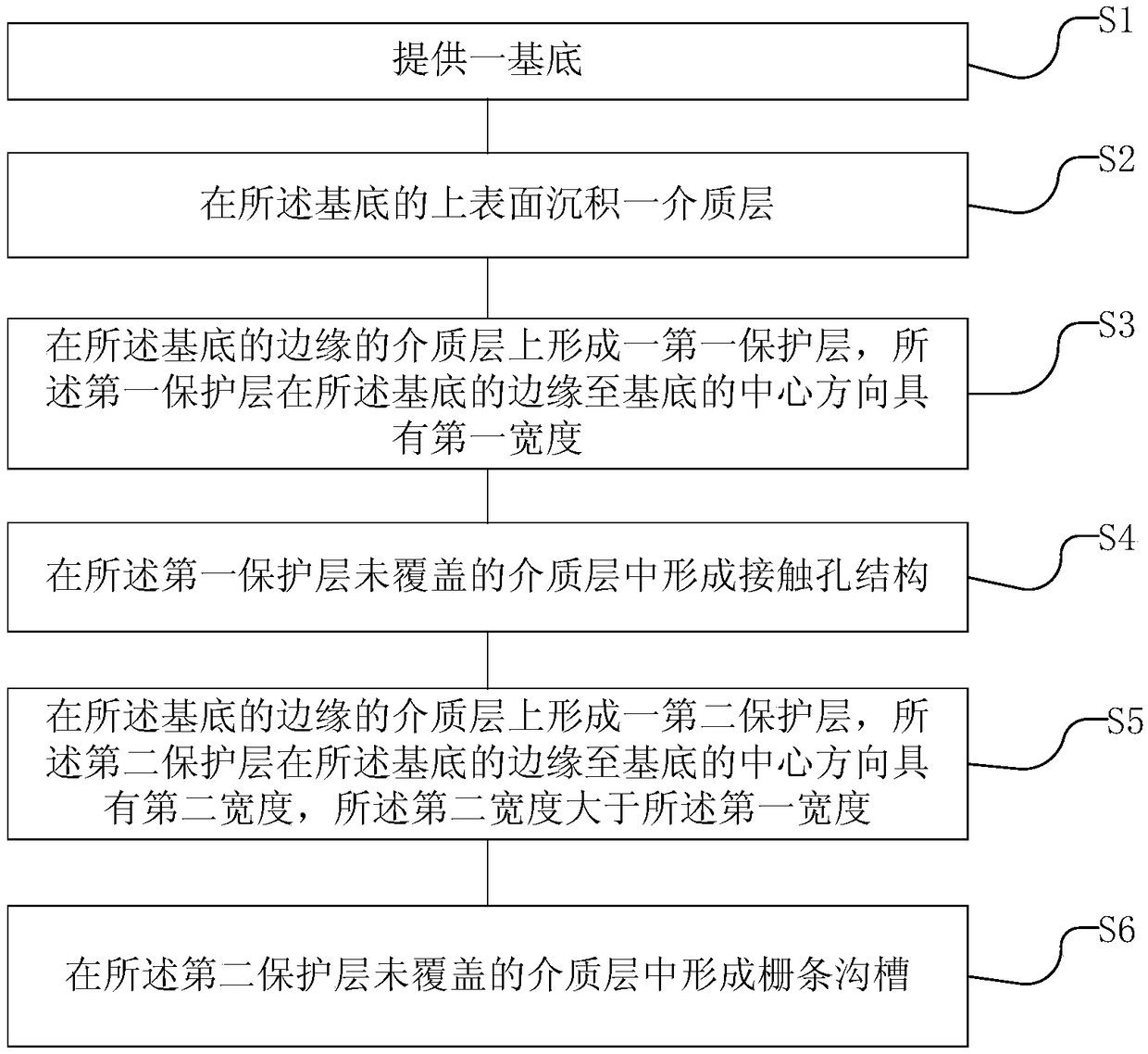

[0039] The core idea of the present invention is that the present invention provides a semiconductor preparation method, the semiconductor preparation method comprising:

[0040] Step S1: providing a substrate;

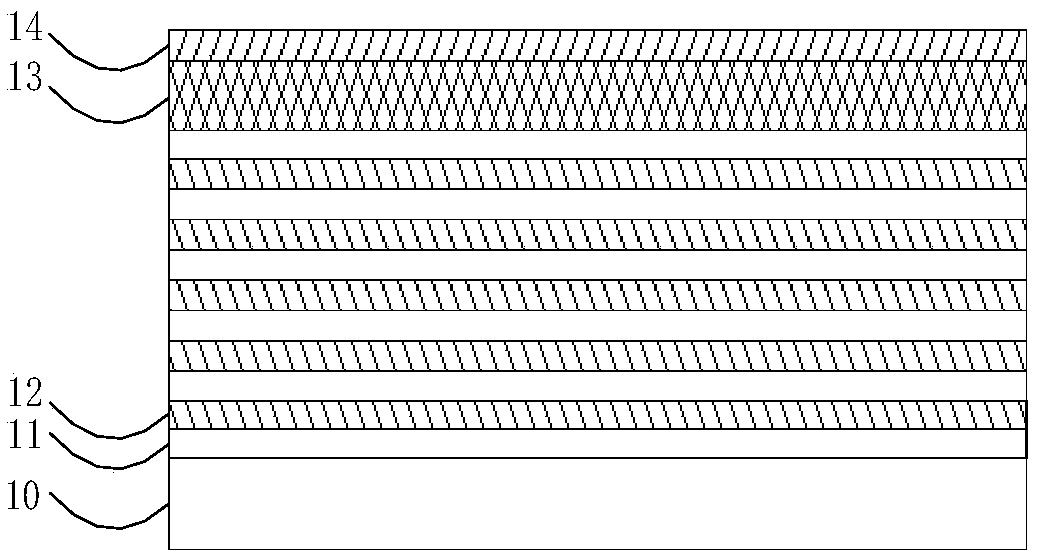

[0041] Step S2: depositing a dielectric layer on the upper surface of the substrate;

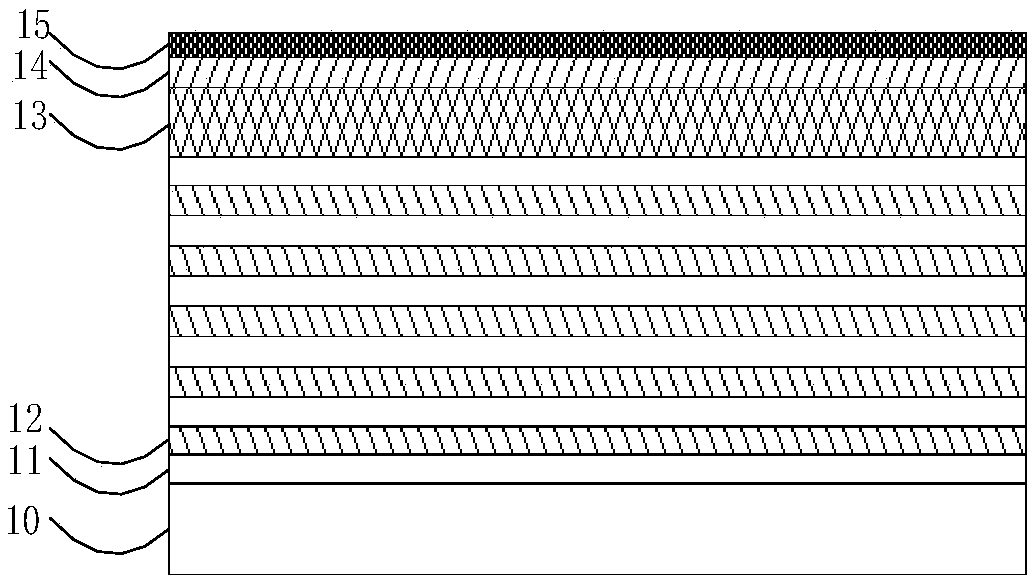

[0042] Step S3: forming a first protective layer on the dielectric layer at the edge of the substrate, the first protective layer has a first width from the edge of the substrate to the center of the substrate;

[0043] Step S4: forming a contact hole structure in the dielectric layer not covered by the first protective layer;

[0044] Step S5: forming a second protective layer on the dielectric layer at the edge of the substrate, the second protective layer has a second width from the edge of the substrate to the center of the substrate, and the second width is larger than the first width;

[0045] Step S6: forming grid grooves in the dielectric layer not covered by the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More