Resistive random access memory and preparation method thereof

A resistive variable memory and resistive variable technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems of reducing the stability and reliability of resistive variable memory, increase the probability of conductive channels, improve Uniformity and the effect of improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

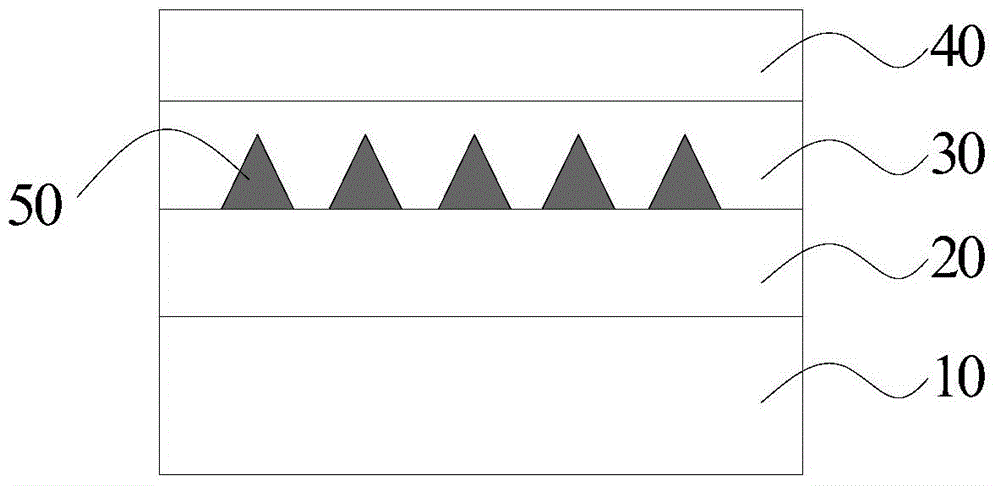

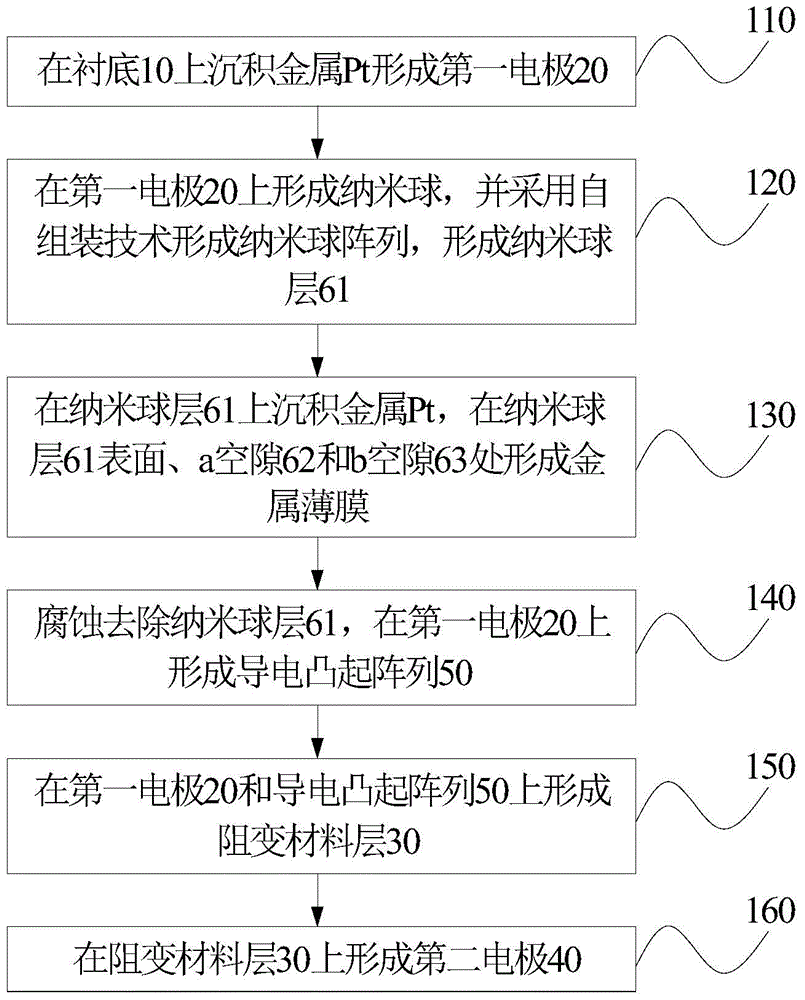

[0028] figure 1 is a schematic structural diagram of a resistive variable memory according to Embodiment 1 of the present invention.

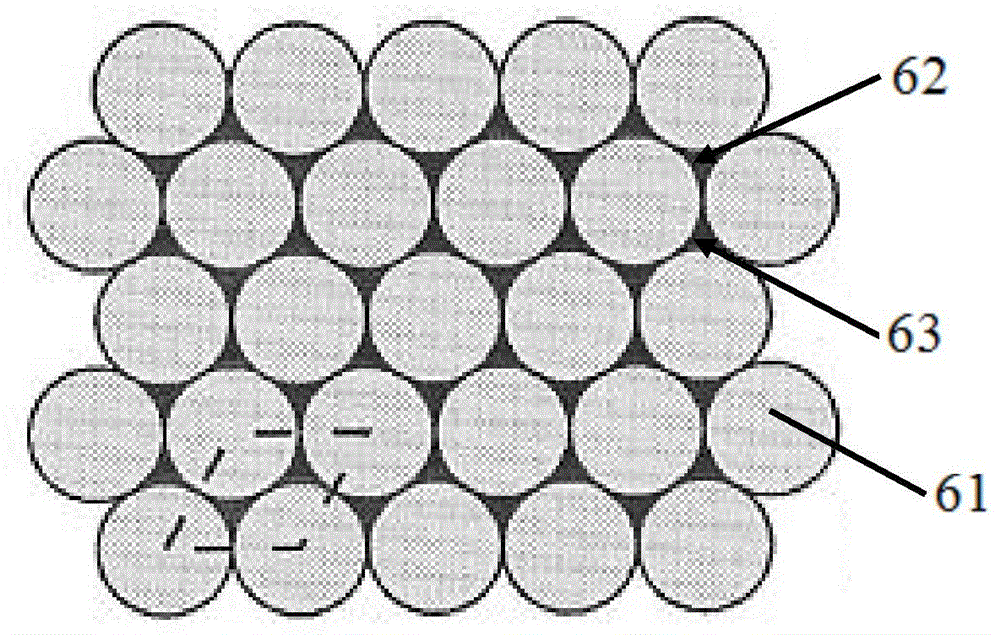

[0029] refer to figure 1 , The resistive variable memory according to Embodiment 1 of the present invention includes a substrate 10; a first electrode 20, a resistive material layer 30, and a second electrode 40 sequentially stacked on the substrate 10; and, arranged on the first electrode The conductive protrusion array 50 formed on the surface of the first electrode 20 is spaced between the resistive material layer 30 and the resistive material layer 20 .

[0030] In this embodiment, the material of the above-mentioned conductive bump array 50 is Pt, and the height of the conductive bump array is about 5nm, and the pitch is 50nm; but the present invention is not limited thereto, the material of the conductive bump array can also be selected Any one of Cu, Al, Ti, Ni, Au, and the height of the conductive bump array is limited to 1nm-5nm, and...

Embodiment 2

[0050] In the description of Embodiment 2, the similarities with Embodiment 1 will not be repeated here, and only the differences with Embodiment 1 will be described. The difference between embodiment 2 and embodiment 1 is that, referring to Figure 5 , the resistive variable memory according to Embodiment 2 of the present invention includes a substrate 10; a first electrode 20, a resistive material layer 30, and a second electrode 40 sequentially stacked on the substrate 10; and, arranged on the second electrode 40 and the resistance-switching material layer 30 and spaced apart from the conductive bump array 50 formed on the surface of the resistance-switching material layer 30 .

[0051] refer to Figure 6 A flow chart of the steps of the method for manufacturing the resistive variable memory according to Embodiment 2 of the present invention.

[0052] In step 210 , metal Pt is deposited on the substrate 10 to form the first electrode 20 , and the resistive material layer ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Height | aaaaa | aaaaa |

| Spacing | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More