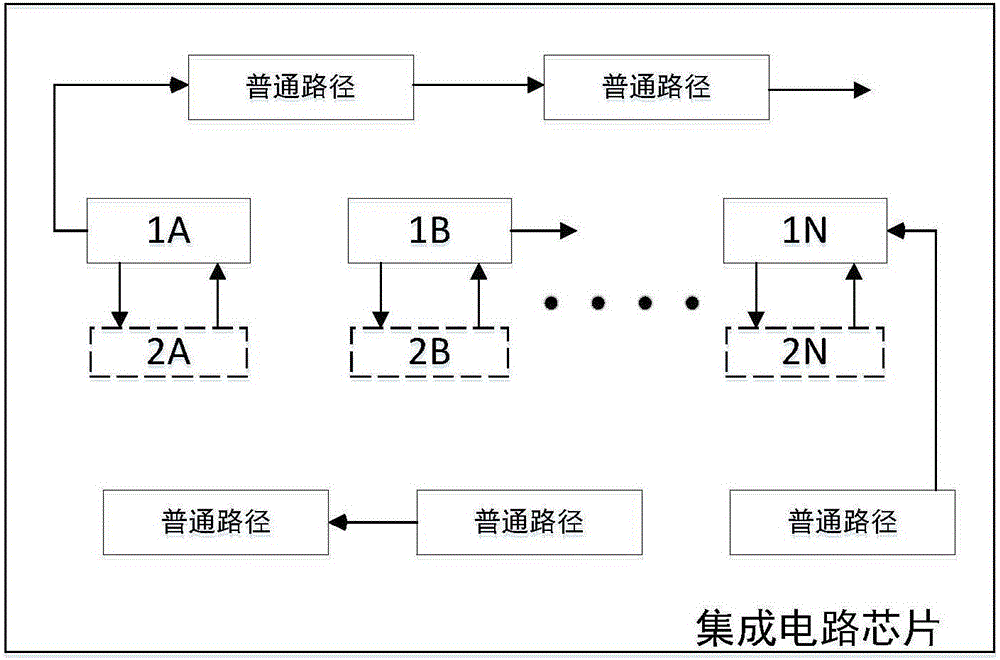

Speed grading optimization structure and method capable of improving yield of high-performance integrated circuit

A speed classification, integrated circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of inconsistent maximum operating speed of integrated circuits, and achieve the effect of increasing profits, increasing overall profits, and increasing proportions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0100] Apply the internal speed classification optimization structure of the integrated circuit chip designed by the present invention to test:

[0101] The internal speed classification optimization structure of the integrated circuit chip proposed by the present invention has been inserted into several test circuits, such as the FGU (Floating Point and Graphic Unit, floating-point calculation and image processing module) module in the OpenSPARCT2 processor, in ITC'99 The largest circuit b19, and s953, s9234, s13207, s38417, and s35932 of the ISCAS'89 test circuits. The above-mentioned circuits inserted into the on-chip regulation structure have been verified by simulation, and verified on Altera's 28nm FPGA.

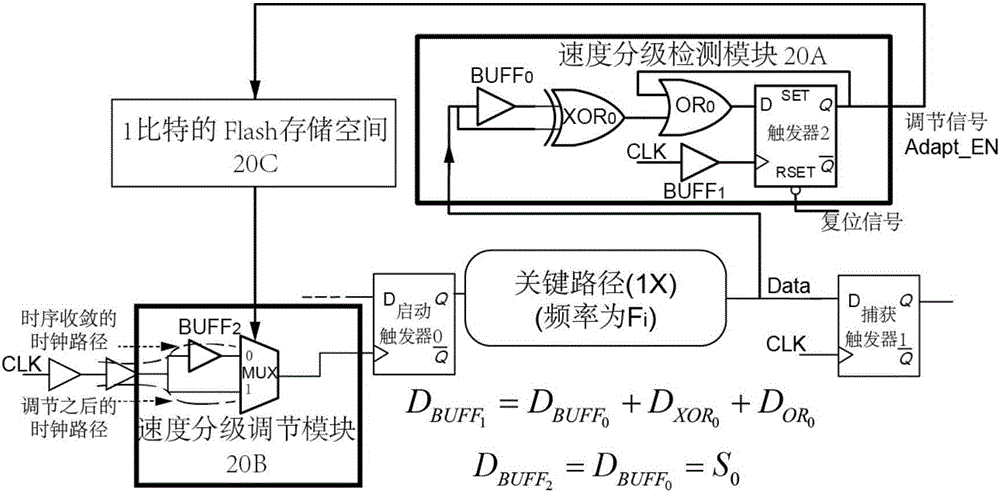

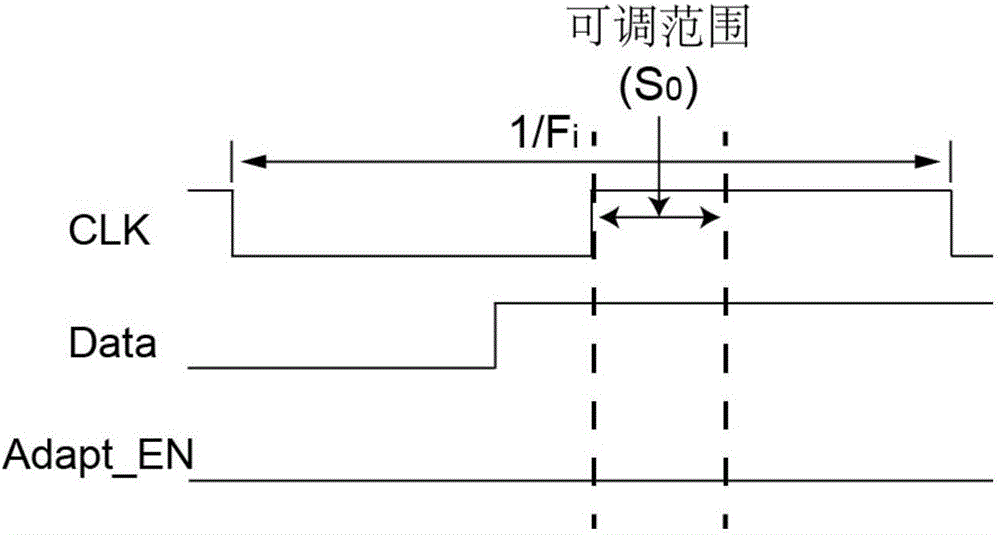

[0102] Firstly, the hierarchical optimization structure of single path speed is tested. A path is extracted in the b19 circuit, and the delay of this path is 851ps. The extraction method is as follows: first, use the Design Compiler software of Synopsys to synthesize...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More