Method for forming MIS structure

A technology of MIS structure and silicon substrate, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of high deposition cost and slow deposition speed of ALD film

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

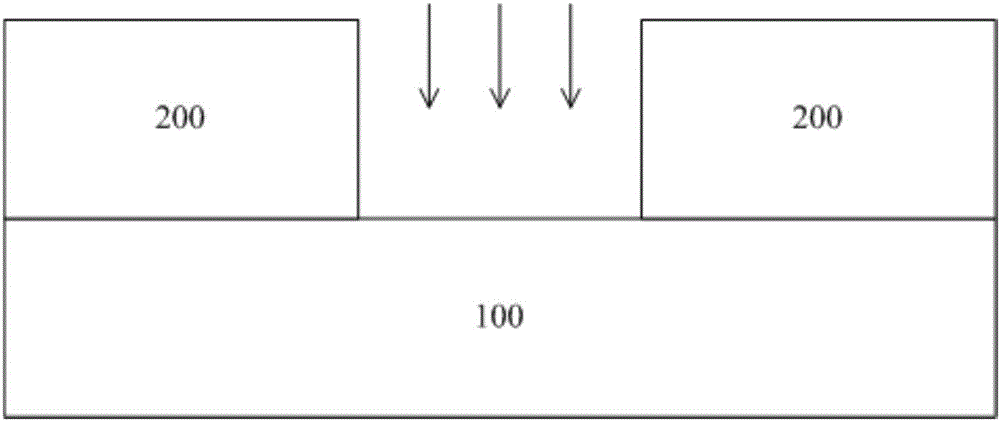

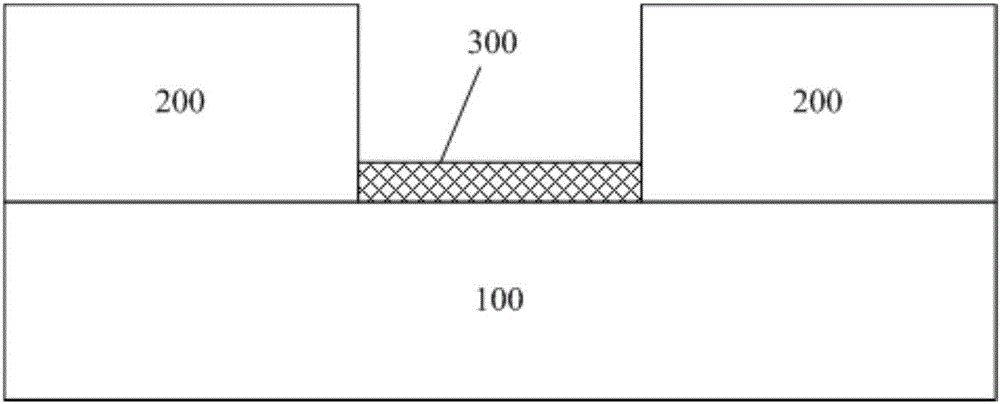

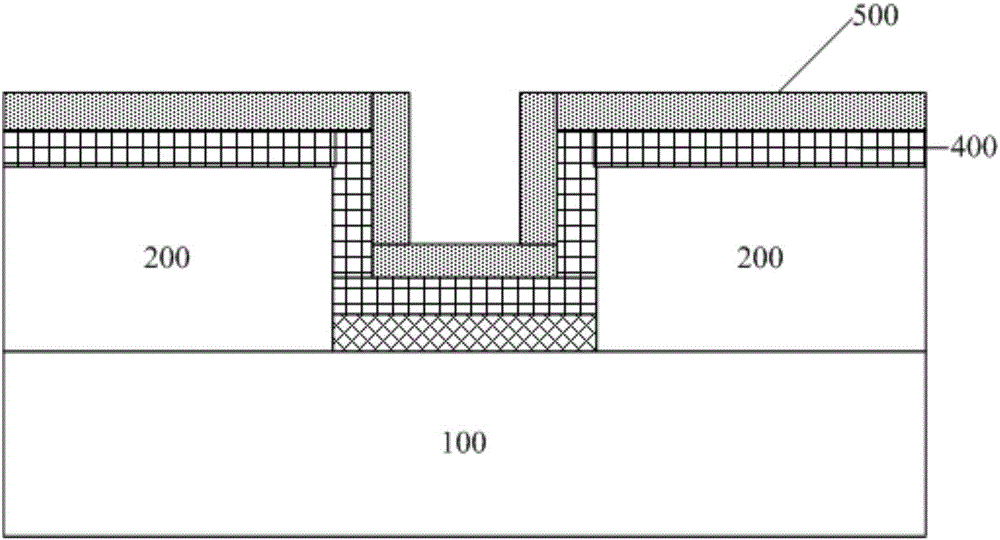

[0024] Figure 1 to Figure 4 Each step of the method for forming the MIS structure according to the preferred embodiment of the present invention is schematically shown.

[0025] Specifically, such as Figure 1 to Figure 4 As shown, the method for forming an MIS structure according to a preferred embodiment of the present invention includes:

[0026] The first step: performing ion implantation and thermal annealing on the silicon substrate 100 to form an N-type well or a P-type well;

[0027] For example, in the first step, the interlayer dielectric layer pattern 200 is formed on the silicon substrate 100 , and the silicon substrate 100 is ion-implanted and thermally annealed using the interlayer dielectric layer pattern 200 to form an N-type we...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More