Transistor forming method

A transistor and work function technology, applied in the field of semiconductor manufacturing, can solve problems such as unstable performance of static random access memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

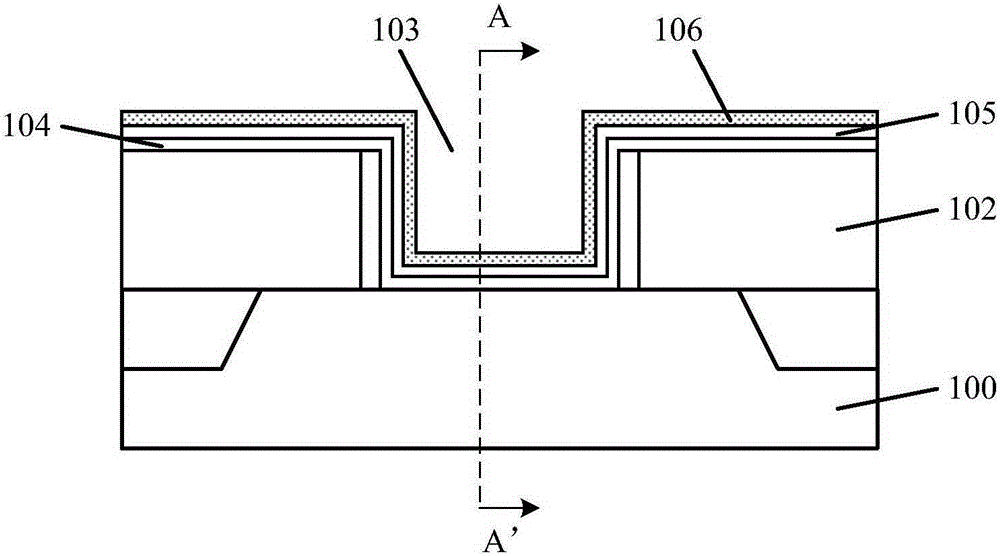

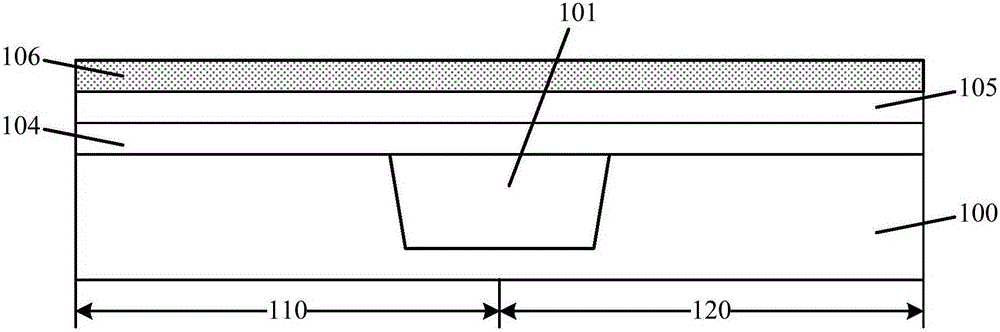

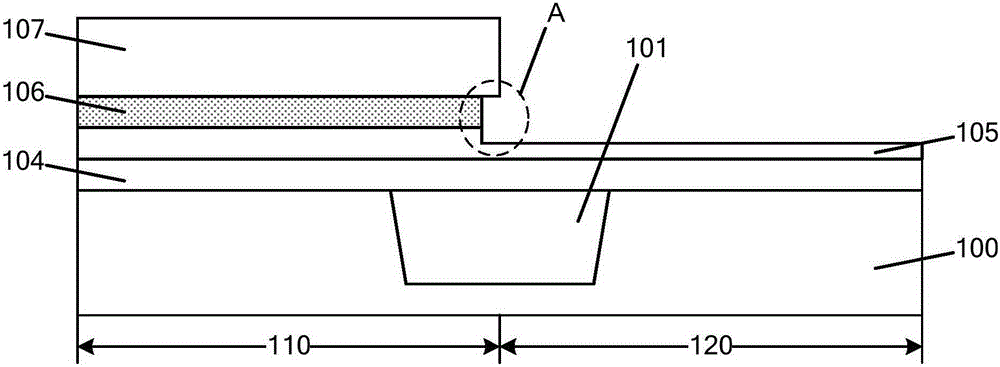

[0034] As mentioned in the background, the performance of the prior art SRAM is unstable.

[0035] After research, it is found that since the storage unit of the SRAM includes a PMOS transistor and an NMOS transistor, and the material of the work function layer required by the PMOS transistor and the NMOS transistor is different, therefore, in the formation process of the storage unit of the SRAM, it is necessary After the work function layer in the PMOS transistor is formed, the work function layer in the NMOS transistor is formed, or after the work function layer in the NMOS transistor is formed, the work function layer in the PMOS transistor is formed. However, as the device density of the SRAM increases, the work function layer formed in the NMOS transistor easily extends to the PMOS transistor, or the work function layer formed in the PMOS transistor extends to the NMOS transistor, so that the formed SRAM The performance of the device is unstable, which makes it easy to mis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More