Integrated circuit and self-protection output buffer

An output buffer, integrated circuit technology, applied in circuits, electrical solid devices, electrical components, etc., can solve problems such as large circuit layout area, and achieve the effect of saving layout space, enhancing electrostatic tolerance, and fast turn-on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

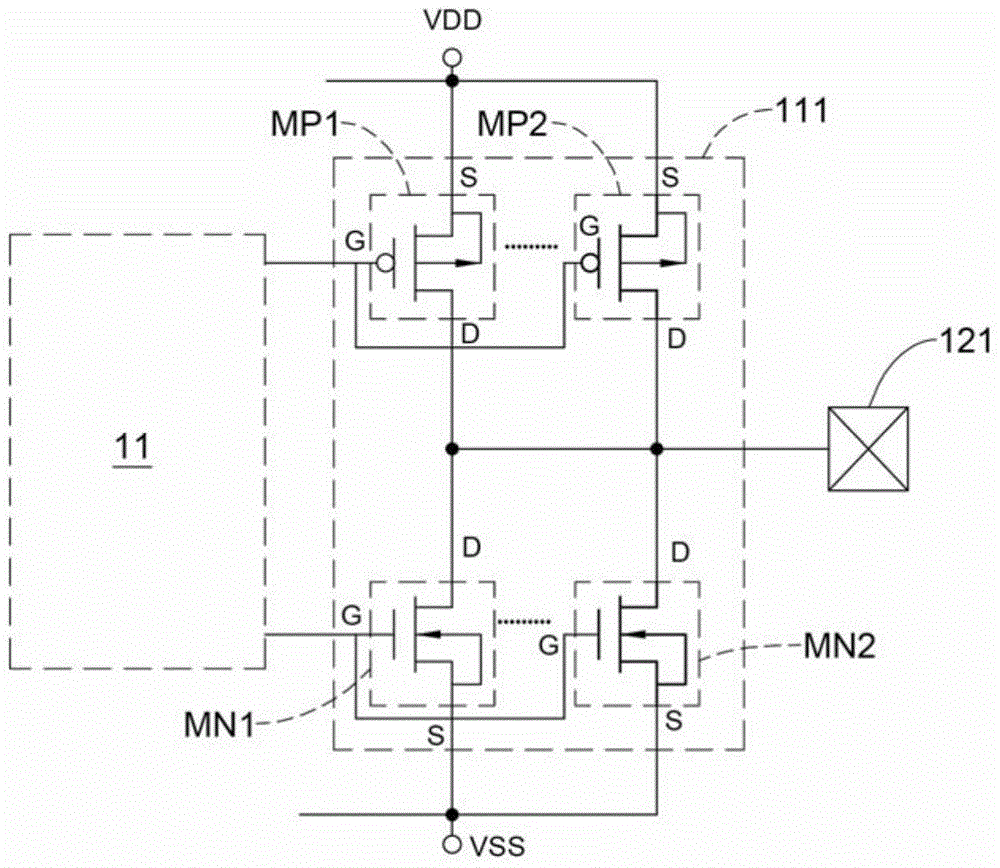

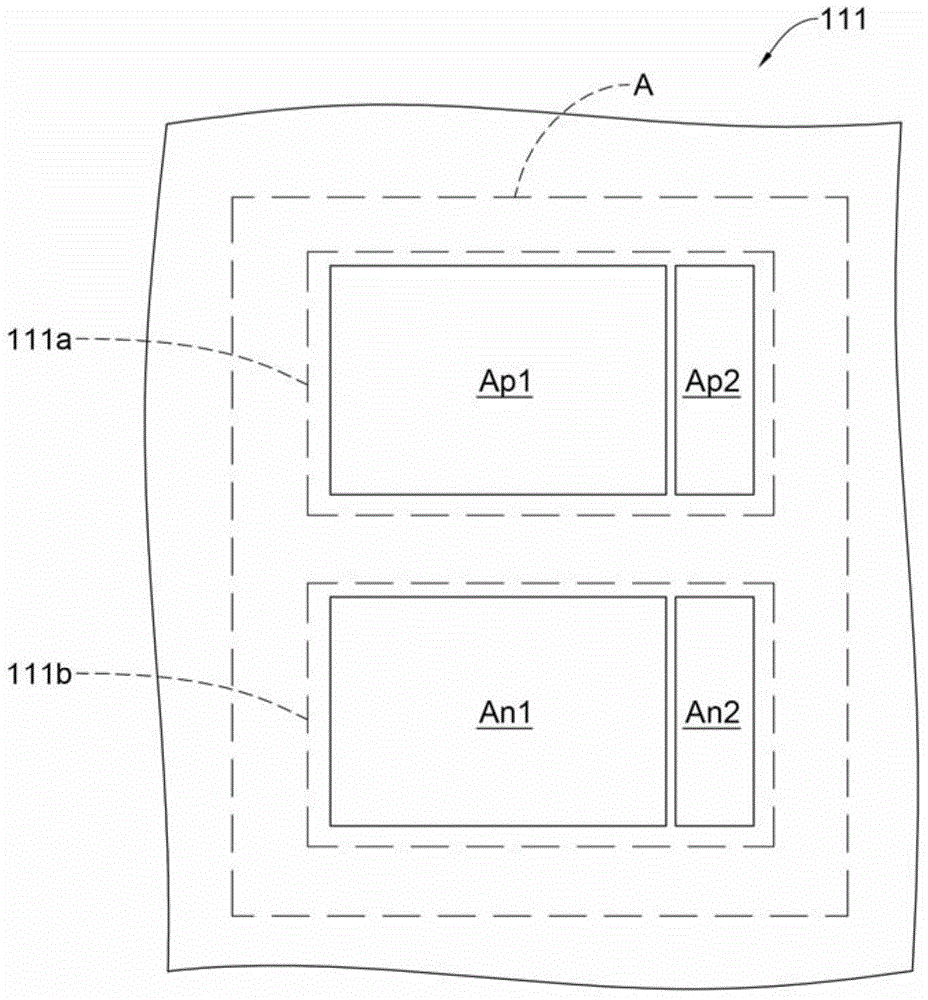

[0066] The present invention improves an output buffer connected to each output pad of an integrated circuit, especially for a large-sized output buffer of a power management integrated circuit, so that the output pad can be directly connected to the output buffer without installing an electrostatic protection circuit, and has the function of self-static protection. The following describes it in detail with several embodiments.

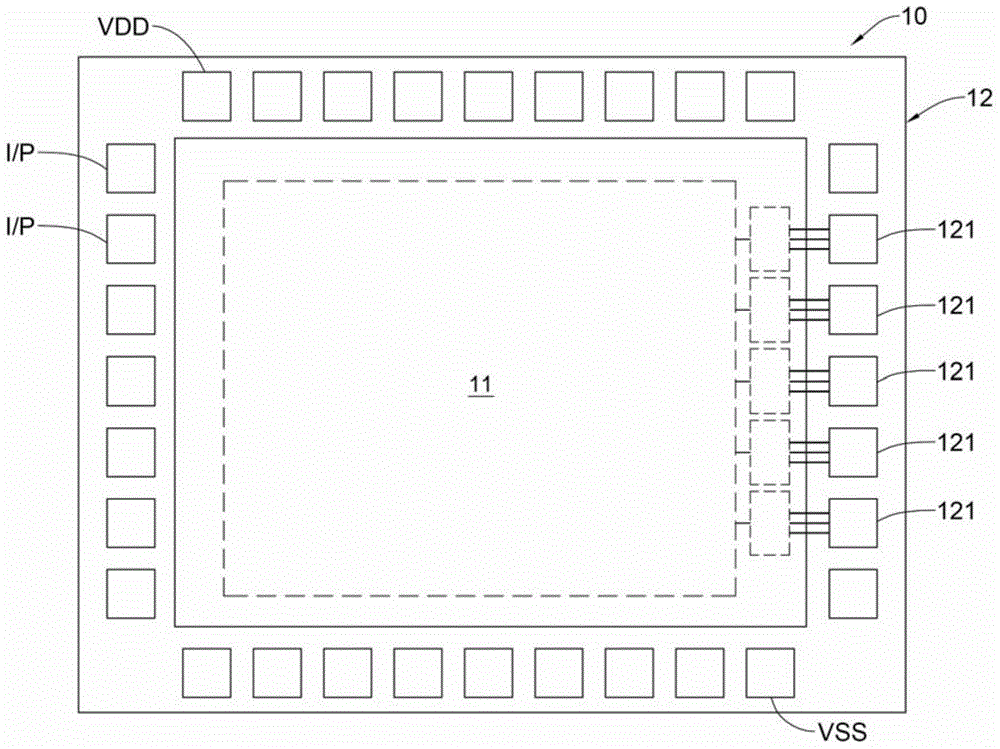

[0067] See first figure 1 as shown, figure 1 It is a schematic layout diagram of an integrated circuit 10 according to the present invention. The integrated circuit 10 includes an internal integrated circuit unit 11 and an input-output ring 12. The input-output ring 12 can surround the internal integrated circuit unit 11, but it is not intended to be To be specific, the input / output ring 12 of this embodiment includes a high potential pad VDD, a low potential pad VSS, a plurality of input pads I / P, a plurality of output pads 121 and the like. The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More