Top gate thin film transistor manufacturing method and top gate thin film transistor

A technology of a thin film transistor and a manufacturing method, which are applied to the manufacturing method of a top-gate thin-film transistor and the field of the top-gate thin-film transistor, can solve the problems of low on-state current of TFT, failure to achieve the effect of conductorization, influence on TFT characteristics, etc., and improve efficiency , high mobility and on-state current, the effect of reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The manufacturing method of the top-gate thin film transistor and the specific implementation of the top-gate thin film transistor provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

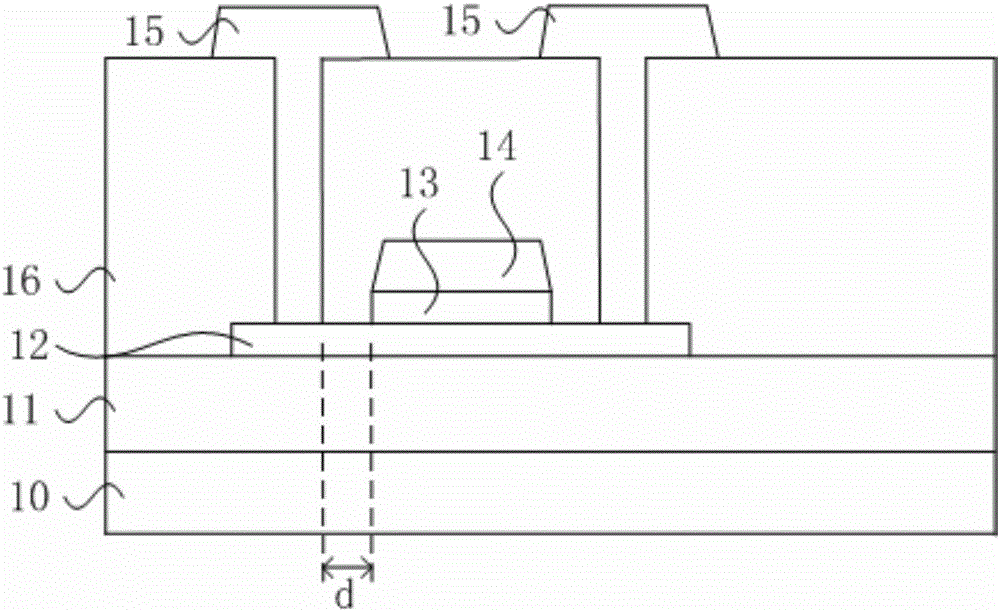

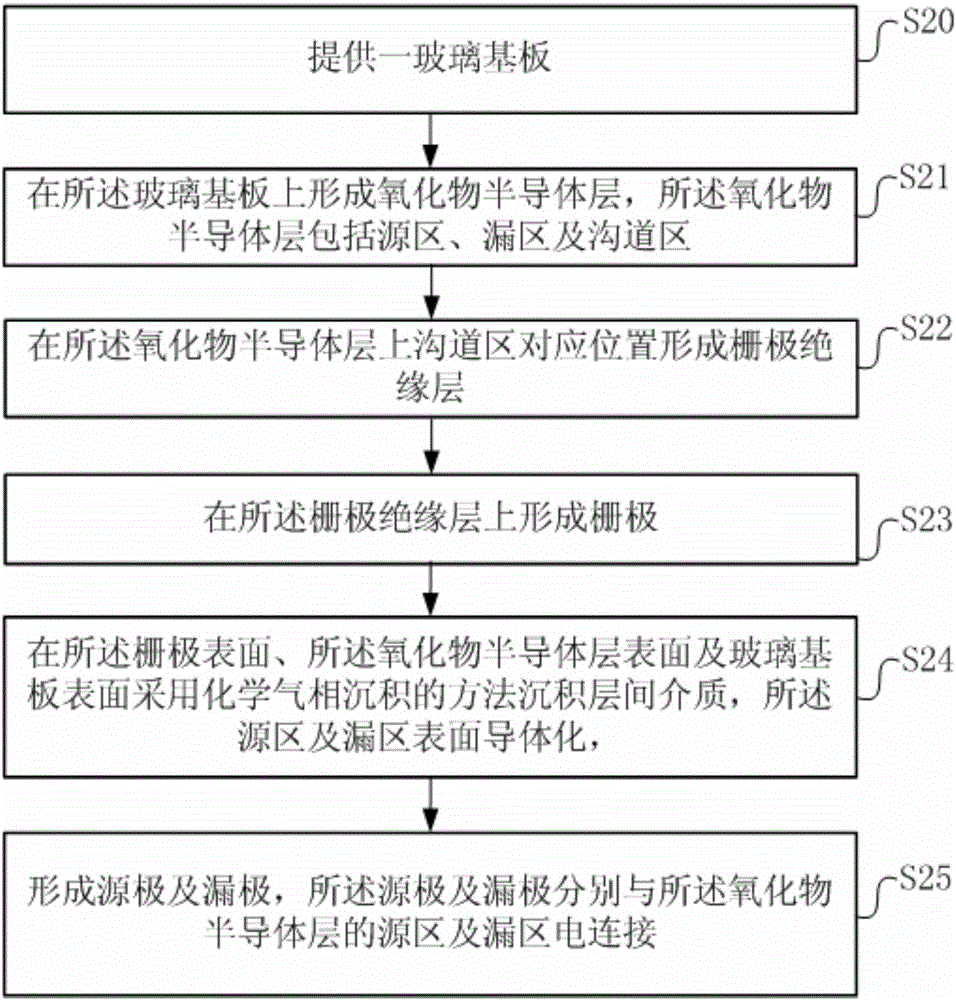

[0029] see figure 2 , the present invention provides a method for manufacturing a top-gate thin film transistor, the method comprising the following steps: step S20, providing a glass substrate; step S21, forming an oxide semiconductor layer on the glass substrate, the oxide semiconductor layer Including a source region, a drain region and a channel region; step S22, forming a gate insulating layer at a position corresponding to the channel region on the oxide semiconductor layer; step S23, forming a gate on the gate insulating layer; step S24 . Deposit an interlayer dielectric on the surface of the gate, the surface of the oxide semiconductor layer and the surface of the glass substrate by chemical vapor deposition, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More