Array substrate, manufacturing method thereof, and display device

A technology of an array substrate and a manufacturing method, applied in the display field, can solve the problems of threshold voltage Vth drift, short charging time, inability of GOA unit to realize scanning function, etc., and achieve the effect of preventing Vth drift and meeting charging rate requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0073] This embodiment provides a method for manufacturing an array substrate, the array substrate includes a display region and a GOA region, and the method includes:

[0074] making the active layer of the first thin film transistor in the display area by using a metal oxide semiconductor material;

[0075] The active layer of the second thin film transistor in the GOA region is fabricated by using non-metal oxide semiconductor material.

[0076] In this embodiment, the active layer of the thin film transistor in the display area of the array substrate and the active layer of the thin film transistor in the GOA area are made of different materials, and the active layer of the thin film transistor in the display area of the array substrate is made of metal oxide In this way, when the resolution of display products is very high, due to the relatively high mobility of metal oxide semiconductor materials, it can also meet the charging rate requirements of high-resolution dis...

Embodiment 2

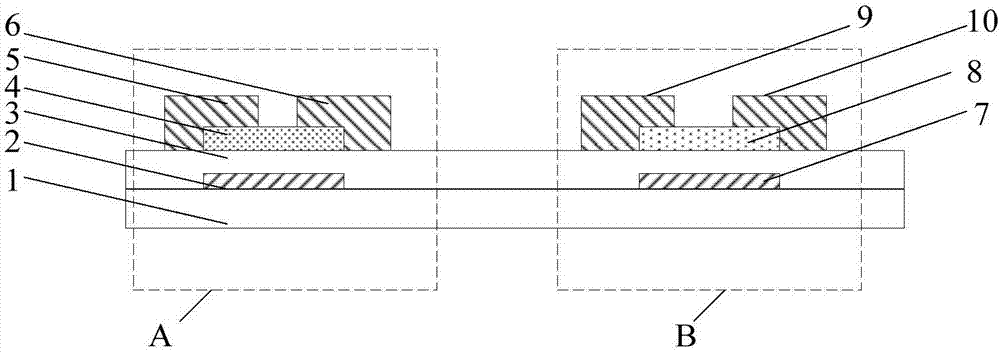

[0109] Taking the fabrication of a bottom-gate array substrate as an example, the fabrication method of the array substrate of the present invention will be further introduced in conjunction with the accompanying drawings:

[0110] The manufacturing method of the array substrate in this embodiment specifically includes the following steps:

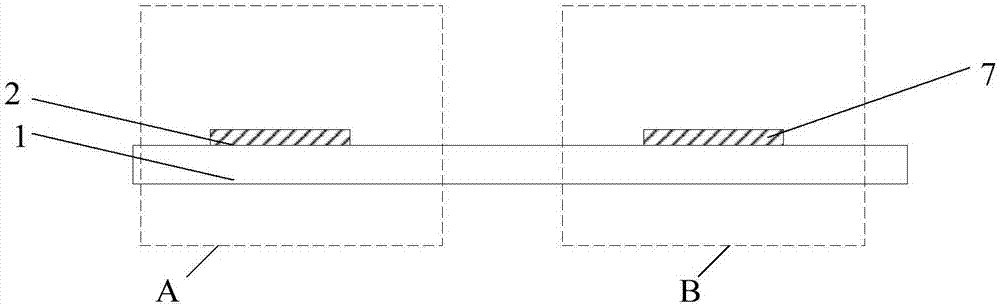

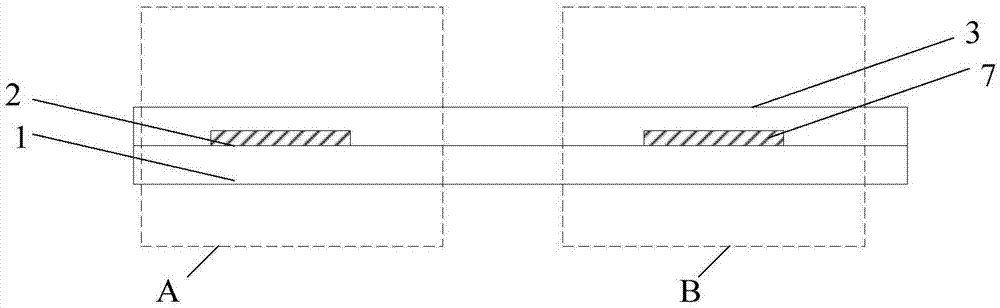

[0111] Step 1, such as figure 2 As shown, a base substrate 1 is provided, and the gate electrode 2 of the thin film transistor in the display area, the gate electrode 7 and the gate line pattern of the thin film transistor in the GOA area are formed on the base substrate 1;

[0112] Wherein, the base substrate may be a glass substrate or a quartz substrate. Specifically, sputtering or thermal evaporation can be used to deposit a thickness of about The gate metal layer, the gate metal layer can be Cu, Al, Ag, Mo, Cr, Nd, Ni, Mn, Ti, Ta, W and other metals and alloys of these metals, the gate metal layer can be single-layer structure or ...

Embodiment 3

[0123] Taking the fabrication of a bottom-gate array substrate as an example, the fabrication method of the array substrate of the present invention will be further introduced in conjunction with the accompanying drawings:

[0124] The manufacturing method of the array substrate in this embodiment specifically includes the following steps:

[0125] Step 1, such as figure 2 As shown, a base substrate 1 is provided, and the gate electrode 2 of the thin film transistor in the display area, the gate electrode 7 and the gate line pattern of the thin film transistor in the GOA area are formed on the base substrate 1;

[0126] Wherein, the base substrate may be a glass substrate or a quartz substrate. Specifically, sputtering or thermal evaporation can be used to deposit a thickness of about The gate metal layer, the gate metal layer can be Cu, Al, Ag, Mo, Cr, Nd, Ni, Mn, Ti, Ta, W and other metals and alloys of these metals, the gate metal layer can be single-layer structure or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More