Three-dimensional on-chip network test planning method

A technology of test planning and network-on-chip, which is applied in software testing/debugging, error detection/correction, and special data processing applications, etc. It can solve problems such as insufficient optimization effect of test planning algorithms and limited application range of models, achieving short test time, The effect of low power consumption and increased diversity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described below in conjunction with the accompanying drawings and embodiments, but not to limit the content of the present invention.

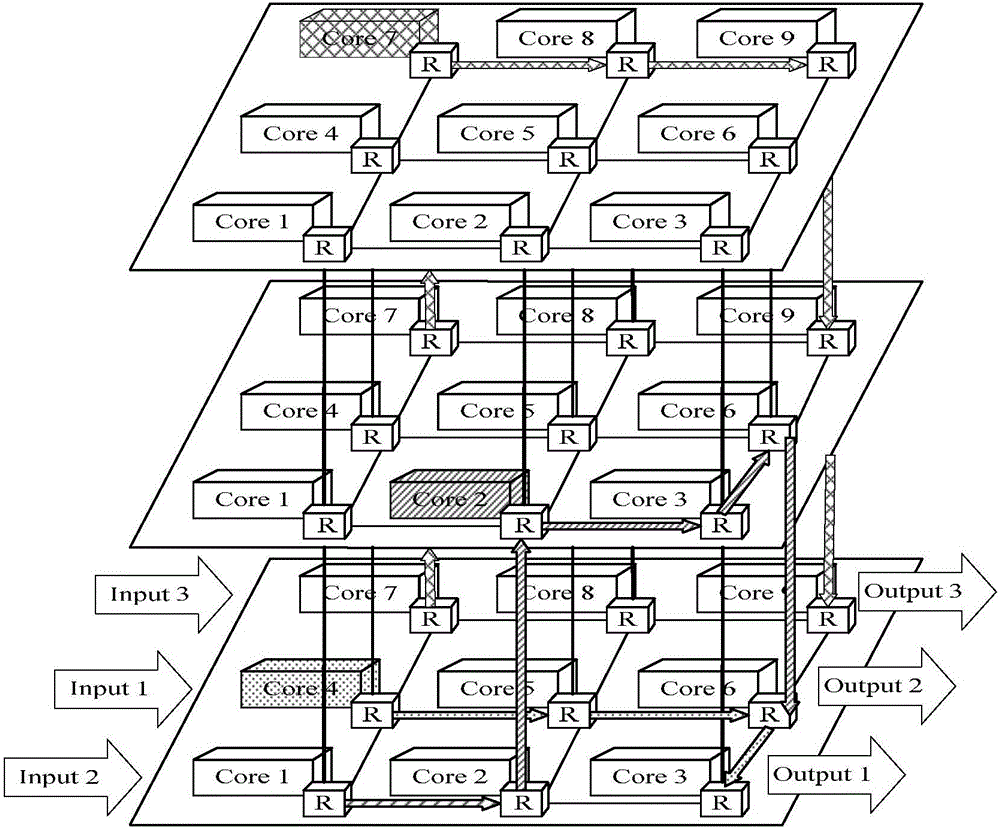

[0042] The 3D NoC involved in the preferred embodiment of the present invention is a 3D Mesh topology, such as figure 1 As shown, two-dimensional chips with multiple planar structures are vertically interconnected through silicon via technology, that is, they are mainly composed of IP cores, routing nodes, network interfaces, and communication links. The communication link includes interconnection lines in XY direction and TSV (Through Silicon Via) in Z direction. The routers in the 3D NoC adopt the wormhole data exchange mechanism based on the virtual channel technology, and the routing algorithm adopts the XYZ routing algorithm, and each router connects to the resource nodes through the resource network interface. Since 3D NoC supports high-efficiency and reusable design, it adopts distributed technology...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More