Implementation method of multi-channel temperature chip interface based on fpga

An implementation method and chip technology, which is applied in the field of relatively high occupancy, can solve problems such as large FPGA resources, low temperature acquisition accuracy, occupancy, etc., and achieve the effect of saving FPGA logic resources and having scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

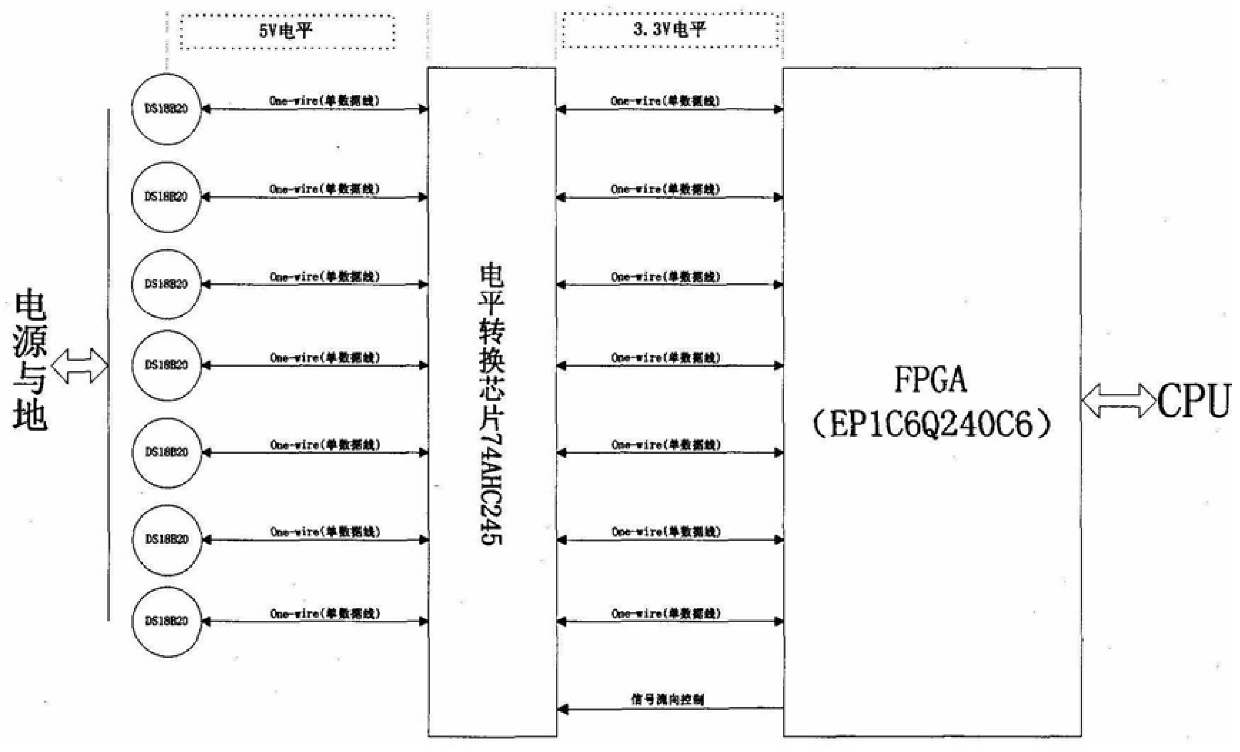

[0065] Fig. 1 is a schematic diagram of the 7-way DS18B20 temperature chip interface of the present invention. The hardware platform of this embodiment mainly includes

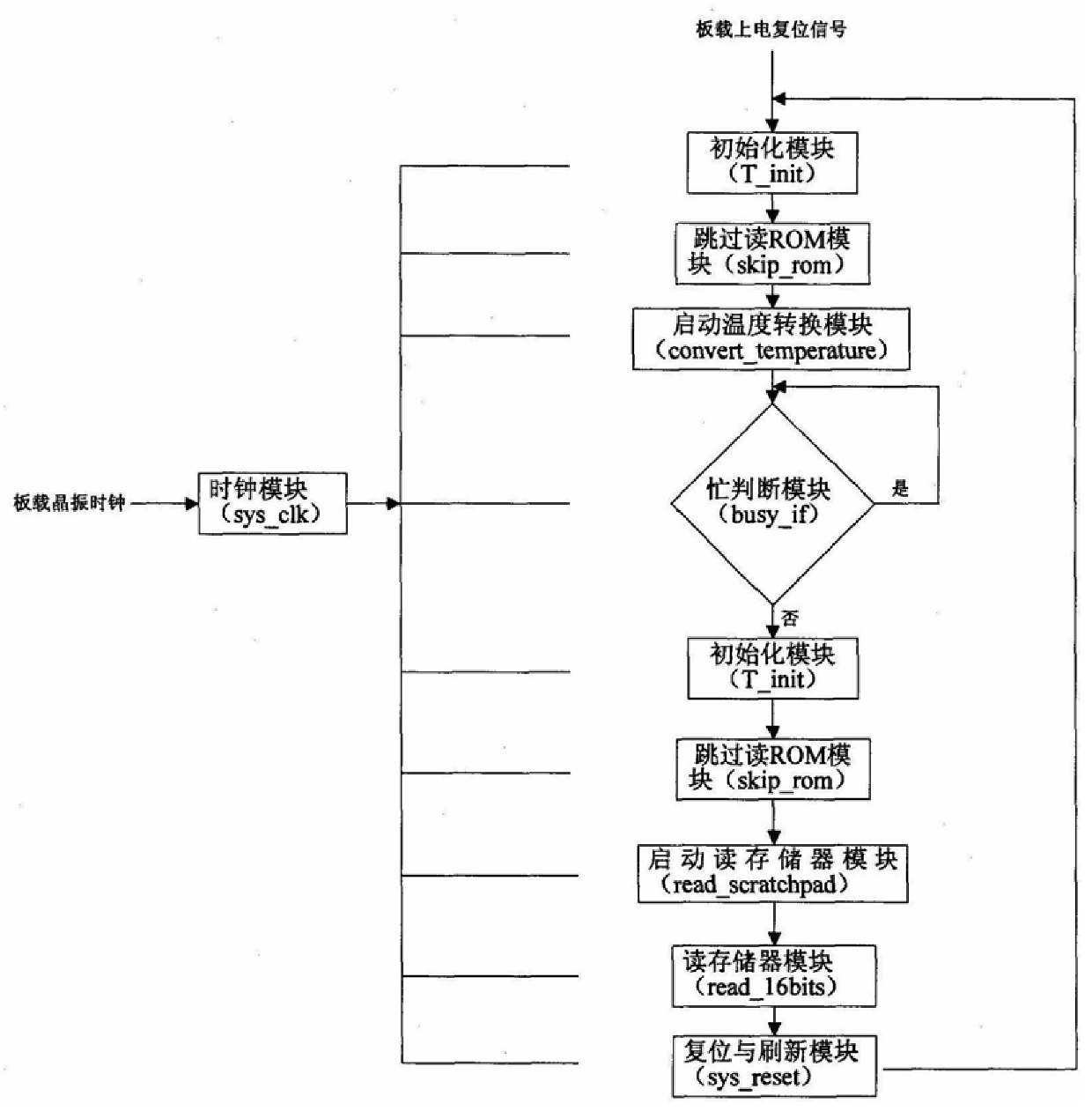

[0067] Fig. 2 is a work flow diagram of each functional module in the interface implementation method of the present invention. FPGA-based multi-channel temperature

[0069] Function introduction: realize the frequency division of the reference crystal oscillator on the board to obtain a clock signal with a period of 1us. This specific

[0080] Function introduction: starting the temperature conversion module means starting the DS18B20 temperature chip to start temperature conversion.

[0088] Function introduction: start reading the memory module to indicate that the memory reading of the DS18B20 temperature chip will be started next.

[0098] The present invention is uniformly called by the DS18B20_zjq module (top-level (TOP) module).

[0100] Function introduction: the top-level module controls each of the ab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More