Wafer level dynamic pre-burning test method

A test method and wafer-level technology, applied in the field of testing, can solve the problems of large packaging and testing costs, expenses, and inability to effectively reduce production costs, and achieve the effect of reducing packaging and testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

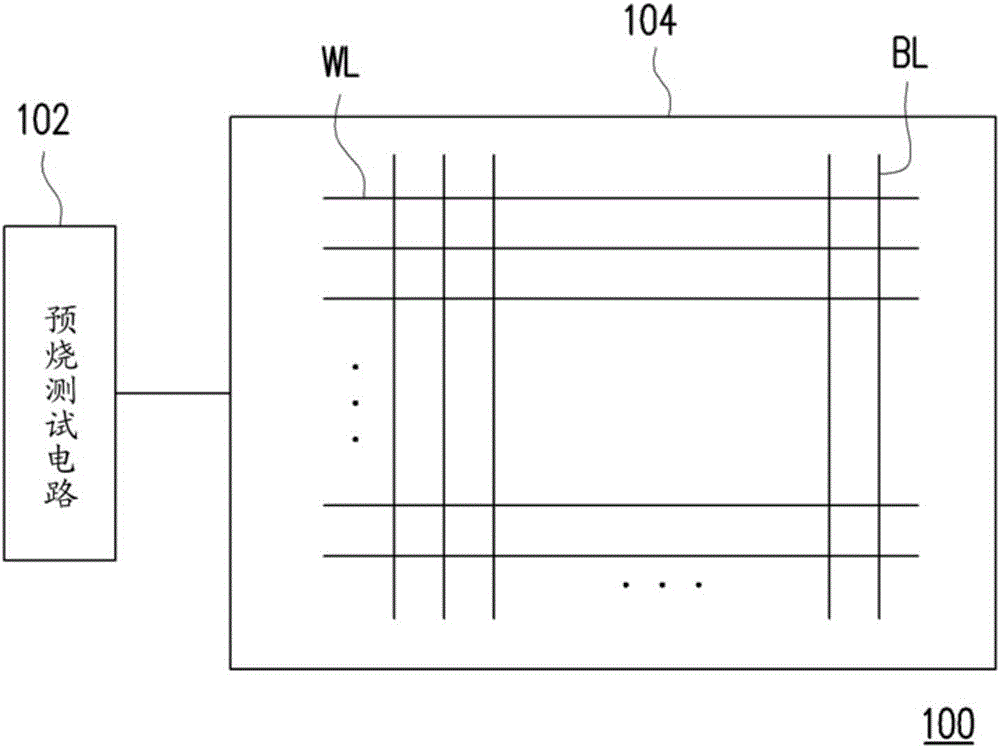

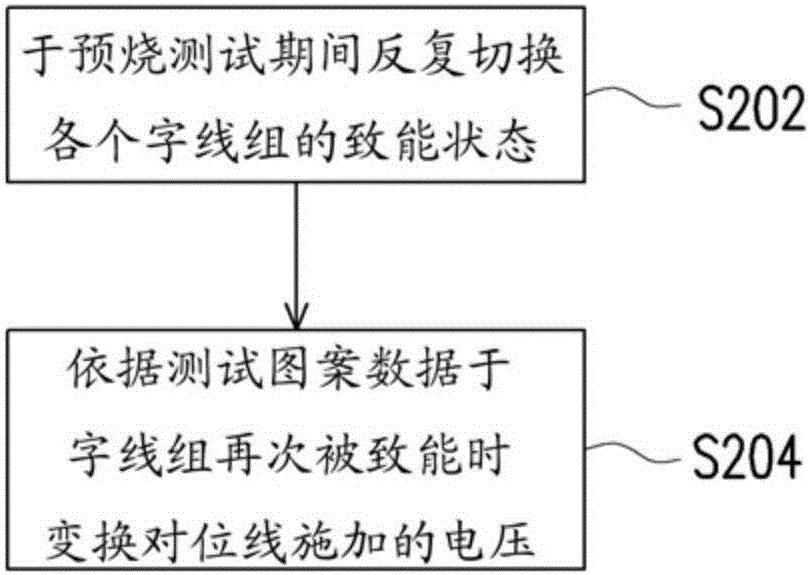

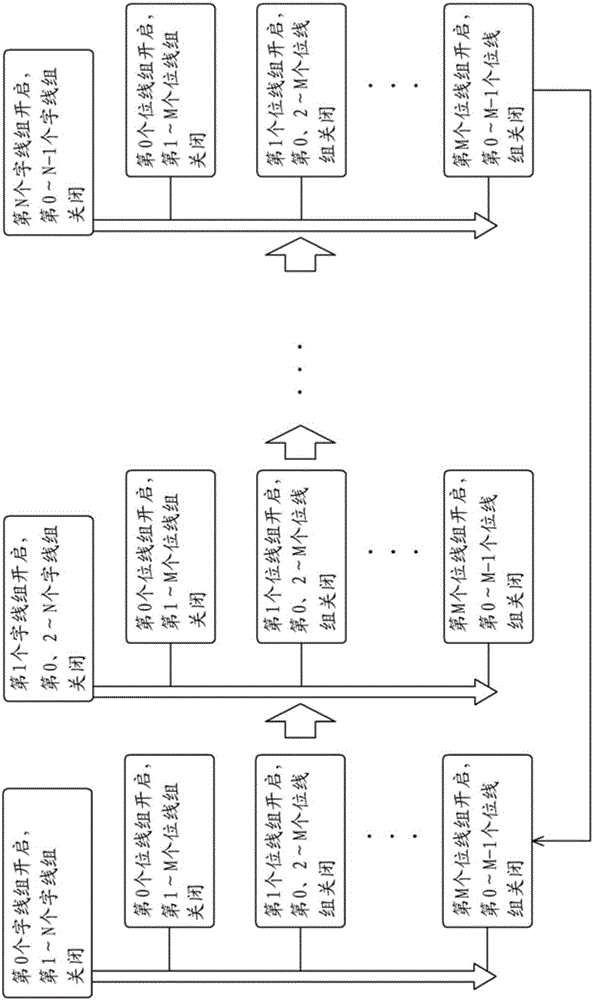

[0021] figure 1 is a schematic diagram of a memory chip of a wafer according to an embodiment of the present invention, figure 2 is a schematic flow chart of a wafer-level dynamic burn-in test method according to an embodiment of the present invention, please refer to figure 1 and figure 2 . A wafer (not shown) may include multiple memory chips. For ease of illustration, only one memory chip 100 is shown in this embodiment for illustration. In fact, the memory chips in the wafer can be burn-in tested at the same time. The memory chip 100 may include a burn-in test circuit 102 and a memory array 104, wherein the memory array 104 includes a plurality of word lines WL and a plurality of bit lines BL, and the intersection of the word lines WL and the bit lines BL is configured with the word line WL and the bit lines BL-connected memory cells (not shown). The word line WL can be divided into multiple word line groups, and the burn-in test circuit 102 can receive a burn-in tes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More