FPGA-based server acceleration technology

A server and domain technology, applied in the field of FPGA-based server acceleration technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings.

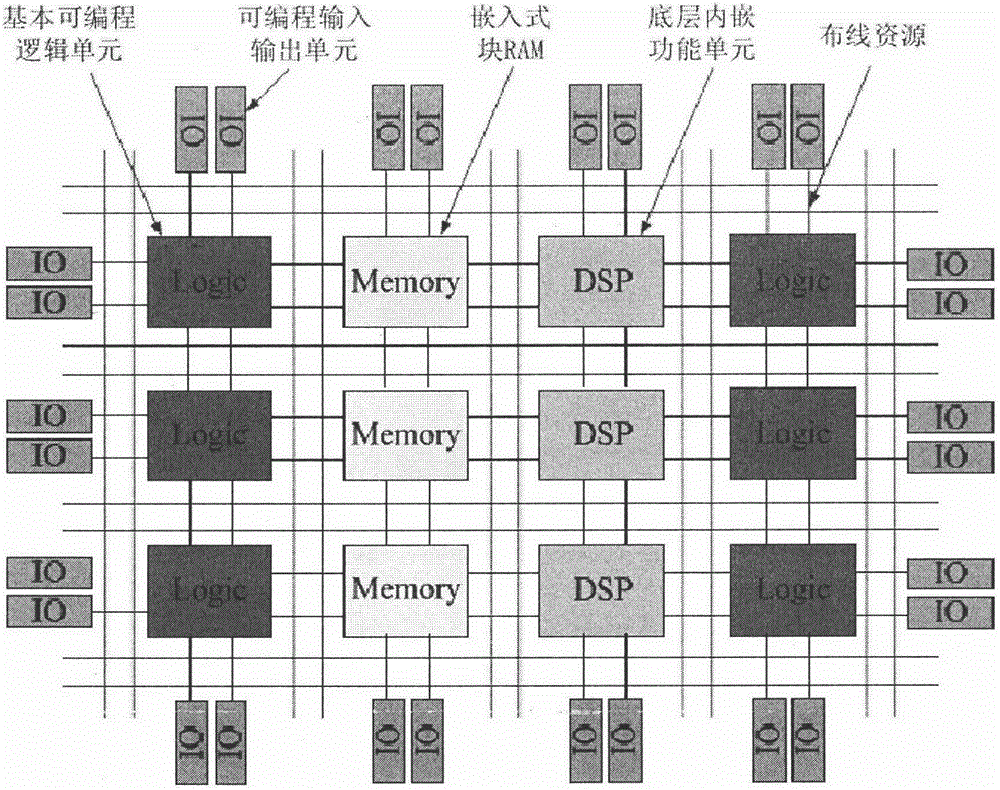

[0024] figure 1 Shown is the FPGA internal structure. It mainly includes 6 parts. They are: embedded RAM, basic programmable logic unit, programmable input and output unit, rich layout and routing resources, complete clock management, embedded dedicated hard core module and embedded underlying functional unit.

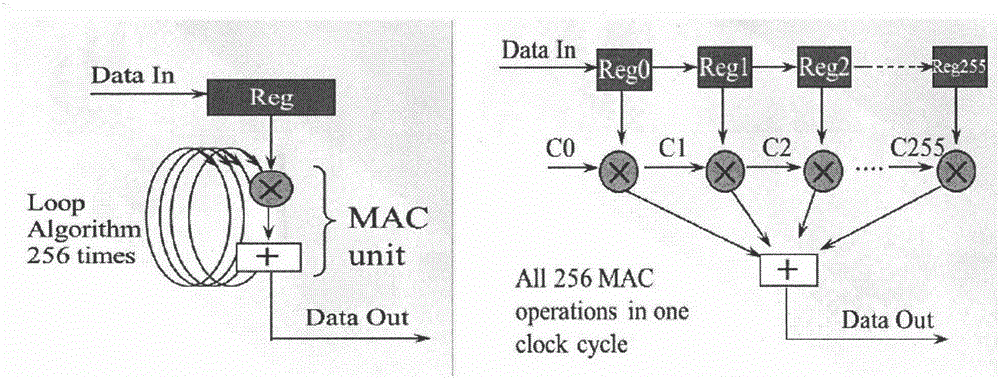

[0025] figure 2 Shown is the space-for-time strategy of the FPGA. Taking the multiplication and accumulation operation of the CPU as an example, in order to realize the multiplication and accumulation operation, if the CPU is used to implement it, it is necessary to repeatedly call the multiplication and addition unit of the CPU for 256 clock cycles to have an output. However, if the FPGA is used for processing, the internal resources of the FPGA can be used to implement a multi-engine multiply-accumulator, so that 256 multiply-accumulate operations can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com