Chip package structure and method

A chip packaging structure and chip packaging technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of unfavorable chip heat dissipation, large thickness, etc., and achieve the effect of increasing interconnect channel density, reducing restrictions, and increasing bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

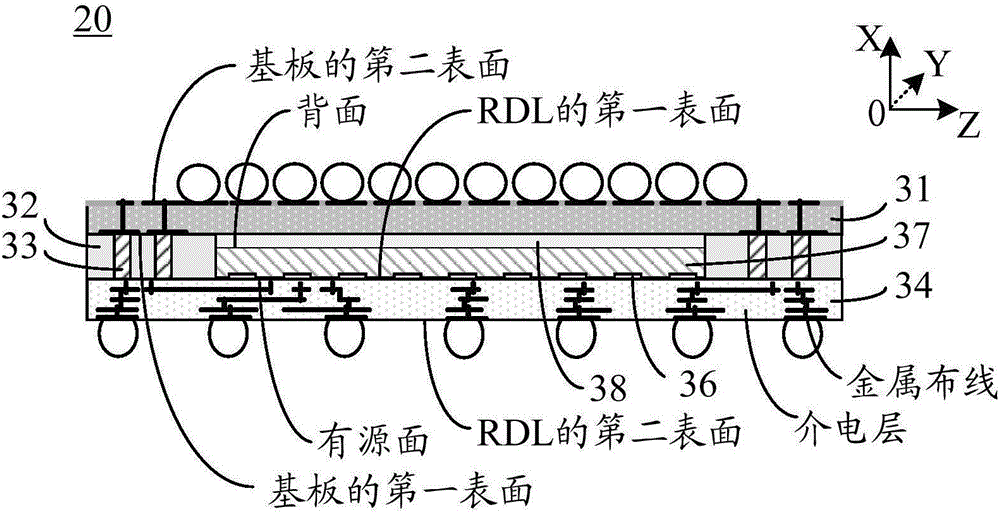

[0121] The technical solutions in the embodiments of the present application will be clearly described below with reference to the drawings in the embodiments of the present application.

[0122] For ease of understanding, first combine figure 1 The scenario of the chip packaging structure applicable to the embodiment of the present application is briefly described.

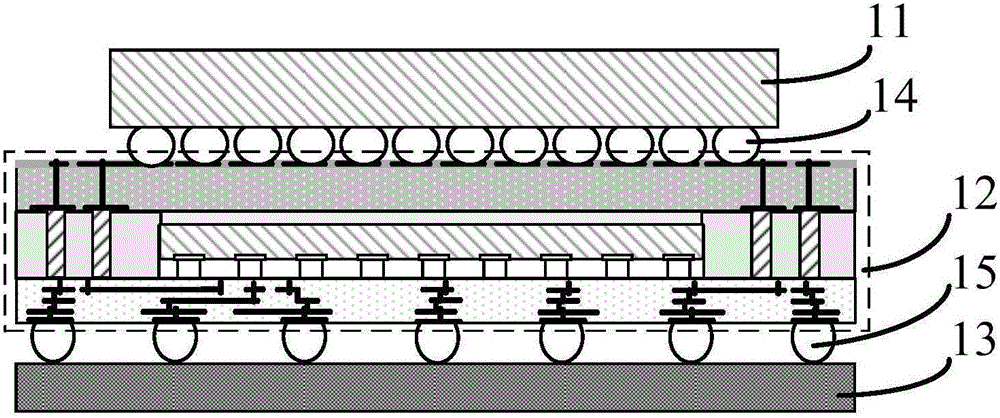

[0123] figure 1 is a schematic diagram of a scenario of a chip packaging structure applicable to an embodiment of the present application. Such as figure 1 As shown, the chip package structure 12 can be connected to the top layer chip 11 through a connector 14 (for example, a solder ball, specifically, a solder ball (solder ball), etc.), and the chip package structure 12 can be connected through a connector 15 ( For example, solder balls (specifically, solderballs, etc.) are connected to a printed circuit board (Printed Circuit Board, “PCB” for short) 13 on the lower layer. Among them, the top chip 11 can be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More