Avoidance method for conflict between instruction sets in RISC-CPU and avoidance system thereof

A RISC-CPU and instruction set technology, applied in the direction of concurrent instruction execution, program control design, instruments, etc., can solve the problems that there is no CPU hardware design engineering strategy, and there is no instruction system to provide RAW coherent conflict resolution methods, etc., to achieve The effect of smooth pipeline

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention is described in detail below in conjunction with accompanying drawing:

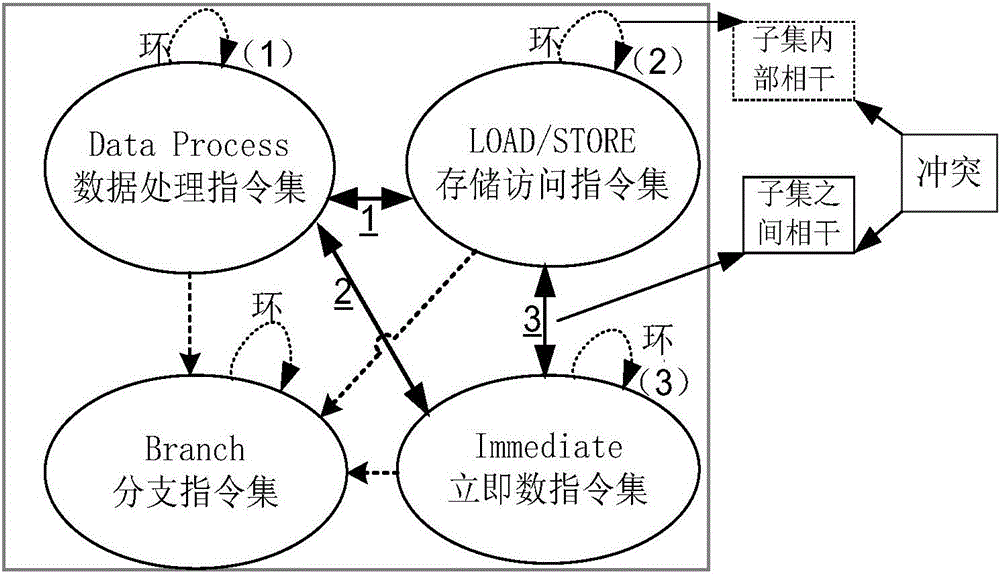

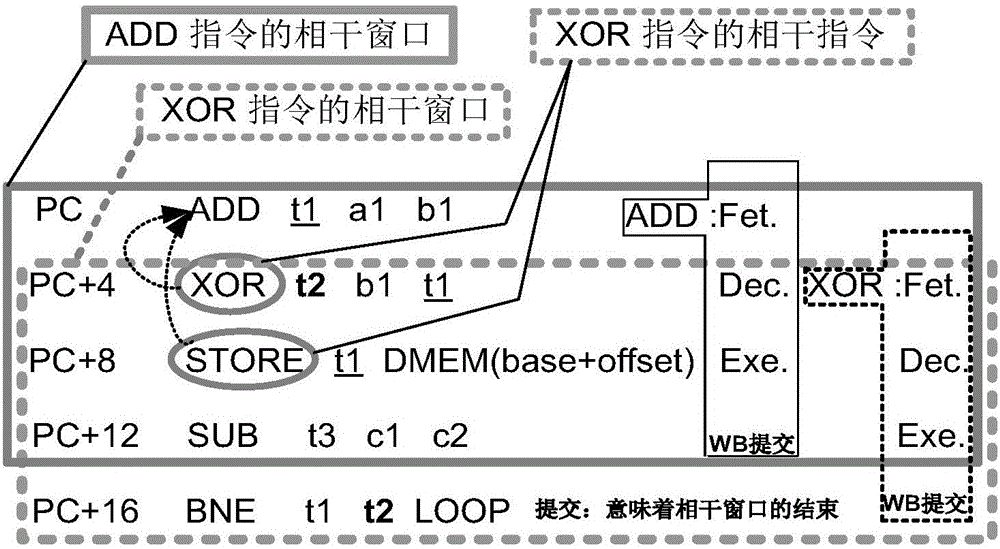

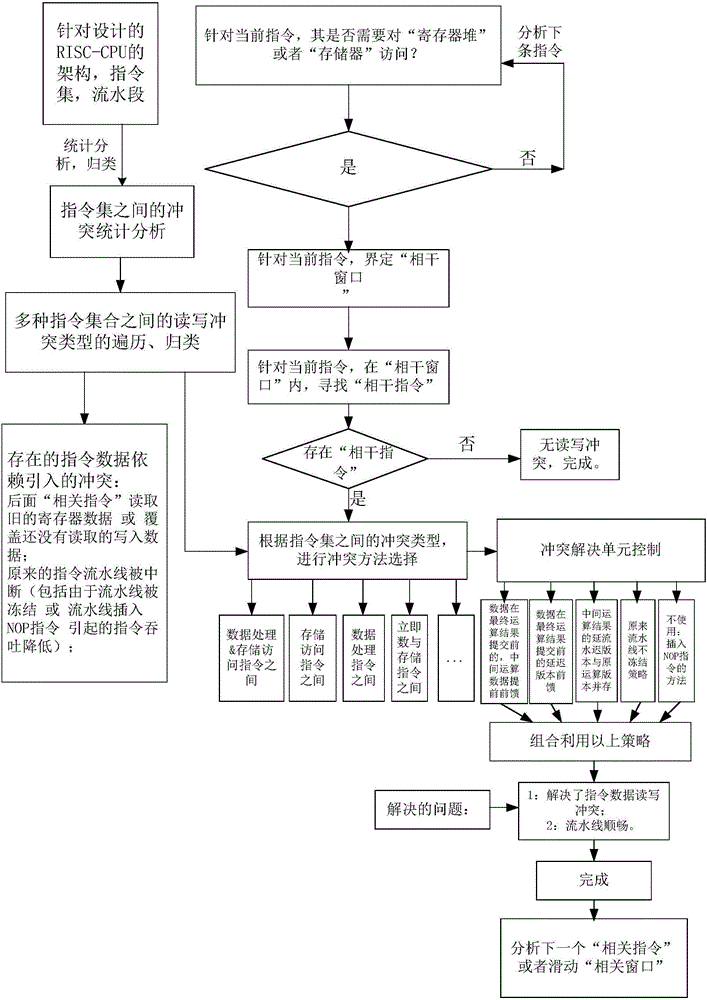

[0046] Such as figure 1 As shown, the present invention proposes an effective method for resolving CPU instruction conflicts. The present invention divides all instructions in the design into 4 categories (data processing instructions, branch Branch instructions, immediate data instructions, and storage access instructions), extracts representative instruction subsets from each type of instruction, and solves the internal problems of the instruction subsets respectively. Conflicts with RAW (write-after-read) direct data coherence between them. Pre-statistically analyze all potential RAW conflicts, and then locate and resolve conflicts to achieve a smooth pipeline.

[0047] The RISC-CPU design proposed by the present invention divides all instruction sets into data processing (Data-Processing), memory access (STORE / LOAD), branch (Branch), and immediate data (Immediate) four i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More