Chip debugging system and method and system chip

A technology for debugging systems and SoCs, applied in instruments, error detection/correction, computing, etc., can solve problems such as prolonged development time, difficulty in copying, and inability to know program errors, so as to improve speed, efficiency, and convenience. , the effect of avoiding the loss of debugging information

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the content of the present invention clearer, the following examples are listed as examples in which the present invention can actually be implemented. In addition, wherever possible, elements / components / steps using the same reference numerals in the drawings and embodiments represent the same or similar parts. Elements / components / steps using the same symbols or using the same terms in different embodiments can refer to related descriptions.

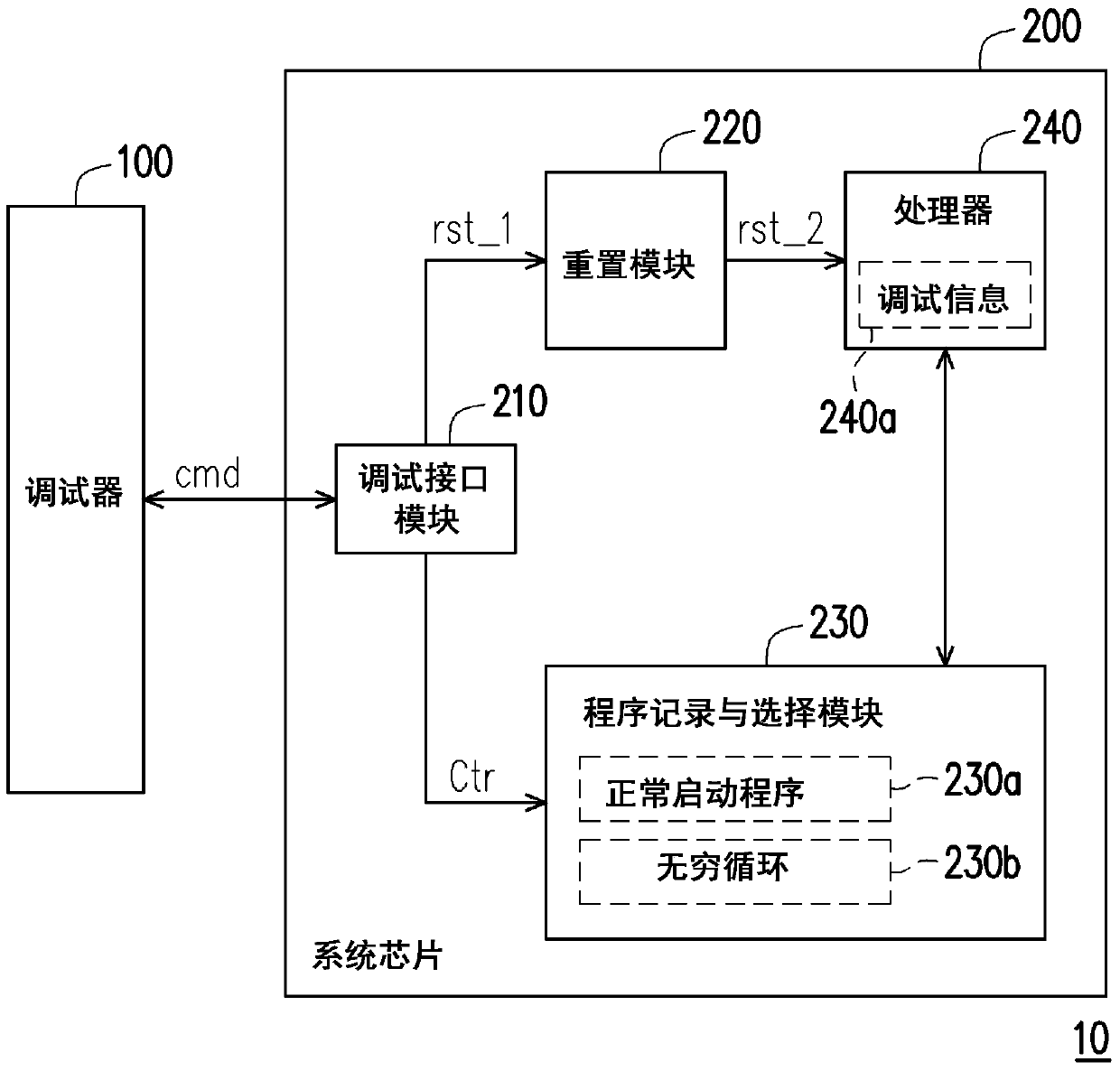

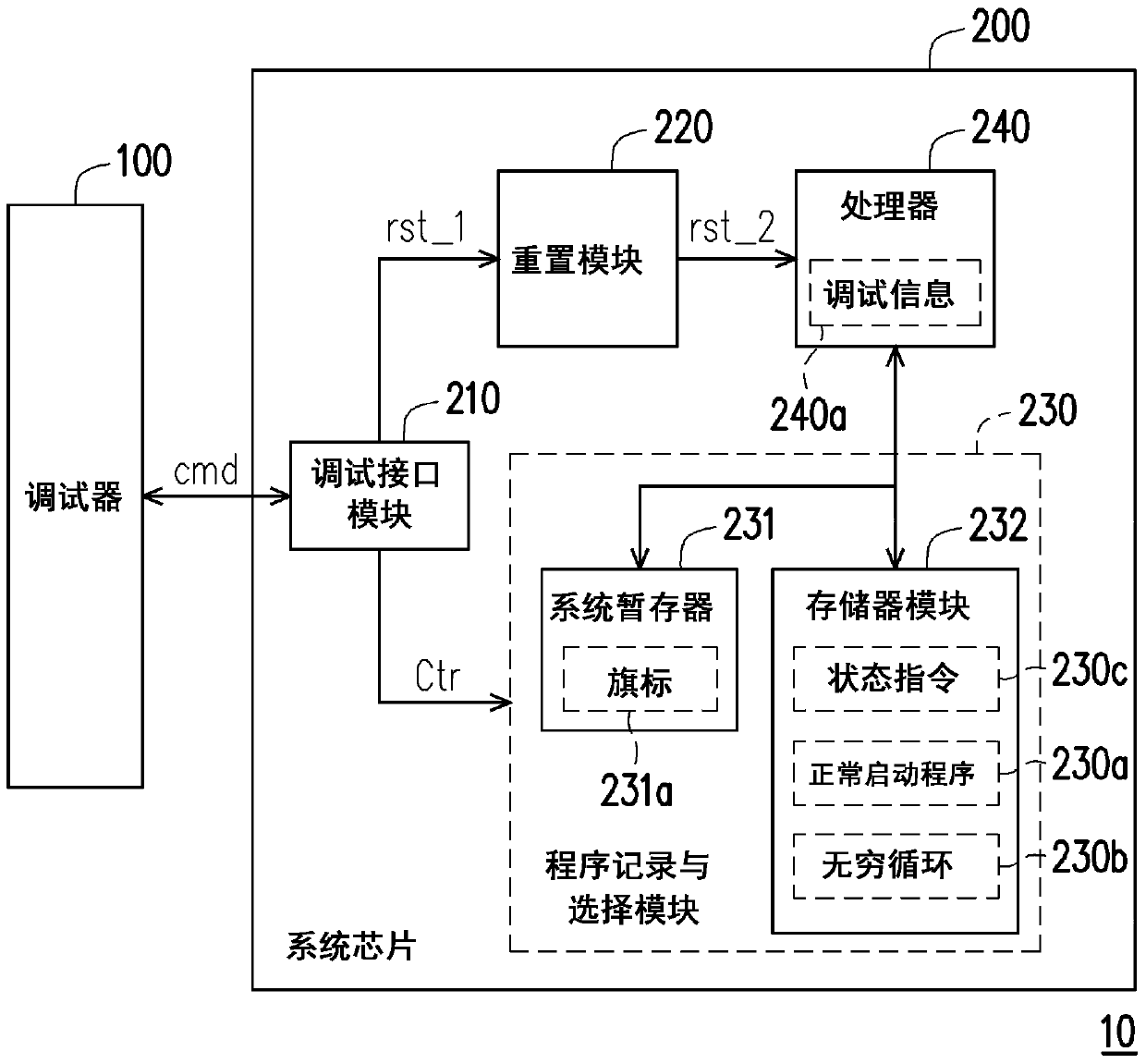

[0045] figure 1 It is a schematic block diagram of a chip debugging system according to an embodiment of the present invention. Please refer to figure 1, the chip debugging system 10 includes a debugger 100 and a system chip 200 . The SoC 100 is formed by constructing many types of circuit modules with different functions on a single chip. For example, the SoC 100 may include elements such as a processor, a digital signal processor, or a memory. The debugger 100 is a computer program and tool for debugging ot...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More