An implementation method of heterogeneous many-core based on sparse matrix-vector multiplication based on Shenwei 26010 processor

A technology of sparse matrix and implementation method, which is applied in the direction of electrical digital data processing, instruments, machine execution devices, etc., can solve the problem of unbalanced load access bandwidth utilization sparse matrix, etc., so as to improve the utilization rate of memory access bandwidth and improve the overall Performance, the effect of reducing scheduling overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be described in detail below in conjunction with examples.

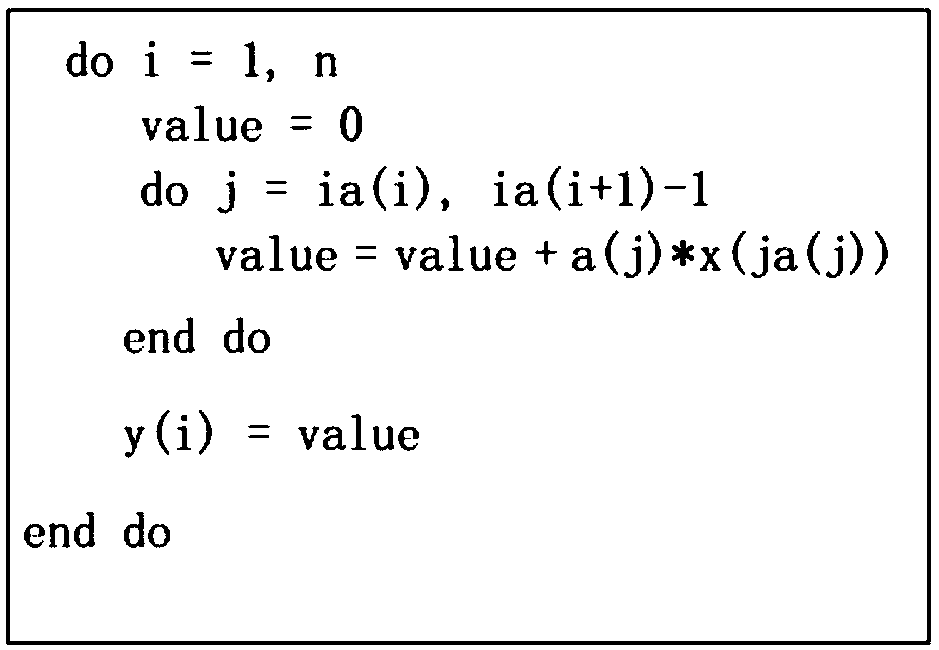

[0044] Such as figure 1 As shown, the implementation process of the main core version of SpMV is as follows:

[0045] (1) Carry out cyclic calculation for each row of the sparse matrix, first obtain the current row number and judge, if the current row number is less than the total number of rows of the sparse matrix, proceed to the next step;

[0046] (2) Traverse all the sparse non-zero elements in each row, obtain the value information of the current non-zero element and the column subscript information through array access, and obtain the value of the vector x according to the column subscript information, multiply the two together and obtain Accumulate to get the calculation result of the current row;

[0047] (3) Assign the calculation result to the vector y.

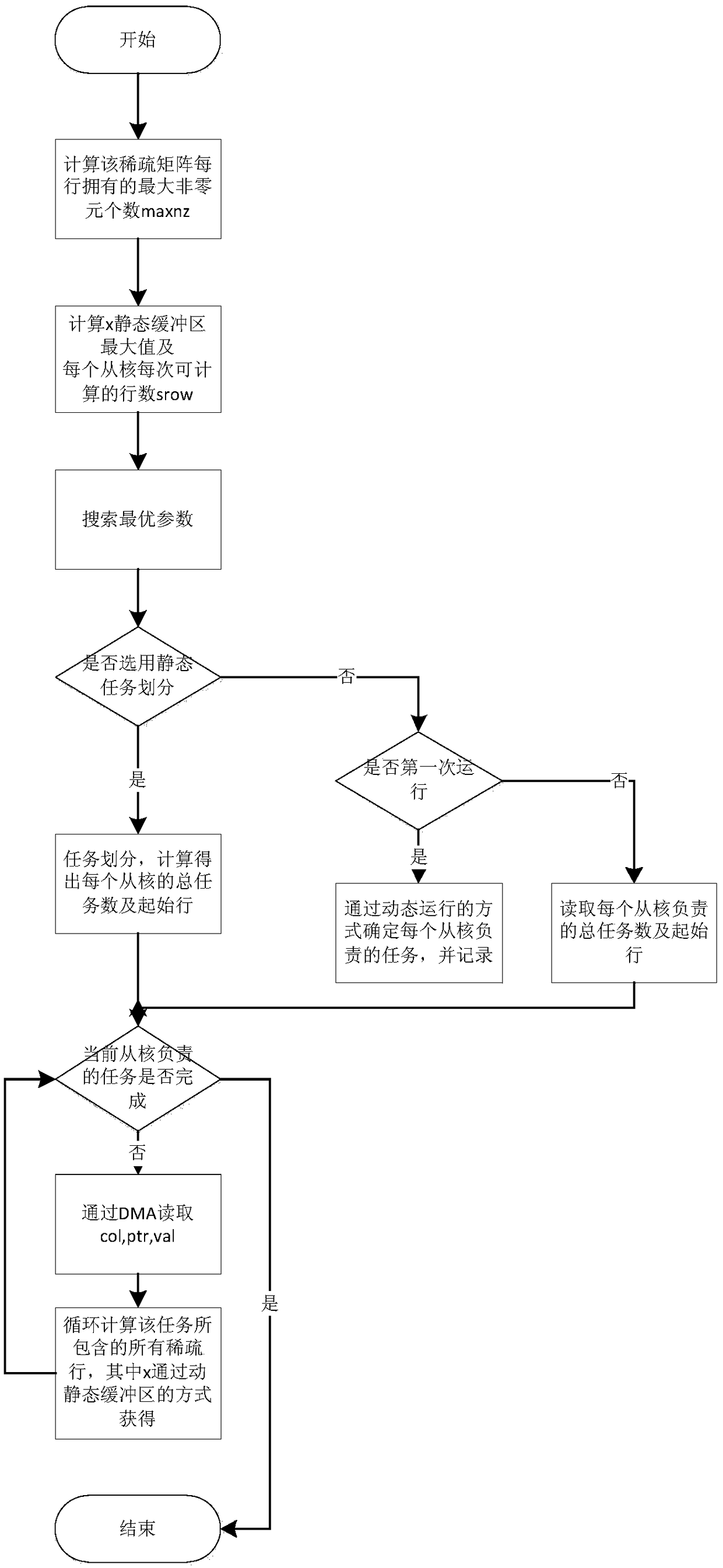

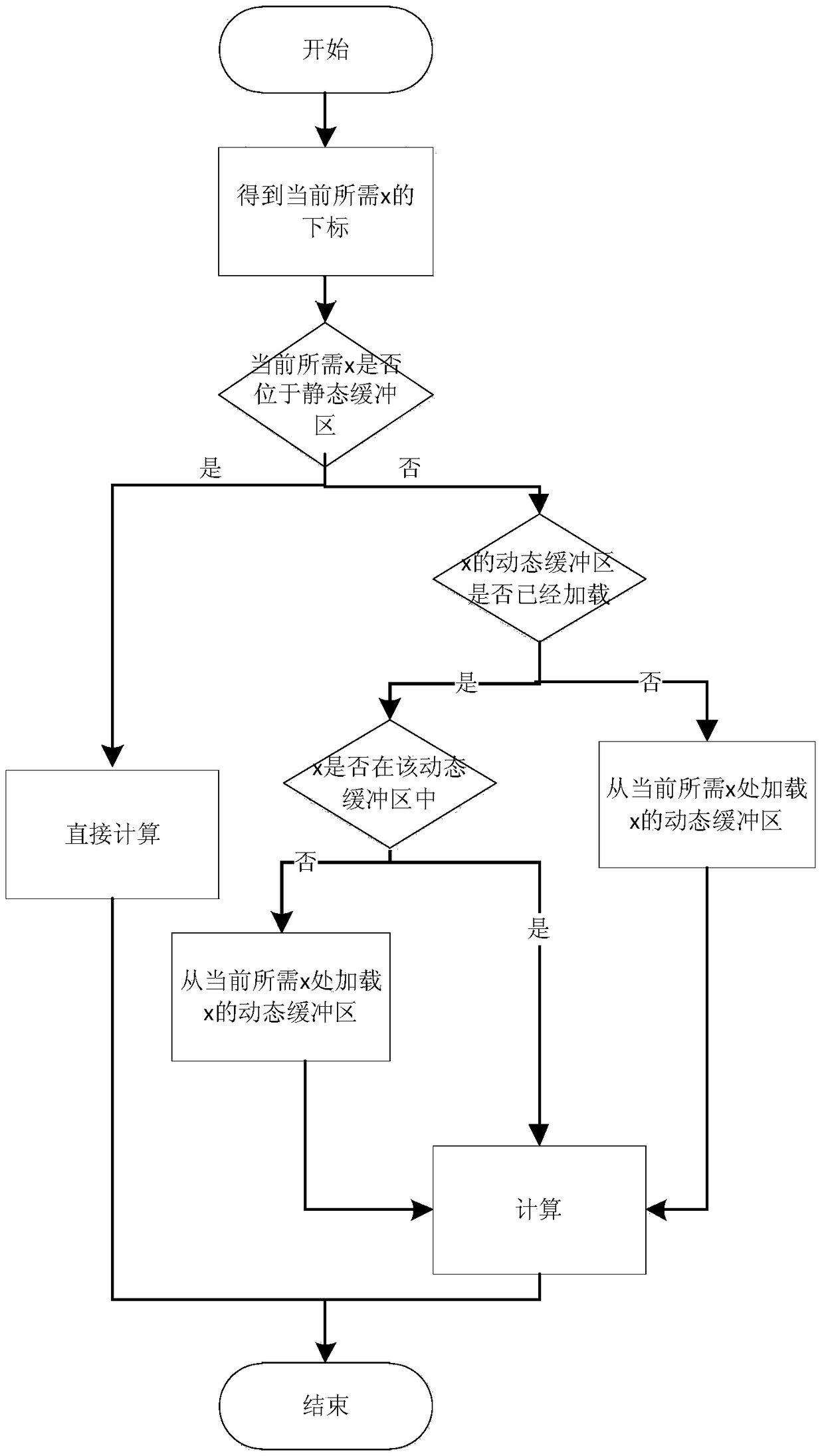

[0048] Such as figure 2 Shown, the specific realization of SpMV of the present invention is as follows:

[0049] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More