An electrostatic protection circuit, an array substrate, a display panel, and a display device

A static protection, array substrate technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of less paths, poor static effect, etc., and achieve the effect of improving the ability of static electricity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

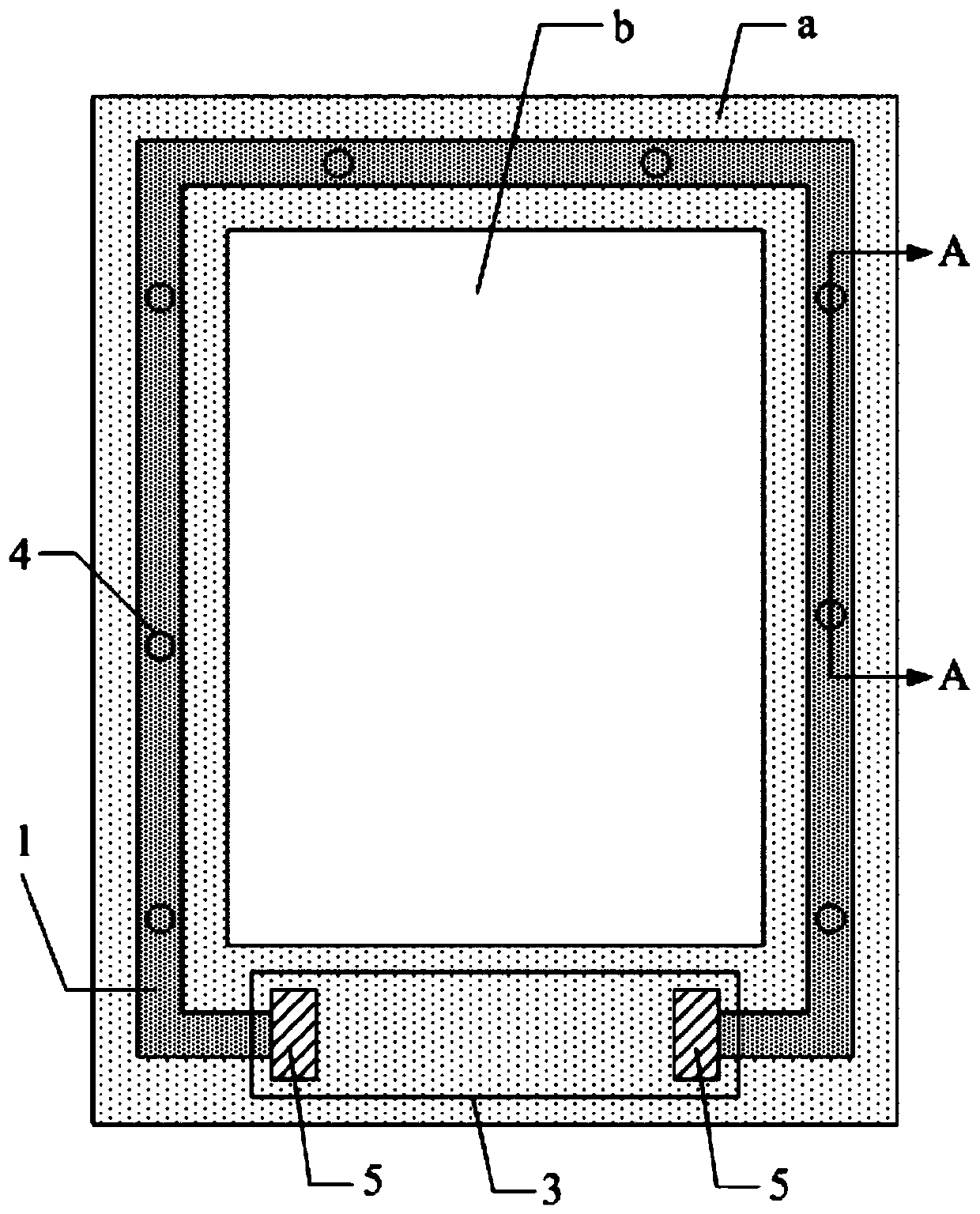

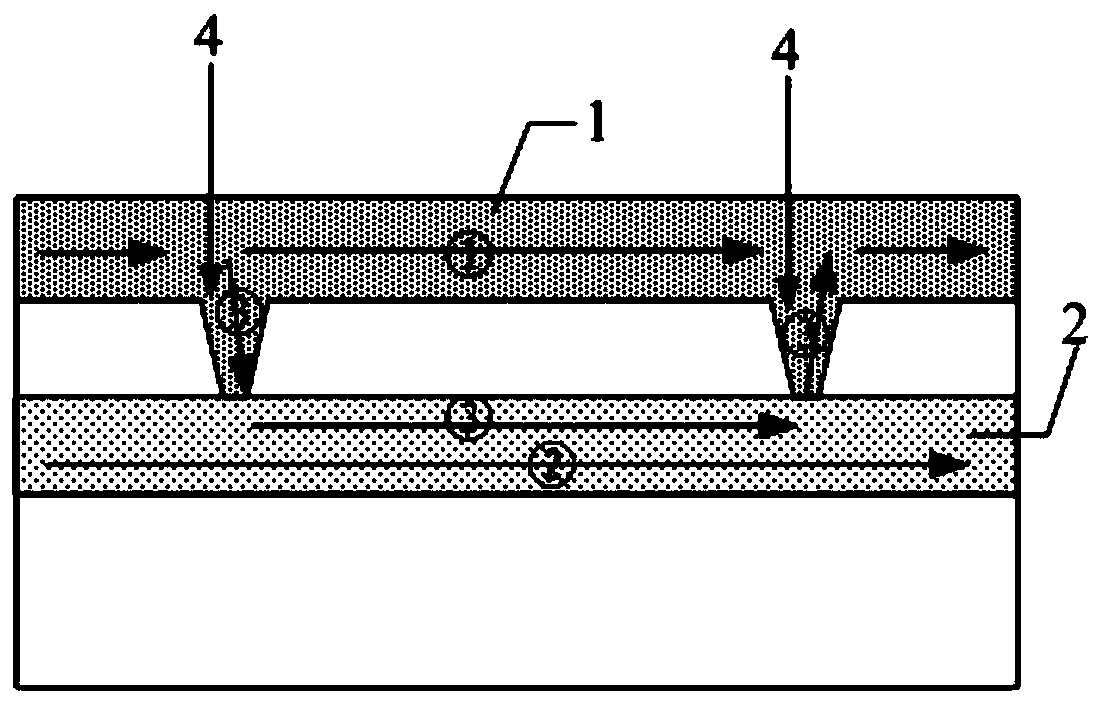

[0062] Example 1: The above electrostatic protection circuit provided by the embodiment of the present invention is applied to an array substrate of a thin film transistor with a top-gate structure, and the active layer, gate, and source (drain) of the thin film transistor are sequentially stacked on the array substrate superior.

[0063] In specific implementation, in the above-mentioned electrostatic protection circuit provided by the embodiment of the present invention, such as Figure 3a-Figure 3c as shown, Figure 3b for Figure 3a Sectional view along B1B1 direction, Figure 3c for Figure 3a A cross-sectional view along the B2B2 direction, the third ground line 6, the second ground line 2 and the first ground line 1 are sequentially stacked on the array substrate; as Figure 3b As shown, the second ground wire 2 has a third via hole 8 that runs through the film layer where the second ground wire 2 is located and has a diameter larger than that of the second via hole...

example 2

[0068]Example 2: The above electrostatic protection circuit provided by the embodiment of the present invention is applied to an array substrate of a thin film transistor with a top-gate structure, and the source (drain), active layer, and gate of the thin film transistor are sequentially stacked on the array substrate superior.

[0069] In specific implementation, the above-mentioned electrostatic protection circuit provided by the embodiment of the present invention, such as Figure 5a-5c as shown, Figure 5b for Figure 5a Sectional view along D1D1 direction, Figure 5c for Figure 5a In the cross-sectional view along the direction D2D2, the first ground wire 1, the third ground wire 6 and the second ground wire 2 are sequentially stacked on the array substrate; the above-mentioned electrostatic protection circuit provided by the embodiment of the present invention is as follows Figure 5b and Figure 5c As shown, it may also include: a fourth insulating layer 14 locat...

example 3

[0071] Example 3: The above electrostatic protection circuit provided by the embodiment of the present invention is applied to an array substrate of a thin film transistor with a bottom gate structure, and the gate, active layer, and source (drain) of the thin film transistor are sequentially stacked on the array substrate .

[0072] In specific implementation, in the above-mentioned electrostatic protection circuit provided by the embodiment of the present invention, such as Figure 6a-Figure 6c as shown, Figure 6b for Figure 6a Sectional view along E1E1 direction, Figure 6c for Figure 6a In the cross-sectional view along the E2E2 direction, the second ground line 2, the third ground line 6 and the first ground line 1 are sequentially stacked on the array substrate; Figure 6b and Figure 6c As shown, it may also include: a sixth insulating layer 16 located between the film layer where the first ground line 1 is located and the film layer where the third ground line ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More