Semiconductor package structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., and can solve problems such as structural strength influence and carrier reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

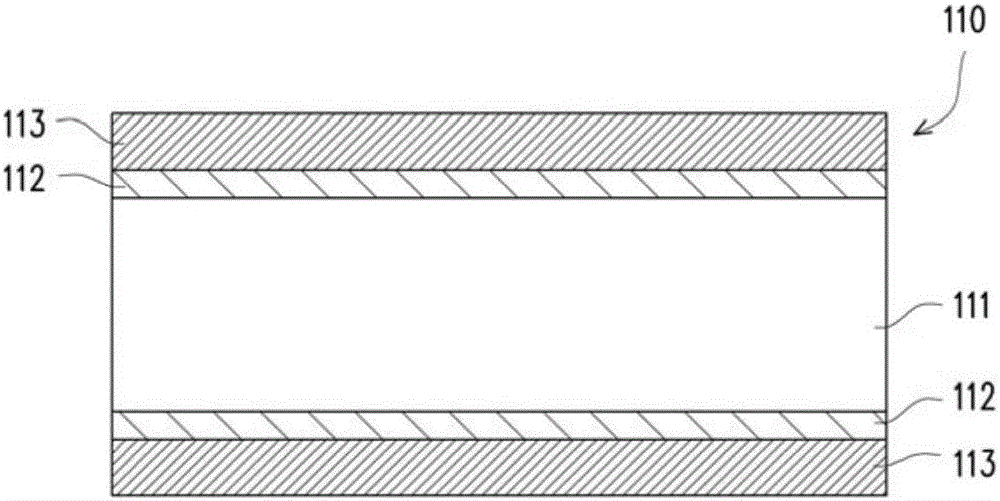

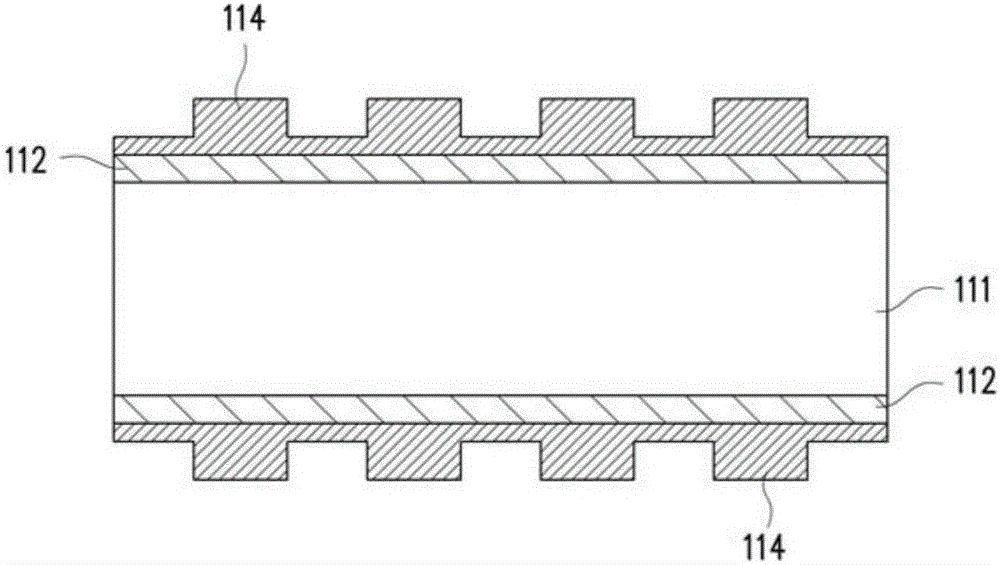

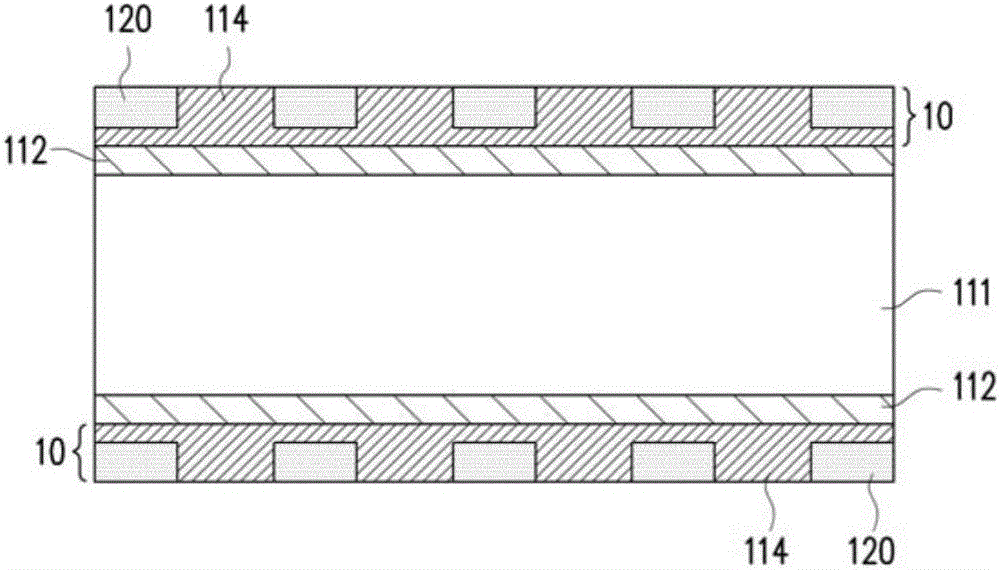

[0033] Figure 1A to Figure 1H It is a schematic cross-sectional view of the manufacturing process of the semiconductor package structure according to an embodiment of the present invention. First, please refer to Figure 1A , providing a packaging substrate 110 . The packaging substrate 110 includes a dielectric layer 111, a first metal layer 112 connected to the dielectric layer 111, and a second metal layer 113 connected to the first metal layer 112, wherein the first metal layer 112 is located between the dielectric layer 111 and the second metal layer Between 113. In this embodiment, the number of the first metal layer 112 and the number of the second metal layer 113 are two respectively. The aforementioned two first metal layers 112 are respectively located on opposite sides of the dielectric layer 111 , and each second metal layer 113 is connected to the corresponding first metal layer 112 . The material of the dielectric layer 111 can be silicon oxide, silicon nitri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More