High holding current ldmos structure for high voltage esd protection

An ESD protection and high-maintenance technology, which is applied in the field of electronic science and technology, can solve problems such as the threat of sophisticated integrated circuits and LDMOS damage, and achieve the effects of avoiding latch-up effects, improving robustness, and increasing sustaining current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

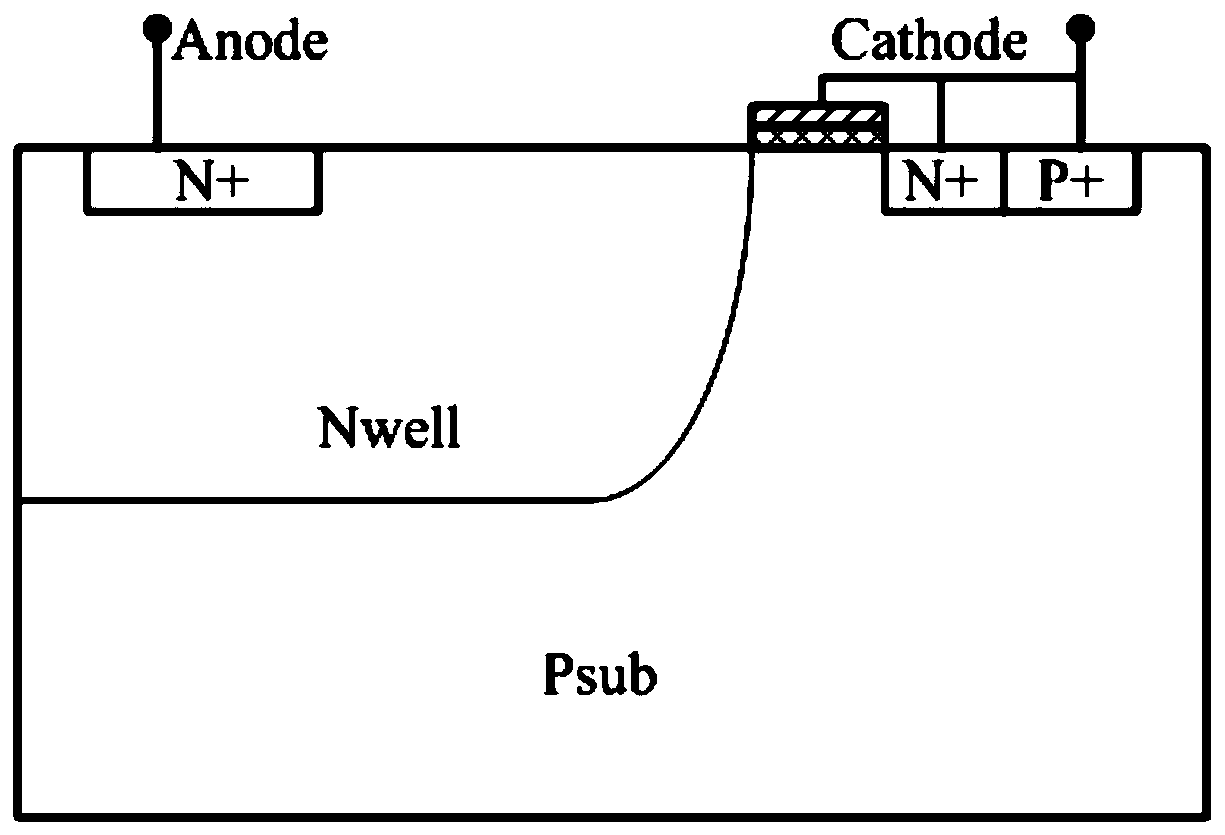

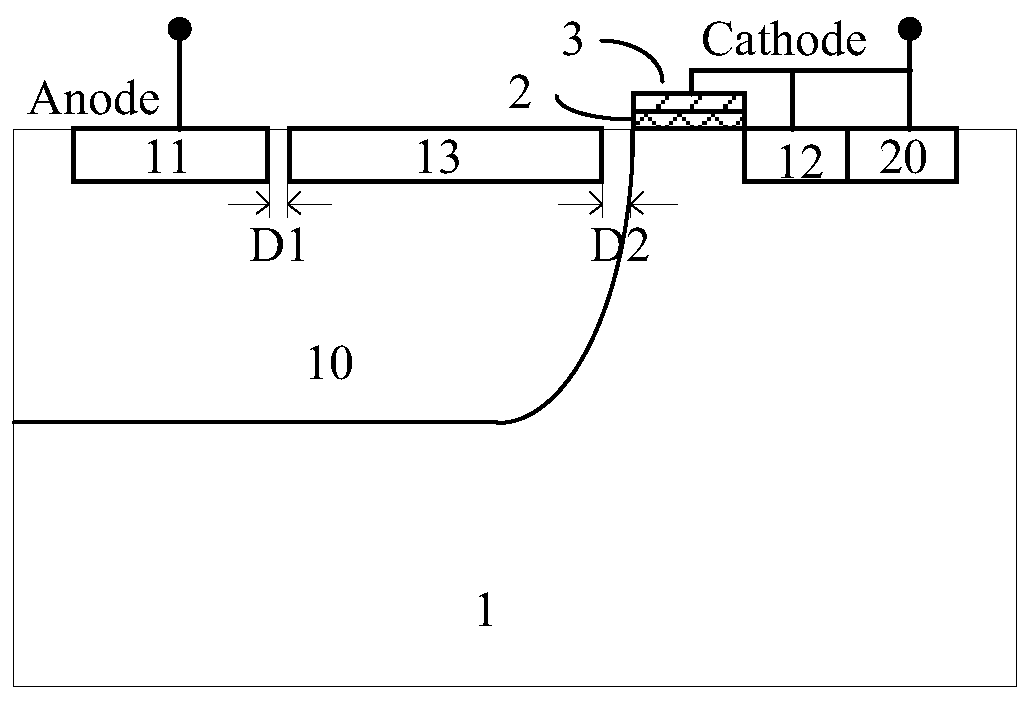

[0026] Such as figure 2 As shown, a high sustaining current LDMOS structure for high-voltage ESD protection includes a P-type substrate 1, an NWELL region 10 located on the surface of the P-type substrate, an NPLUS contact region 11 located inside the NWELL region, and the right side of the NWELL region 10 The thin gate oxide layer 2 on the surface of the P-type substrate whose side is tangential, the polysilicon gate electrode 3 located above the thin gate oxide layer 2, and the NPLUS source contact implanted on the P-substrate surface tangential to the right side of the thin gate oxide layer 2 Region 12, the PPLUS substrate 20 tangent to the right side of the NPLUS source contact region 12, the NTOP layer 13 located on the right side of the NPLUS contact region 11 inside the NWELL region 10, the distance between the left edge of the NTOP layer 13 and the right edge of the NPLUS contact region 11 D1, the distance between the right edge of the NTOP layer 13 and the right edge...

Embodiment 2

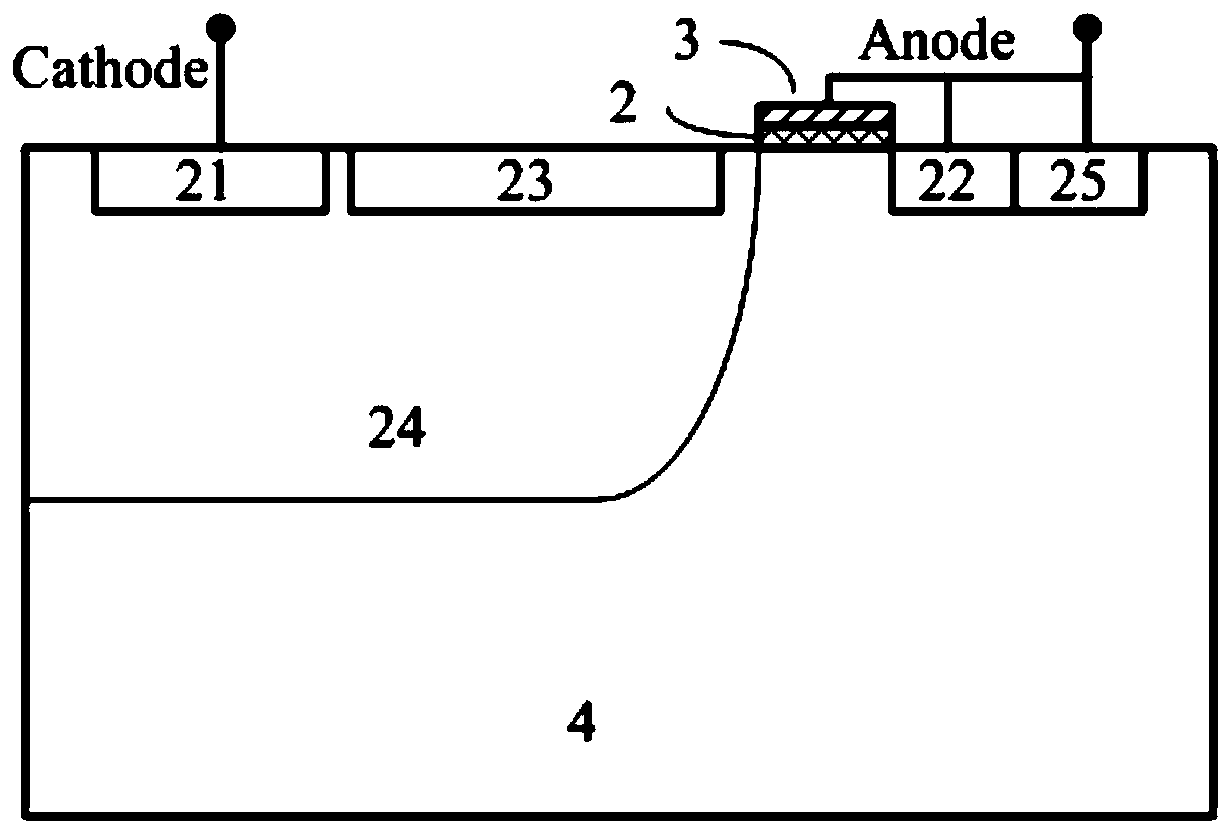

[0037] Such as image 3 As shown, a high sustaining current LDMOS structure for high-voltage ESD protection is different from Embodiment 1 in that: the NPLUS contact region 11 is replaced by the first PPLUS injection region 21, and the NPLUS source contact region 12 is replaced by The second PPLUS injection region 22, the NTOP layer 13 is replaced by a PTOP layer 23, the PPLUS substrate 20 is replaced by a substrate contact NPLUS region 25, the NWELL region 10 is replaced by a PWELL region 24, and the P-type substrate 1 is replaced by an N-type substrate 4, the first PPLUS implantation region 21 constitutes the cathode contact of the device, and the second PPLUS implantation region 22, the substrate contact NPLUS region 25, and the polysilicon gate electrode 3 are short-circuited to constitute the anode contact of the device.

[0038] The working principle of this embodiment is basically the same as that of Embodiment 1, the difference is that this embodiment additionally uses...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More