A kind of semiconductor device and its manufacturing method

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as fin top damage, fin damage, narrow fin damage, etc., and achieve high carrier migration Efficiency, improved performance, avoiding damage problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

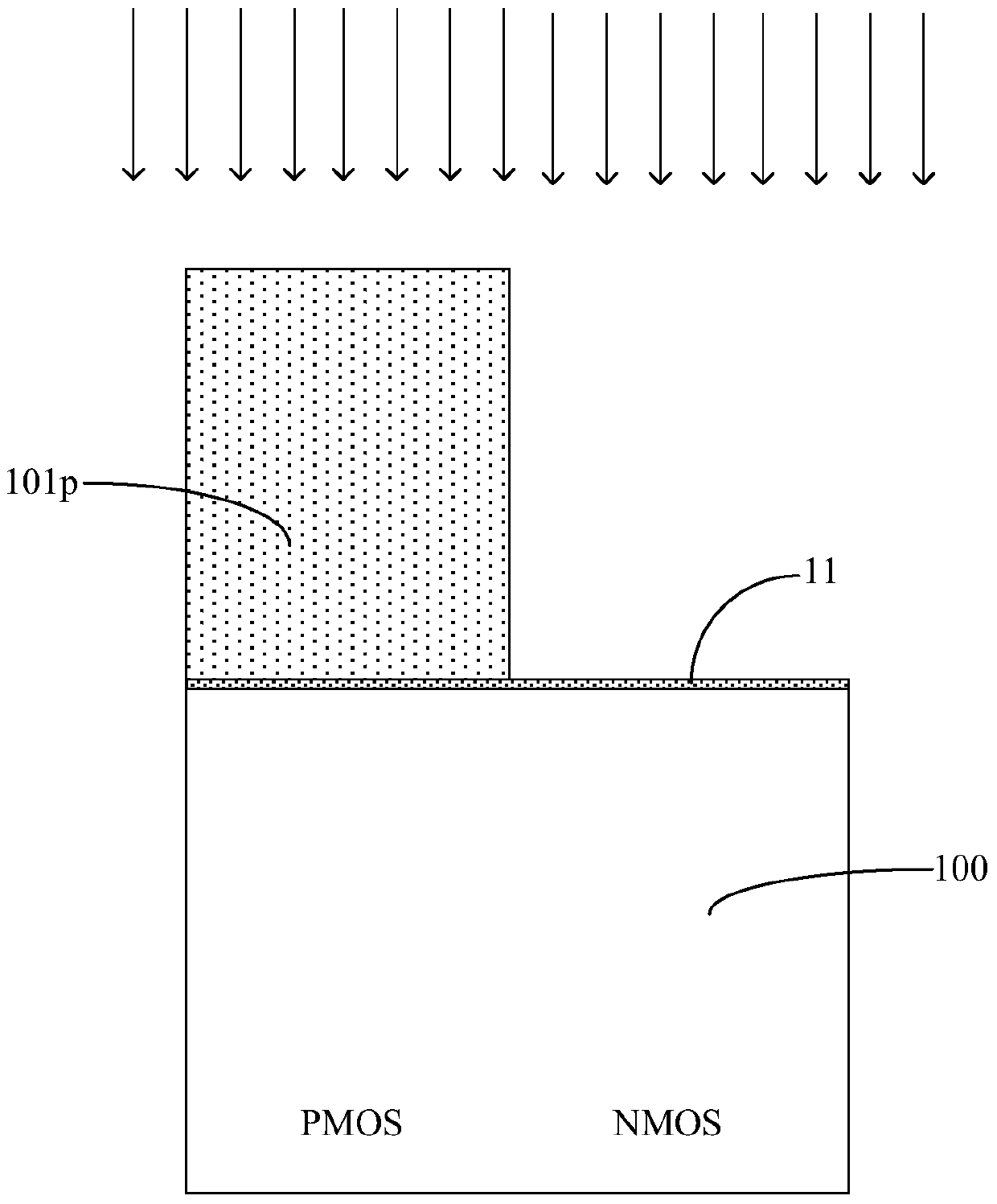

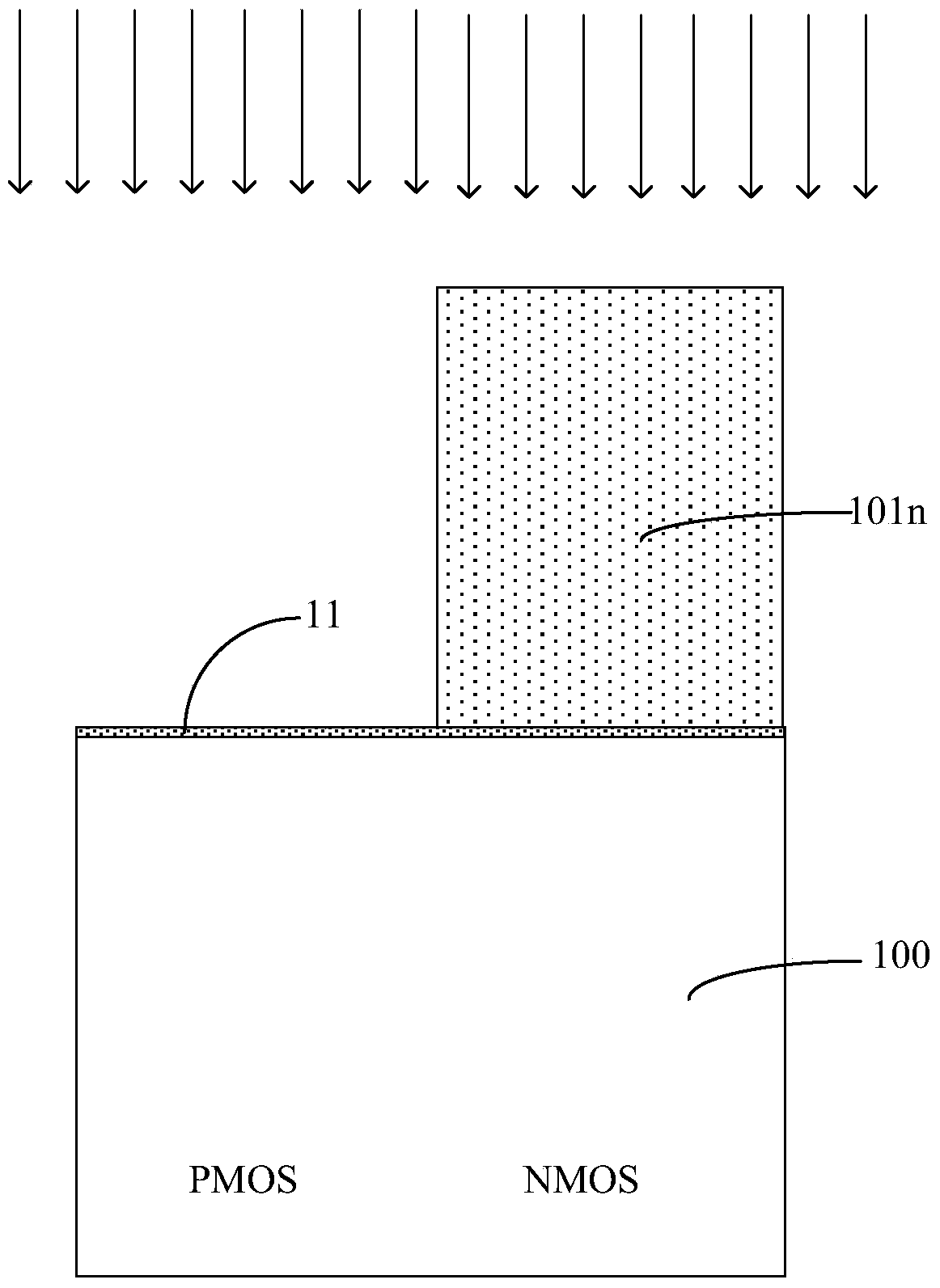

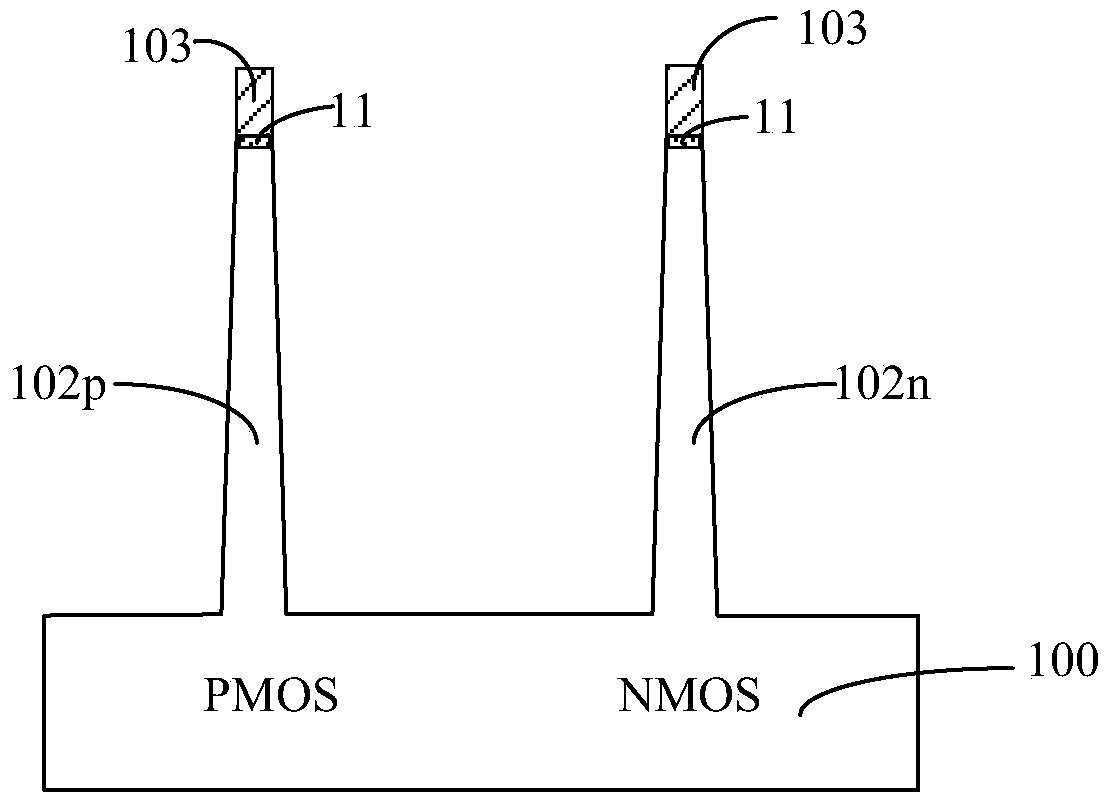

[0068] Below, refer to Figures 1A to 1O and figure 2 To describe a method for manufacturing a semiconductor device provided by an embodiment of the present invention. of which, 1A to Figure 1O A cross-sectional view of a structure formed by related steps of a method for manufacturing a semiconductor device according to an embodiment of the present invention; figure 2 It is a schematic flow chart of a method for manufacturing a semiconductor device according to an embodiment of the present invention.

[0069] Exemplarily, a method for manufacturing a semiconductor device according to an embodiment of the present invention includes the following steps:

[0070] First, step S201 is performed to provide a semiconductor substrate 100, the semiconductor substrate 100 includes a first region and a second region, and a first fin 102n is formed on the surface of the semiconductor substrate 100 corresponding to the first region , a second fin 102p is formed on the surface of the ...

Embodiment 2

[0129] The present invention also provides a manufacturing method of a semiconductor device. For details, refer to 3A to 3M and Figure 4 ,in, 3A to 3M and Figure 4 A cross-sectional view of a structure formed by related steps of a method for manufacturing a semiconductor device according to an embodiment of the present invention; Figure 4 It is a schematic flow chart of a method for manufacturing a semiconductor device according to another embodiment of the present invention.

[0130] Exemplarily, a method for manufacturing a semiconductor device according to an embodiment of the present invention includes the following steps:

[0131] First, step S401 is performed to provide a semiconductor substrate 300, the semiconductor substrate 300 includes a first region and a second region, and a first fin 302n is formed on the surface of the semiconductor substrate 300 corresponding to the first region , a second fin 302p is formed on the surface of the semiconductor substrat...

Embodiment 3

[0181] This embodiment also provides a semiconductor device obtained by using the manufacturing method in Embodiment 1, or a semiconductor device obtained by using the manufacturing method in Embodiment 2, and the semiconductor device may be a FinFET device.

[0182] The following reference Figure 3M The semiconductor device of the present invention will be described in detail.

[0183] The semiconductor device of the present invention includes: a semiconductor substrate 300, the semiconductor substrate 300 includes a first region and a second region, and a first well of a second conductivity type is formed in the semiconductor substrate corresponding to the first region , a second well of the first conductivity type is formed in the semiconductor substrate corresponding to the second region, a first fin 302n is formed on the surface of the semiconductor substrate corresponding to the first region, and A second fin 302p is formed on the surface of the semiconductor substrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More