Fan-out-type wafer-level packaging structure and preparation method therefor

A wafer-level packaging, fan-out technology, used in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., which can solve the problems of long flip-chip communication response time, packaging failure, offset and other problems , to achieve the effect of shortening communication response time, ensuring device performance, and increasing yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

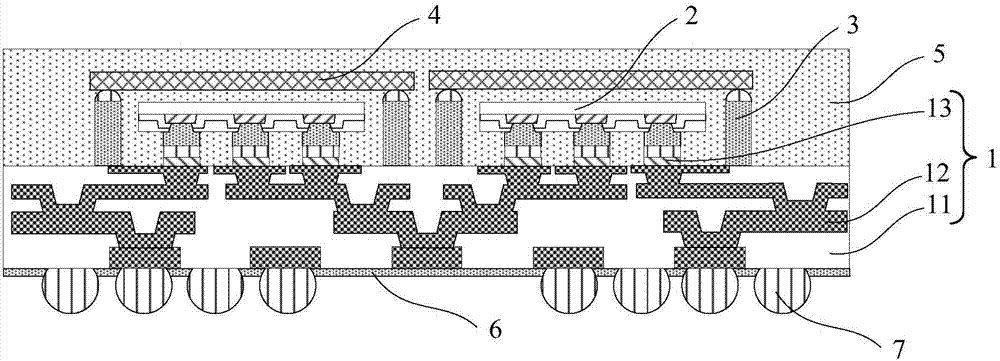

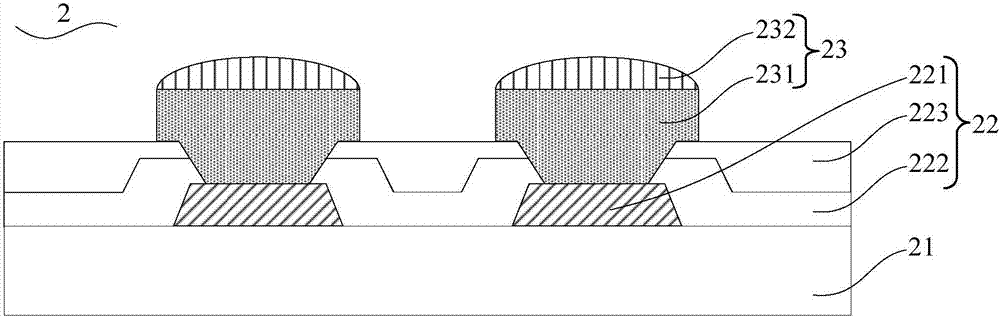

[0086] see figure 1 , the present invention provides a fan-out wafer level packaging structure, the fan-out wafer level packaging structure at least includes: a rewiring layer 1; a first flip chip 2, the first flip chip 2 bonding on the upper surface of the rewiring layer 1 and is electrically connected to the rewiring layer 1; a metal connecting column 3, the metal connecting column 3 is bonded to the upper surface of the rewiring layer 1, and is connected to the The rewiring layer 1 is electrically connected; the second flip chip 4, the second flip chip 4 is bonded to the upper surface of the metal connecting column 3, and is located above the first flip chip 2, the The second flip chip 4 is electrically connected to the rewiring layer 1 via the metal connecting column 3; the plastic sealing layer 5 is located on the upper surface of the rewiring layer 1 and fills the first Flip chip 2, the metal connecting column 3, the gap between the second flip chip 4 and the rewiring l...

Embodiment 2

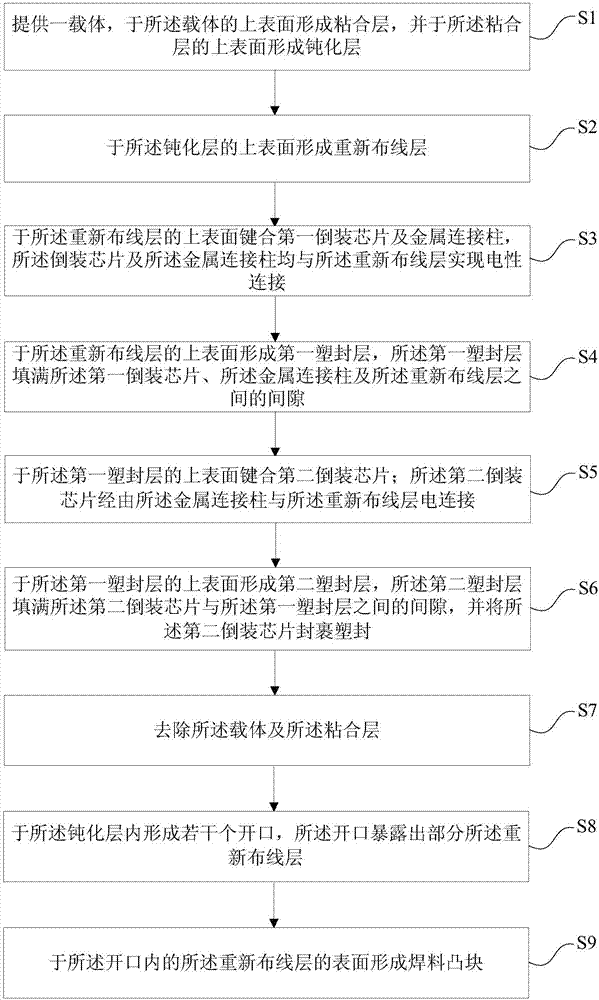

[0106] see image 3 , the present invention also provides a method for preparing a fan-out wafer-level packaging structure, the method for preparing a fan-out wafer-level packaging structure is suitable for preparing the fan-out wafer-level packaging as described in Embodiment 1 structure, the preparation method of the fan-out wafer level packaging structure at least includes the following steps:

[0107] S1: providing a carrier, forming an adhesive layer on the upper surface of the carrier, and forming a passivation layer on the upper surface of the adhesive layer;

[0108] S2: forming a rewiring layer on the upper surface of the passivation layer;

[0109] S3: bonding a first flip chip and a metal connecting post on the upper surface of the rewiring layer, and both the flip chip and the metal connecting post are electrically connected to the rewiring layer;

[0110] S4: forming a first plastic encapsulation layer on the upper surface of the rewiring layer, the first plasti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More