Thin-film transistor, preparation method thereof, array substrate and display panel

A technology for thin film transistors and array substrates, applied in the display field, can solve the problems of affecting the electrical properties of oxides in the channel region, poor working stability of TFTs, and poor shading effect in the channel region, etc., so as to improve illumination stability and work stability. , easy to achieve effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

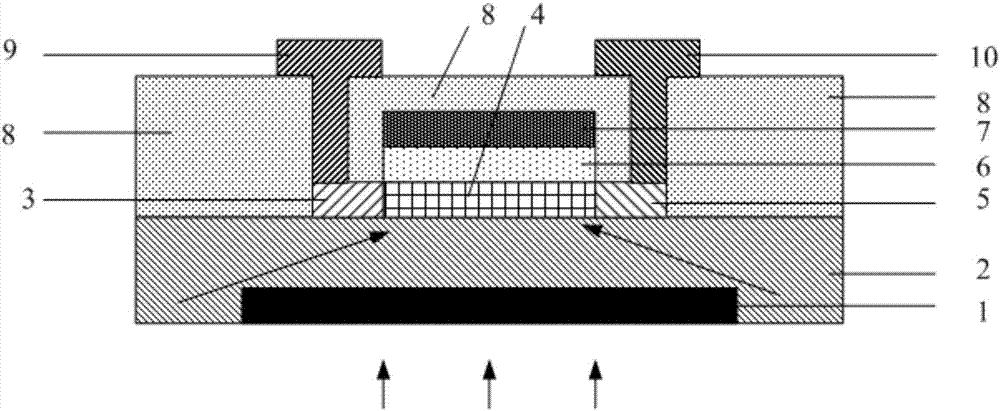

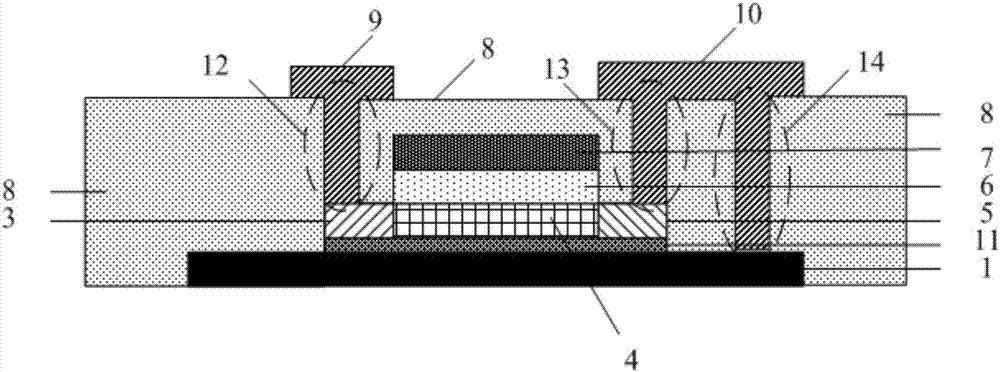

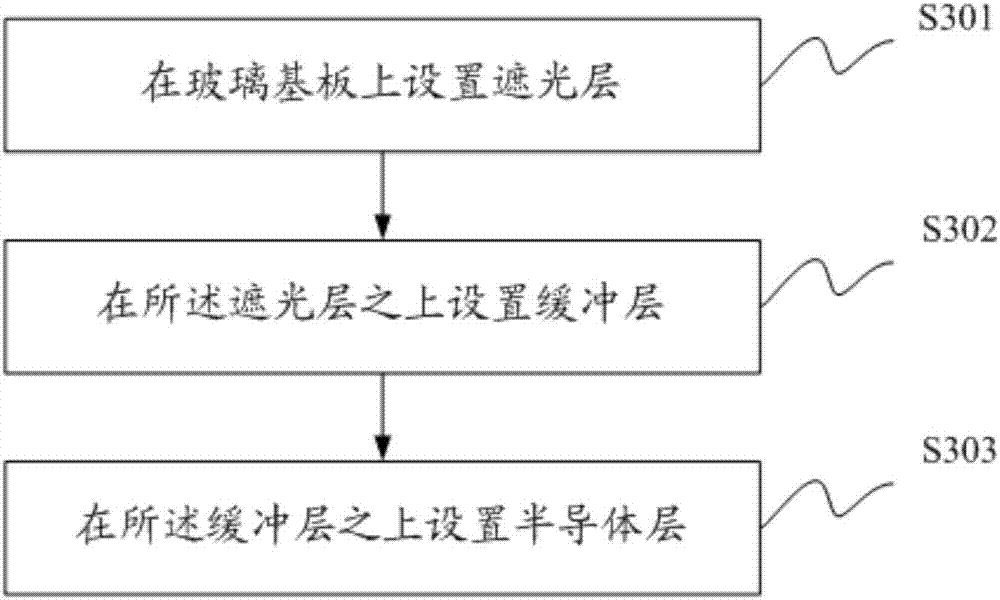

[0043] A method for preparing a thin film transistor provided in an embodiment of the present application, such as image 3 As shown, the method includes:

[0044] S301, setting a light-shielding layer on the glass substrate;

[0045] S302, setting a buffer layer on the light shielding layer;

[0046] S303, setting a semiconductor layer on the buffer layer;

[0047] The semiconductor layer includes three regions: a channel region, a first conductorized region and a second conductorized region formed through conductorization treatment, and in a direction parallel to the semiconductor layer, the channel region is located on the Between the first conductorized region and the second conductorized region; wherein, the thickness of the buffer layer is such that the light incident on the buffer layer cannot affect the first conductorized region, the channel region and the Second conductorized area.

[0048] Preferably, setting the light-shielding layer on the glass substrate spec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More