Binary and multi-valued memristor based on HfO2-x, preparation method, and application of binary and multi-valued memristor

A 1.8 is unfavorable for memristor integration, unable to meet the demanding requirements of special-purpose chips, and functional decline.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

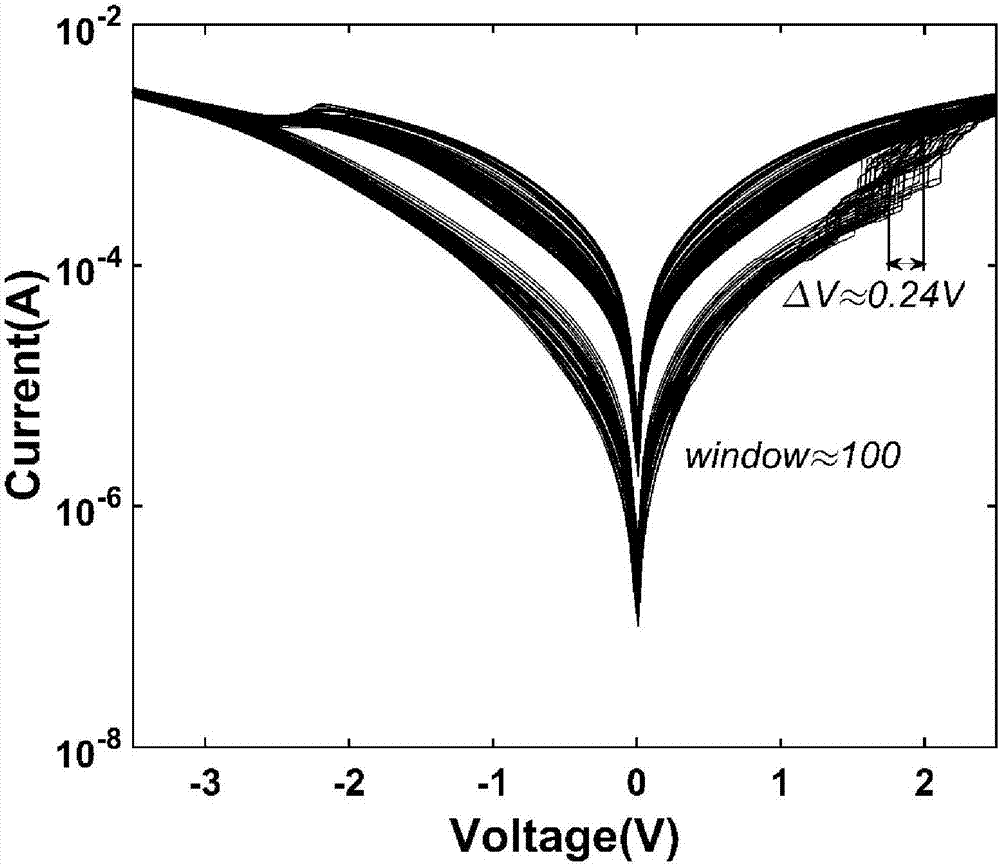

[0074] Example 1: Binary HfO 2-x Memristor

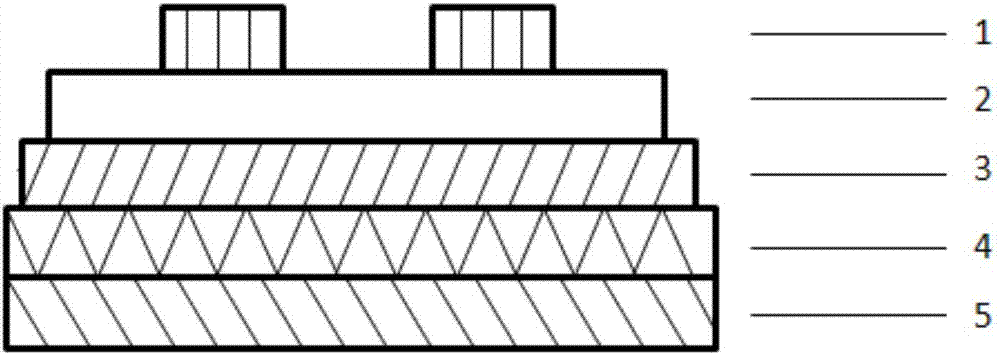

[0075] The binary HfO provided by embodiment 1 2-x Memristor, Pt / HfO with 8*8crossbar array structure x / Ti memristor, whose structure is as figure 1 shown; where the bottom electrode is Pt with a thickness of 100nm, and the functional layer is HfO with a thickness of 19.5nm 2-x , 2-x=1.93; the upper electrode is Ti with a thickness of 100nm.

[0076] The binary HfO of embodiment 1 is specifically described below 2-x The preparation method of memristor; Concrete steps are as follows:

[0077] (1) The first step: prepare the lower electrode:

[0078] (1.1) Photolithography: in the long SiO 2 One or more strip-shaped lower electrode patterns are prepared by a photolithography process on the Si substrate of the insulating layer;

[0079] Among them, the photolithography process includes: the steps of uniform glue, pre-baking, pre-exposure, post-baking, post-exposure, developing, coating, and stripping;

[0080] Sputtering: The...

Embodiment 2

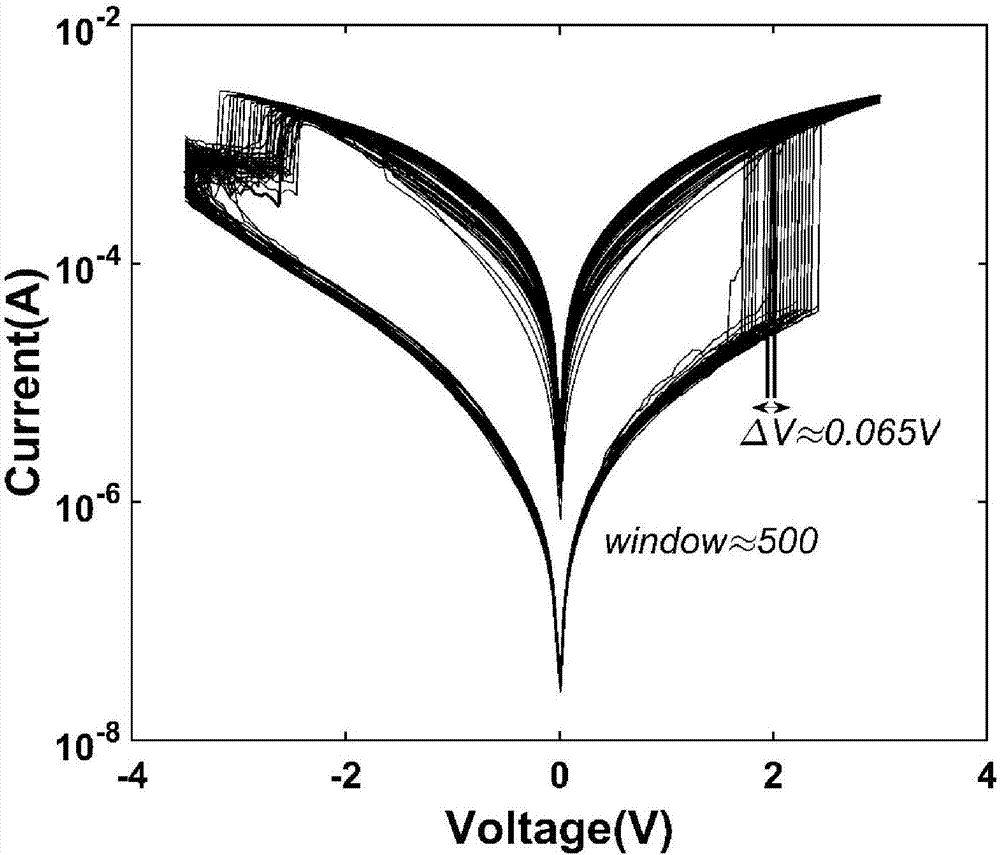

[0094] Example 2: Multivalued HfO 2-x Memristor

[0095] The multi-valued HfO provided by embodiment 2 2-x Memristor, Pt / HfO with 8*8crossbar array structure x / Ti memristor, whose structure is as figure 1 shown; where the bottom electrode is Pt with a thickness of 100nm, and the functional layer is HfO with a thickness of 19.5nm 2-x , 2-x=1.69; the upper electrode is Ti with a thickness of 100nm.

[0096] The multi-valued HfO of embodiment 2 is specifically described below 2-x The preparation method of memristor; Concrete steps are as follows:

[0097] (1) The first step: preparing the lower electrode;

[0098] (1.1) Photolithography: in the long SiO 2 One or more strip-shaped lower electrode patterns are prepared by a photolithography process on the Si substrate of the insulating layer;

[0099] Among them, the photolithography process includes: the steps of uniform glue, pre-baking, pre-exposure, post-baking, post-exposure, developing, coating, and stripping;

[01...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More