Annular field effect transistor (FET) device in matrix arrangement

A matrix arrangement and ring-shaped technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of gate delay, large area, electric field device breakdown, etc., to reduce gate delay, uniform electric field distribution, and improve modulation capability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

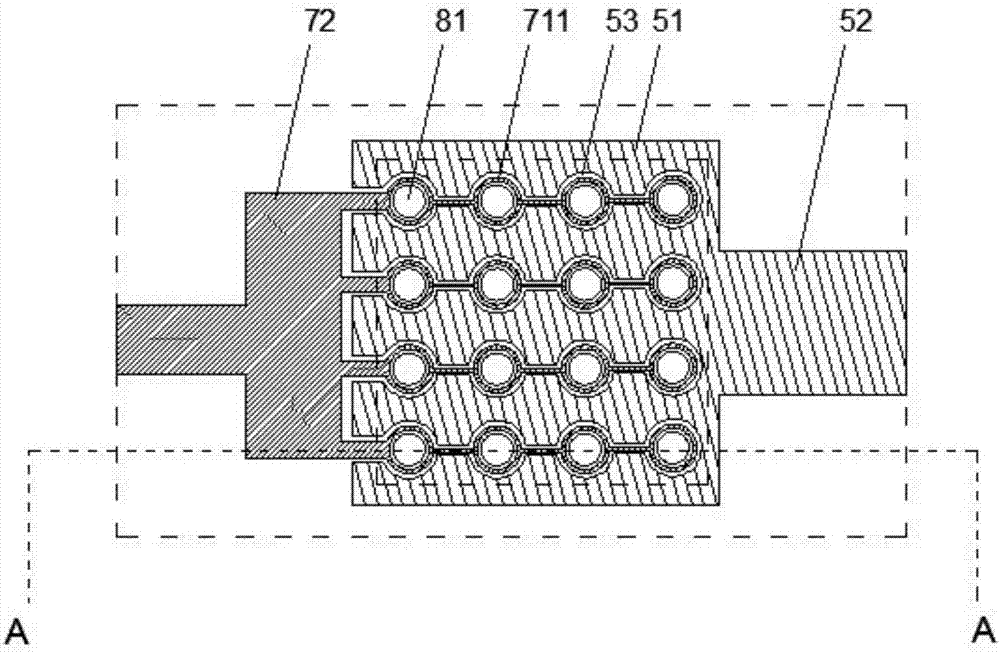

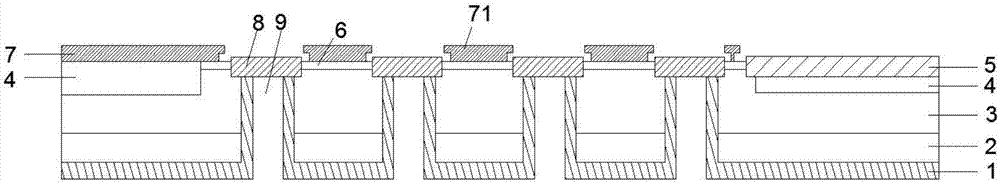

[0012] Such as figure 1 and image 3 As shown, this embodiment provides a matrix-arranged annular FET device, which includes a substrate 2, a buffer layer 3, and a barrier layer 6 from bottom to top; it also includes an annular isolation region 4, a gate 7, a source 8, and a drain 5. The annular isolation region 4 is formed on the surface of the barrier layer 6 and extends to the inside of the buffer layer 3, such as figure 1 As shown, between the two dotted lines is an annular isolation region 4; the source 8 is composed of 16 cylindrical source metals 81 arranged in a matrix, the array size is 4×4, and each source metal 81 is formed on the barrier Layer 6 extends above and bottom to buffer layer 3 . The gate 7 includes a first surrounding portion 71 and a first extending portion 72. The first surrounding portion 71 is composed of 16 closed rings 711 arranged in a matrix. The closed rings 711 are closed circular rings. The closed rings 711 and the source metal 81 One corre...

Embodiment 2

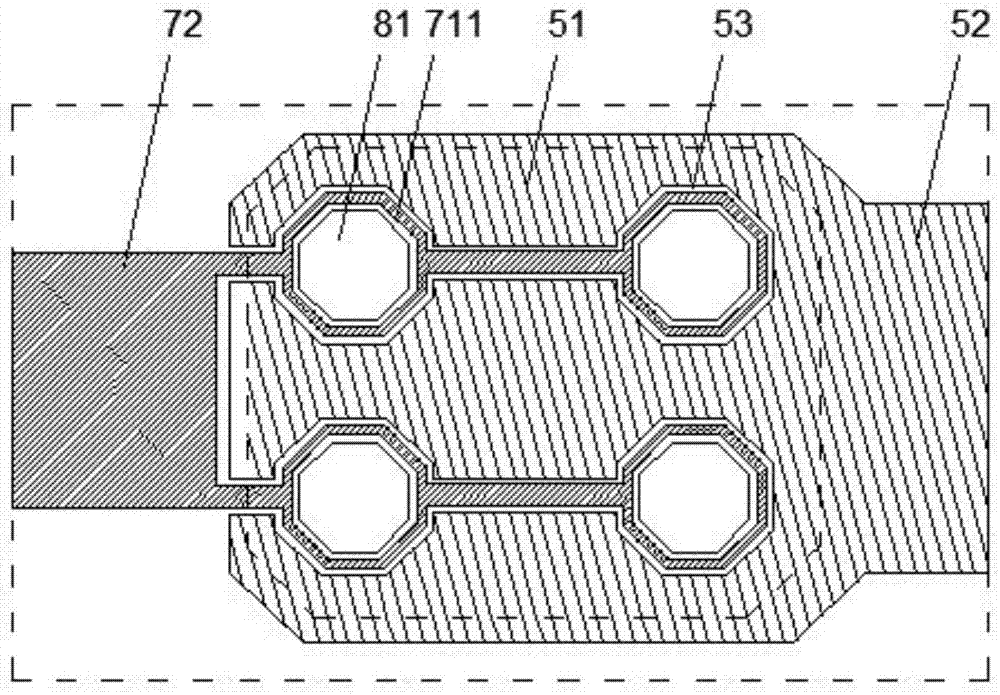

[0015] Such as figure 2 As shown, the source 8 of this embodiment is composed of four cylindrical source metals 81 arranged in a matrix, and the array size is 2×2; the first surrounding part 71 of the gate 7 is composed of four closed rings arranged in a matrix 711, the cross section of the closed ring 711 is a regular octagon; the second surrounding part 51 of the drain 5 has four through holes 53 arranged in a matrix, and the through holes 53 are regular octagonal holes; the outer part of the second surrounding part 51 The edge is an open octagon, and two openings are opened on one side of the second surrounding portion 51 ; four back holes 9 are opened upward from the bottom of the substrate 2 to the source metal 81 . Other structures are the same as in Embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com