Convolution, pooling and activation circuit based on resistive random access memory (RRAM) three-dimensional intersection array

A technology of resistive memory and cross array, applied in the field of semiconductor technology and neural network, can solve the problems of long processing time, large plane footprint, and high overhead of two-dimensional cross array of resistive memory, so as to reduce the plane footprint. Area, the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

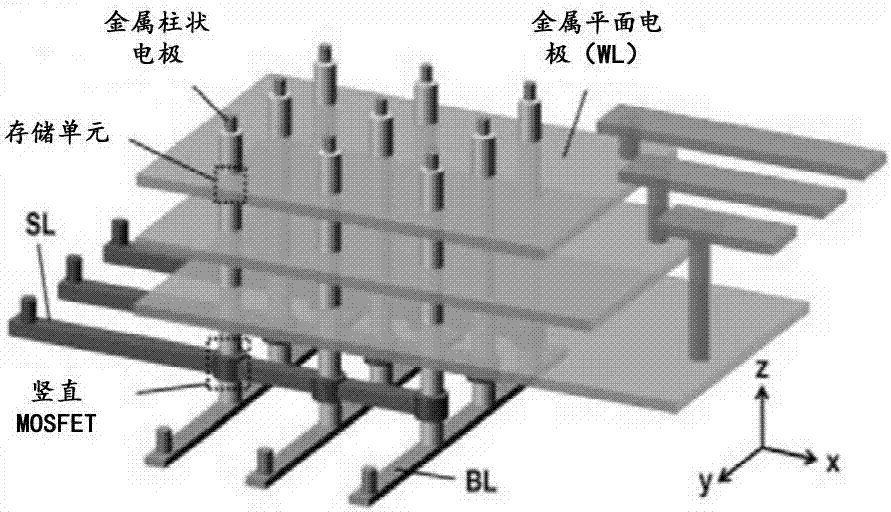

[0022] figure 1 A schematic structural diagram of a three-dimensional cross array of resistive memory used according to an embodiment of the present invention is shown.

[0023] Such as figure 1 As shown, the three-dimensional cross-point array of the RRAM used in the embodiment of the present invention uses a three-dimensional cross-point architecture (Cross-point Architecture).

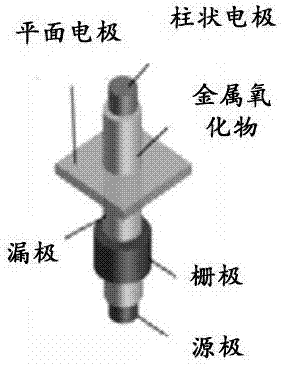

[0024] figure 2 A schematic structural diagram...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More