Memory training method and device

A memory and training value technology, applied in the field of memory training, can solve problems such as not satisfying batch production and small training value margin, and achieve the effect of satisfying memory compatibility and realizing batch production

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0023] figure 1 It is a flow chart of a memory training method provided in Embodiment 1 of the present invention, specifically including steps S101 to S103, detailed as follows:

[0024] S101. Initialize the memory controller.

[0025] Specifically, the memory controller is initialized so that the values of all registers of the memory controller are set to initial default values.

[0026] S102. Perform memory training on memory controller parameters, and complete memory training after finding a training value set of memory controller parameters that meets training requirements.

[0027] Specifically, the memory controller parameters are cyclically trained for multiple times. The memory training is to find the values of those memory controller parameters that can make the signal setup and hold time sufficient as the training value by adjusting the values of the memory controller parameters. , and after all the found training values are classified into the training val...

Embodiment 2

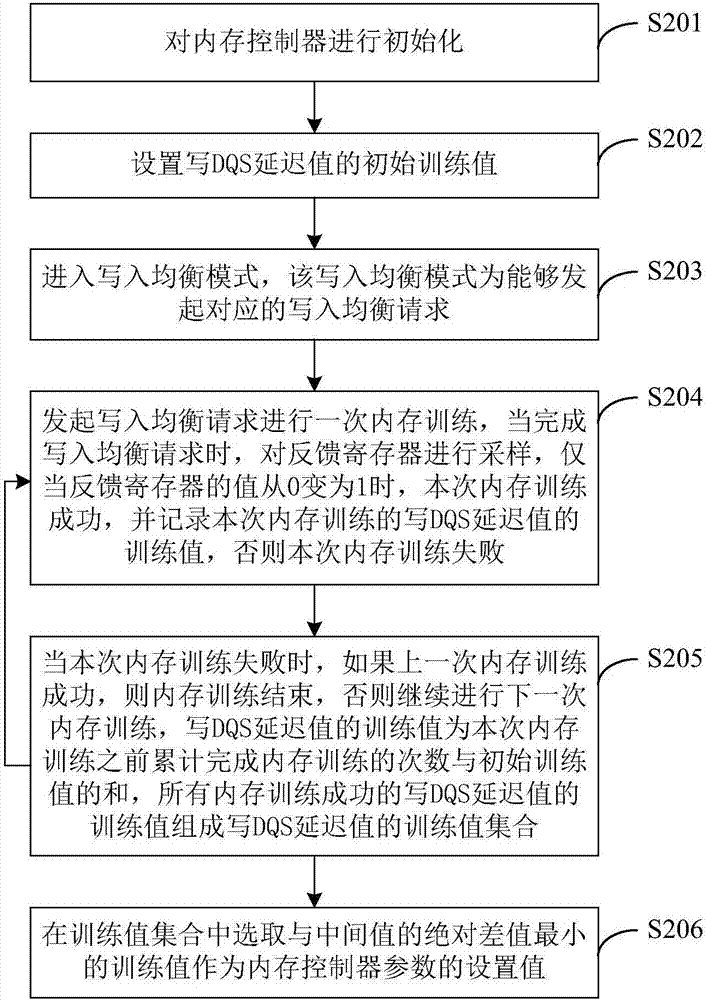

[0034] figure 2 It is a flow chart of a memory training method provided in Embodiment 2 of the present invention, specifically including steps S201 to S206, detailed as follows:

[0035] S201. Initialize the memory controller.

[0036] Specifically, the memory controller is initialized so that the values of all registers of the memory controller are set to initial default values.

[0037] S202. Set an initial training value of the write DQS delay value.

[0038] Specifically, the write DQS delay value is a memory controller parameter that requires memory training, and the initial training value of the write DQS delay value can be set to 0, that is, the memory training starts from the initial training value of 0.

[0039] S203. Enter a write balance mode, which is capable of initiating a corresponding write balance request.

[0040] The Write Leveling mode is capable of initiating corresponding write leveling requests for memory training.

[0041] Specifically, enter the...

Embodiment 3

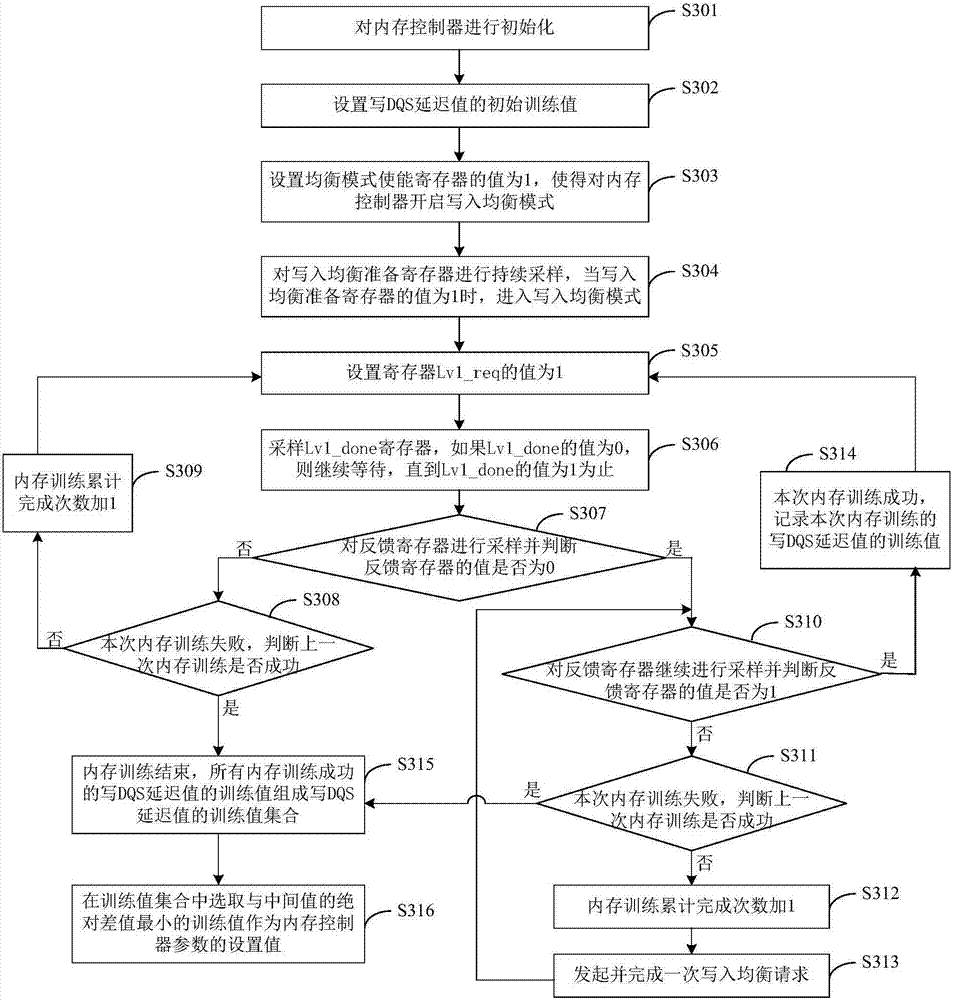

[0053] image 3 It is a flow chart of a memory training method provided in Embodiment 3 of the present invention, specifically including steps S301 to S308, detailed as follows:

[0054] S301. Initialize the memory controller.

[0055] Specifically, the memory controller is initialized so that the values of all registers of the memory controller are set to initial default values.

[0056] It should be noted that the specific registers involved in this embodiment are all based on the domestic Loongson platform.

[0057] S302. Set an initial training value of the write DQS delay value.

[0058] Specifically, the write DQS delay value is a memory controller parameter that requires memory training, and the initial training value of the write DQS delay value can be set to 0, that is, the memory training starts from the initial training value of 0.

[0059] S303. Set the value of the balance mode enable register to 1, so that the write balance mode is enabled for the memory con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More