Correction circuit for error detection and correction technology

A correction circuit and error detection technology, which is applied in the direction of error detection/correction, response error generation, electrical digital data processing, etc., can solve the problem of increased complexity of timing control circuit design, error detection and correction technology, and hardware consumption of correction circuits Advanced problems, to achieve the effect of eliminating glitches, reducing hardware overhead, and reducing hardware consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is only some embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

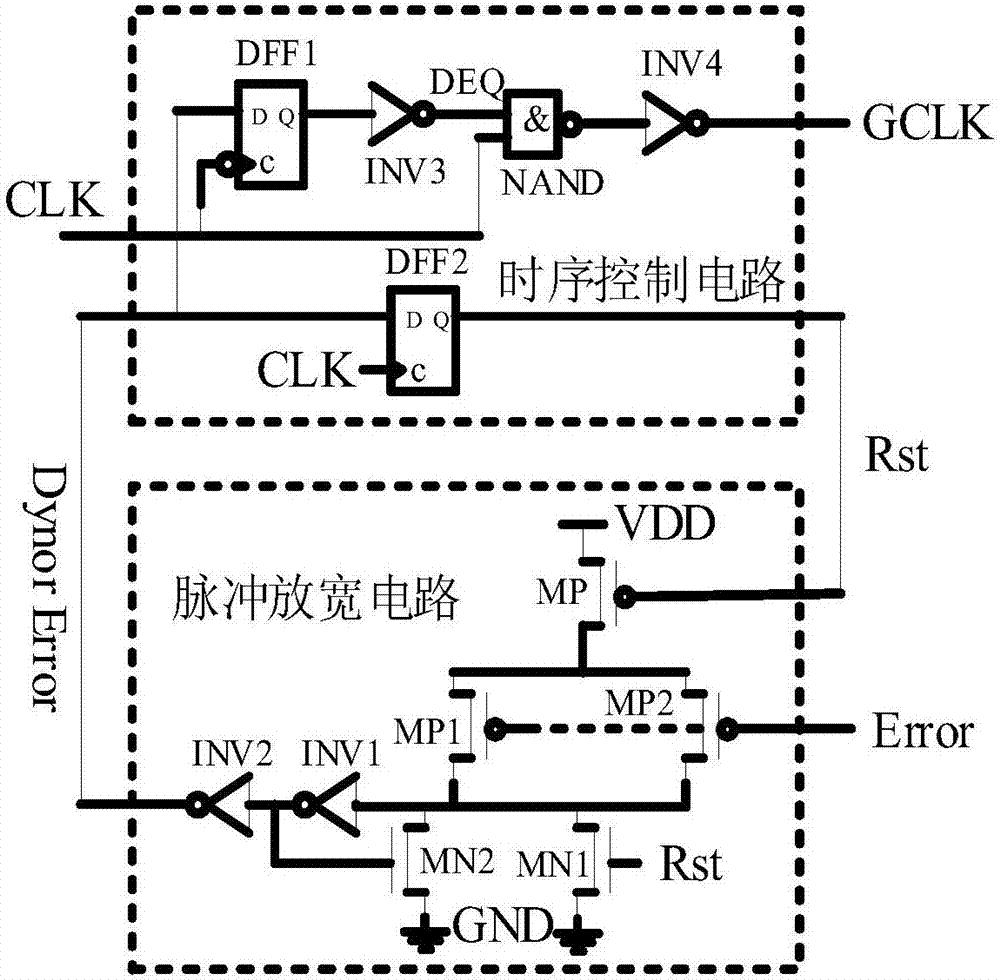

[0029] The present invention provides a correction circuit for error detection and correction techniques. figure 1 A schematic structural diagram of an EDAC technology correction circuit module is shown in an embodiment of the present invention. As shown in the figure, the EDAC technology correction circuit module of an embodiment of the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More