Laterally diffused MOS device

A MOS device, lateral double diffusion technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of substrate-assisted depletion, depletion by the substrate, unable to achieve the optimization of the electric field in the drift region, etc. The effect of uniform distribution of blocking voltage and electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

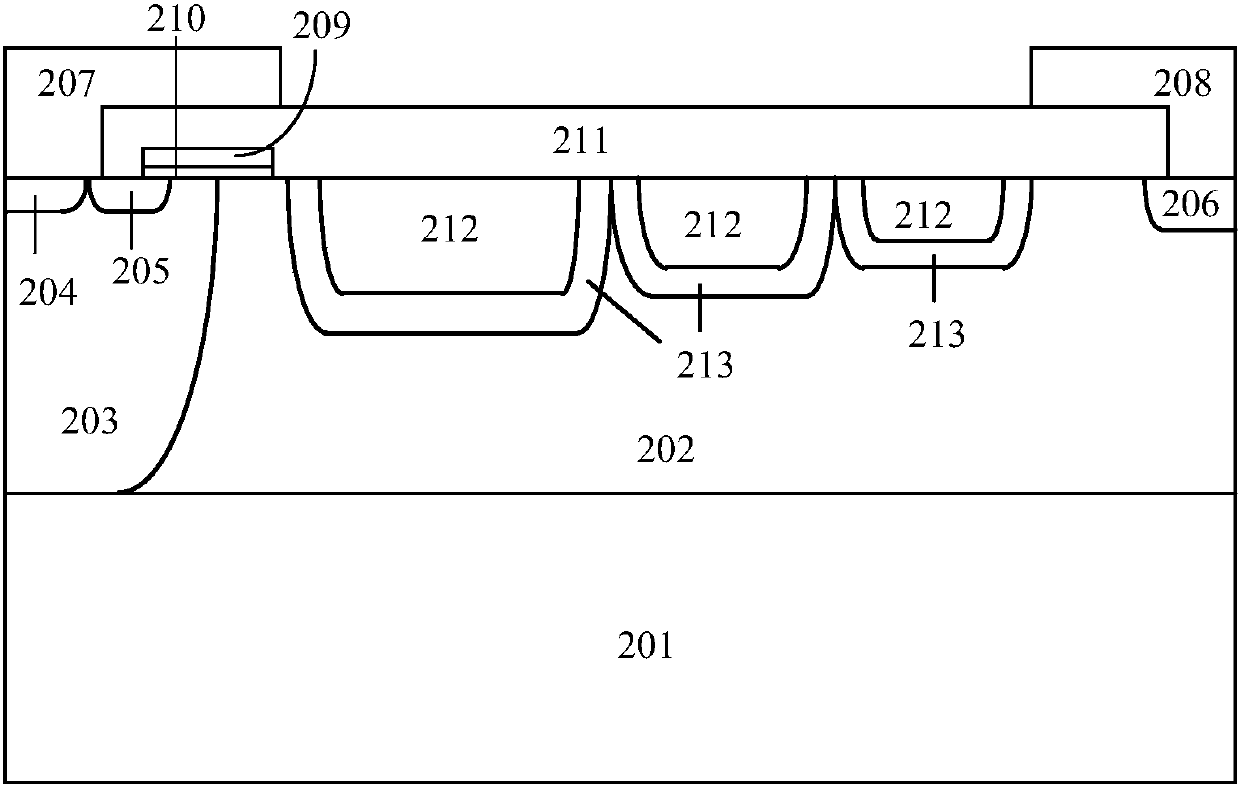

[0016] In this embodiment, the semiconductor of the first conductivity type is a P-type semiconductor, the semiconductor of the second conductivity type is an N-type semiconductor, and the charges stored in the polysilicon island 212 are negative charges.

[0017] A kind of lateral double diffusion MOS device, comprises P-type semiconductor substrate 201 and the P-type semiconductor body region 203 and N-type semiconductor drift region 202 that are arranged on the upper surface of P-type semiconductor substrate 201, P-type semiconductor body region 203 and N-type The semiconductor drift region 202 is side contacted; the inner upper surface of the P-type semiconductor body region 203 has an N-type semiconductor source region 205 and a highly doped P-type semiconductor body contact region 204; the N-type semiconductor source region 205 and the highly doped P The P-type semiconductor body contact region 204 is in direct contact with the metal source 207 located on its upper surfac...

Embodiment 2

[0023] In this embodiment, the semiconductor of the first conductivity type is an N-type semiconductor, the semiconductor of the second conductivity type is a P-type semiconductor, and the charges stored in the polysilicon island 212 are positive charges.

[0024]A lateral double-diffused MOS device, comprising an N-type semiconductor substrate 201 and an N-type semiconductor body region 203 and a P-type semiconductor drift region 202 arranged on the upper surface of the N-type semiconductor substrate 201, and an N-type semiconductor body region 203 and a P-type semiconductor region. The semiconductor drift region 202 is side contacted; the upper surface of the N-type semiconductor body region 203 has a P-type semiconductor source region 205 and a highly doped N-type semiconductor body contact region 204; the P-type semiconductor source region 205 and the highly doped N The N-type semiconductor body contact region 204 is in direct contact with the metal source 207 located on it...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More