Trench epitaxy filling method

A filling method and trench technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems affecting device performance and other issues, and achieve the effect of reducing the amount of lateral etching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

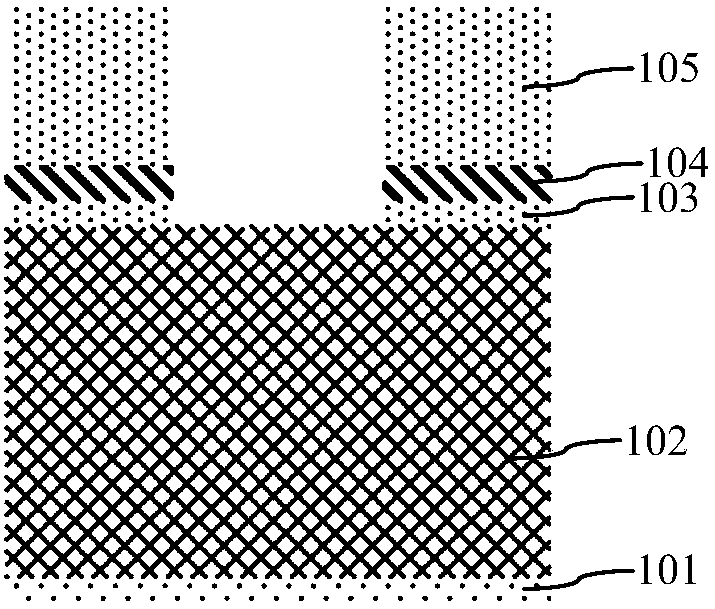

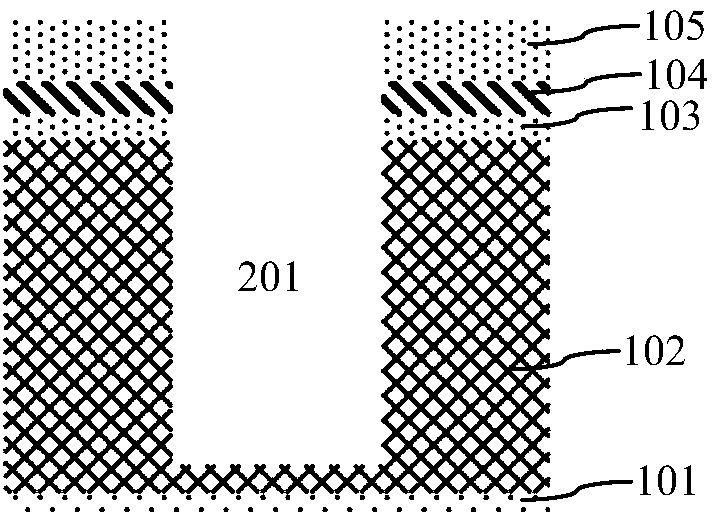

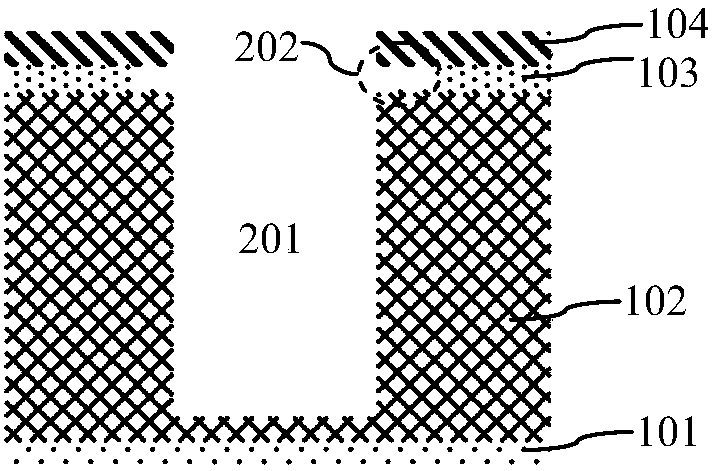

[0041] Such as figure 2 Shown is the flow chart of the filling method of trench epitaxy in the embodiment of the present invention; as Figure 3A to Figure 3I As shown, it is a schematic diagram of the device structure in each step of the filling method of the trench epitaxy in the embodiment of the present invention. The filling method of the trench epitaxy in the embodiment of the present invention includes the following steps:

[0042] Step 1, such as Figure 3A As shown, a hard mask layer formed by stacking the first oxide layer 3 , the second nitride layer 4 and the third oxide layer 5 is formed on the surface of the semiconductor substrate 1 .

[0043] In the embodiment of the present invention, the first epitaxial layer 2 is formed on the surface of the semiconductor substrate 1 , and the subsequent trench 301 is formed in the first epitaxial layer 2 . The trench 301 is a super junction trench. The first epitaxial layer 2 has a first conductivity type, and the subse...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More