A test method for bias temperature instability applied to MOS devices

A MOS device, instability technology, applied in the direction of single semiconductor device testing, instrumentation, measuring electricity, etc., can solve the problem of inaccurate testing of bias temperature instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

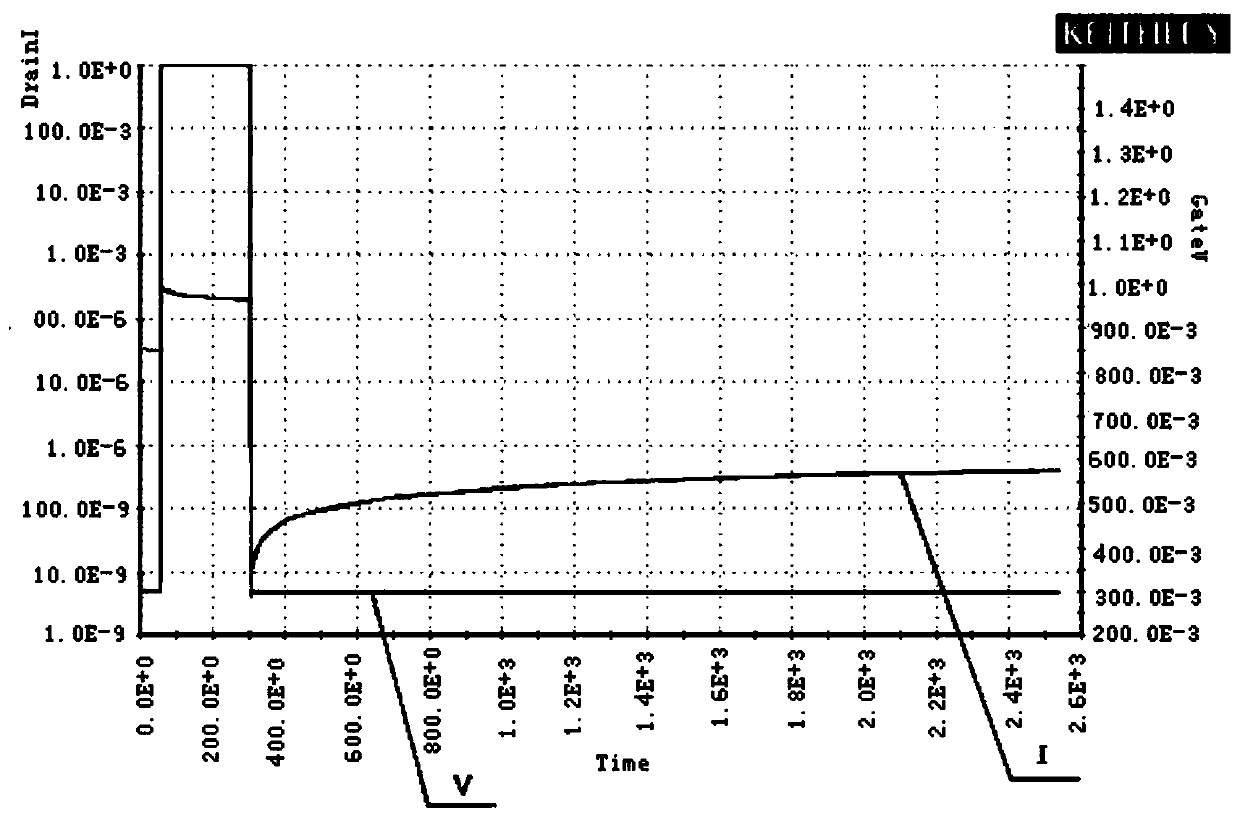

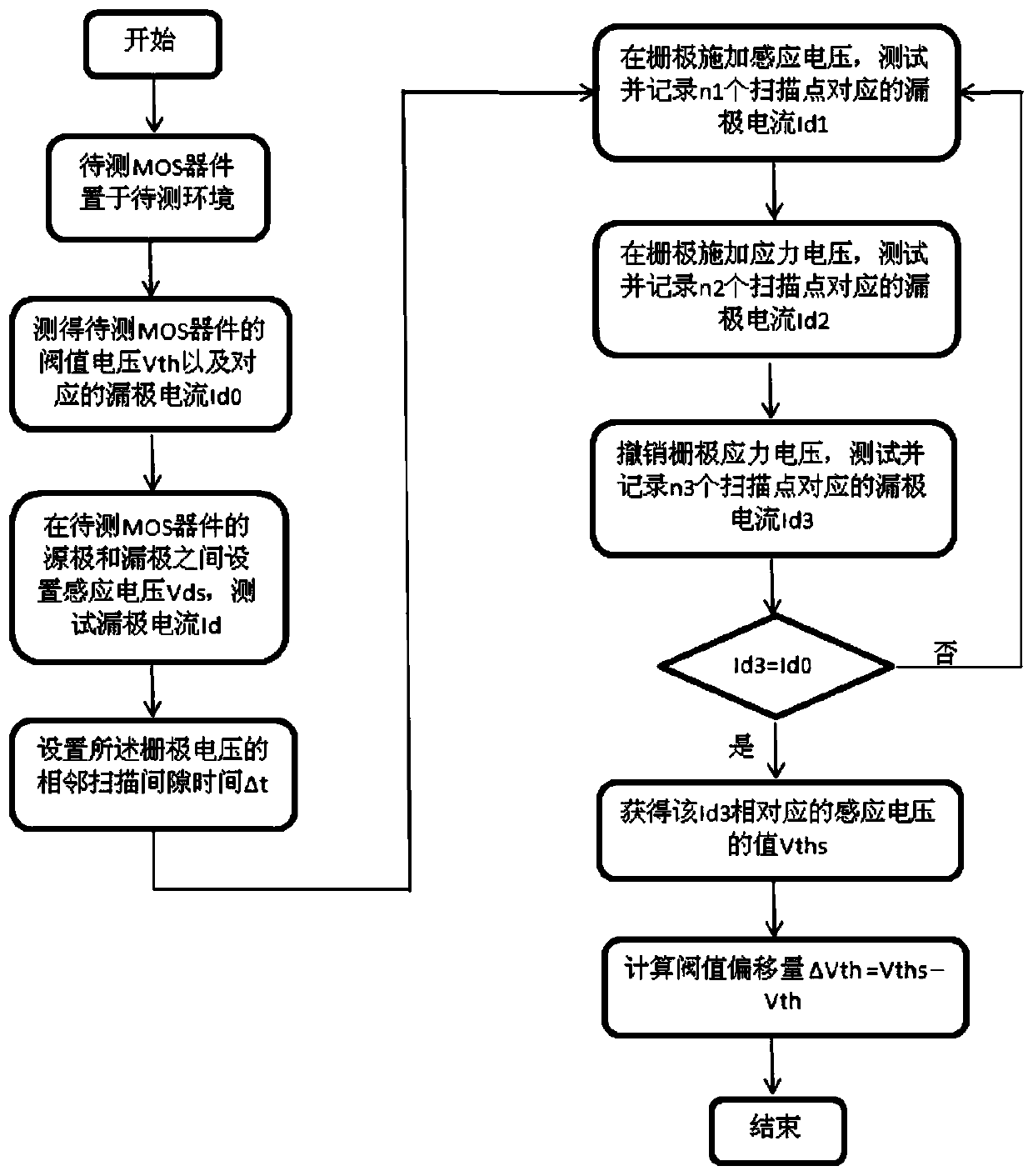

[0028] like figure 1 and figure 2 As shown, this embodiment provides a method for testing bias temperature instability applied to MOS devices, comprising the following steps:

[0029] 1. Place the MOS device to be tested in the test environment, scan the gate voltage from -1V to 1V, scan to obtain the original transfer characteristic curve of the MOS device to be tested, adjust the gate voltage, according to the original transfer characteristic curve It is determined that the MOS device to be tested is in a normal working state, and the threshold voltage Vth and the corresponding drain current Id of the gate of the MOS device to be tested are measured 0 ;

[0030] 2. According to the electrical characteristics of the device, an induced voltage Vds is set between the source and the drain of the MOS device to be tested, and the drain current Id is tested; in the present embodiment, Vds=0.05V;

[0031] 3. The substrate and the source end of the MOS device are set to be ground...

Embodiment 2

[0040] like figure 1 and figure 2 As shown, this embodiment provides a method for testing bias temperature instability applied to MOS devices, comprising the following steps:

[0041] 1. Place the MOS device to be tested in the test environment, scan the gate voltage from -1v to 1v, scan to obtain the original transfer characteristic curve of the MOS device to be tested, adjust the gate voltage, according to the original transfer characteristic curve It is determined that the MOS device to be tested is in a normal working state, and the threshold voltage Vth and the corresponding drain current Id of the gate of the MOS device to be tested are measured 0 ;

[0042]2. According to the electrical characteristics of the device, an induced voltage Vds is set between the source and the drain of the MOS device to be tested, and the drain current Id is tested; in the present embodiment, Vds=0.05V;

[0043] 3. The substrate and the source end of the MOS device are set to be grounde...

Embodiment 3

[0052] like figure 1 and figure 2 As shown, this embodiment provides a method for testing bias temperature instability applied to MOS devices, comprising the following steps:

[0053] 1. Place the MOS device to be tested in the test environment, scan the gate voltage from -1v to 1v, scan to obtain the original transfer characteristic curve of the MOS device to be tested, adjust the gate voltage, according to the original transfer characteristic curve It is determined that the MOS device to be tested is in a normal working state, and the threshold voltage Vth and the corresponding drain current Id of the gate of the MOS device to be tested are measured 0 ;

[0054] 2. According to the electrical characteristics of the device, the induced voltage Vds is set between the source and the drain of the MOS device to be tested, and the drain current Id is tested; Vds=0.05V in the present embodiment;

[0055] 3. Both the substrate and the source of the MOS device are grounded;

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More