Fin field effect transistor and method of forming the same

A technology of fin field effect transistors and fins, which is applied in the direction of transistors, semiconductor devices, electrical components, etc., to achieve the effects of excellent quality, excellent lattice quality, and avoiding lattice damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

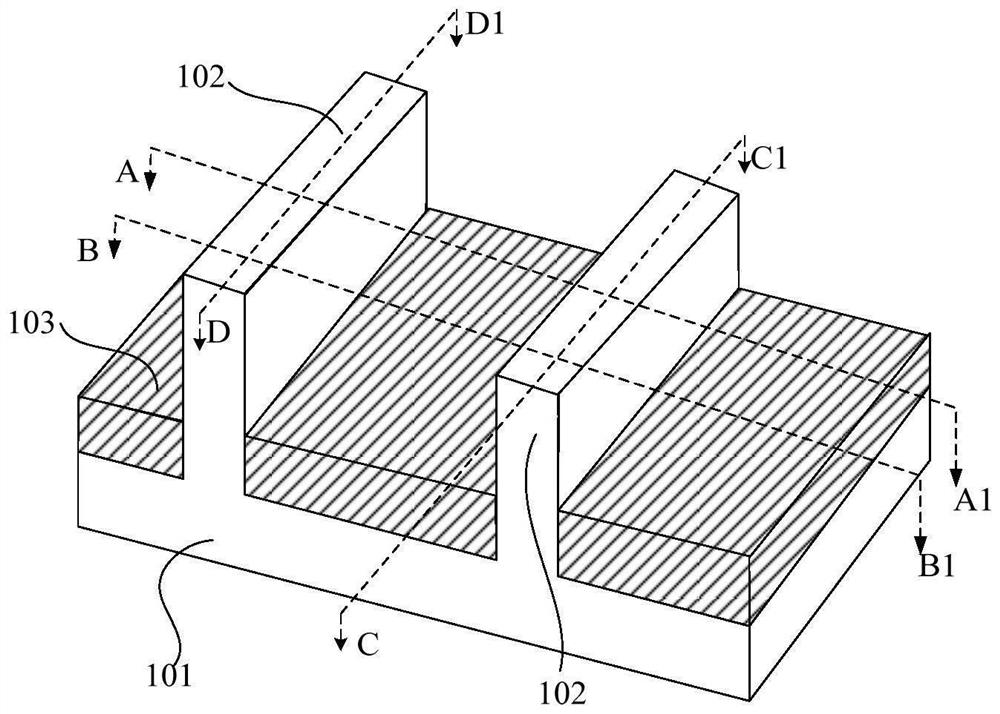

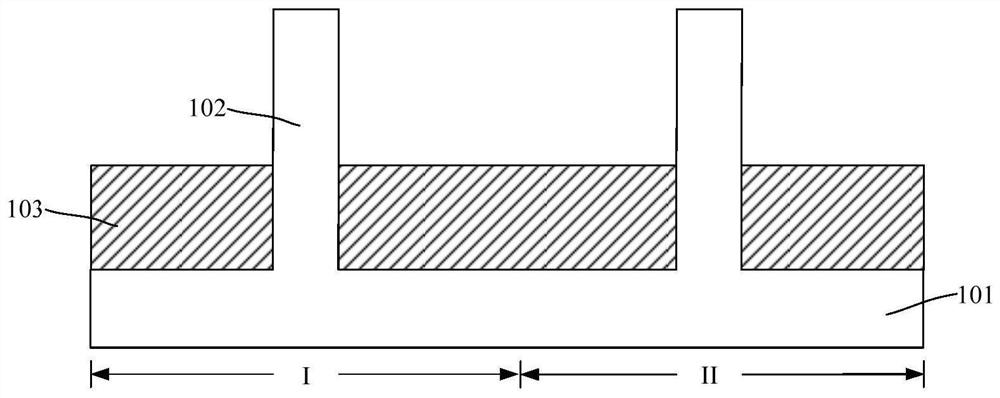

[0032] According to the background technology, the performance of the fin field effect transistor formed in the prior art needs to be improved.

[0033] In order to improve the performance of the fin field effect transistor, the process steps of forming the fin field effect transistor generally include: etching the fins with a partial thickness on both sides of the gate structure to form grooves; Ion implantation is performed on the side wall of the groove to form a light source and drain doped region; and an epitaxial layer filling the groove is formed.

[0034] The above-mentioned epitaxial layer provides a process basis for forming the heavily source-drain doped region of the FinFET. However, there are many defects in the above-formed epitaxial layer, and the surface morphology of the epitaxial layer is poor. poor electrical performance.

[0035]After analysis, it was found that during the process of forming light source and drain doped regions by ion implantation process,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More