FPGA static timing analysis algorithm

A static timing analysis and algorithm technology, applied in computing, CAD circuit design, special data processing applications, etc., to reduce logic and wiring delays and increase operating frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described in detail below in conjunction with the examples.

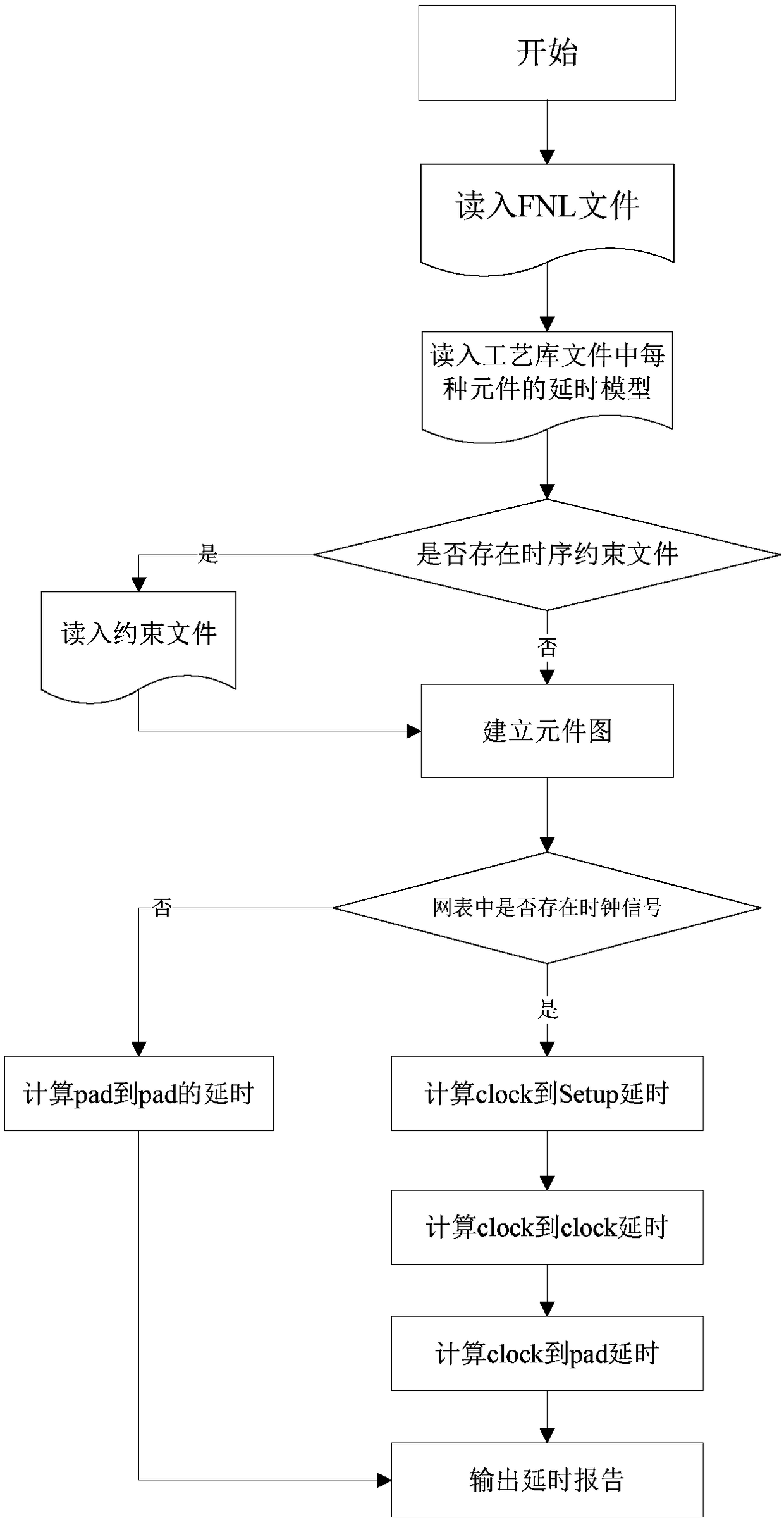

[0024] Such as figure 1 As shown, the present invention relates to an algorithm for FPGA static timing analysis. The purpose of this algorithm is to find the critical paths that make chip timing invalid and play a decisive role in chip performance faster. It uses an exhaustive analysis method (existing method) to extract all timing paths that exist in the entire circuit, examine whether the signal meets the requirements of timing constraints when passing through these paths, and find out violations by analyzing the maximum path delay and the minimum path delay. Timing constraint error.

[0025] The key point of the design of timing analysis program is the establishment of directed acyclic graph (hereinafter referred to as graph) and the calculation of critical path. First, the establishment of the graph is divided into two stages. After each element is read in and a no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More