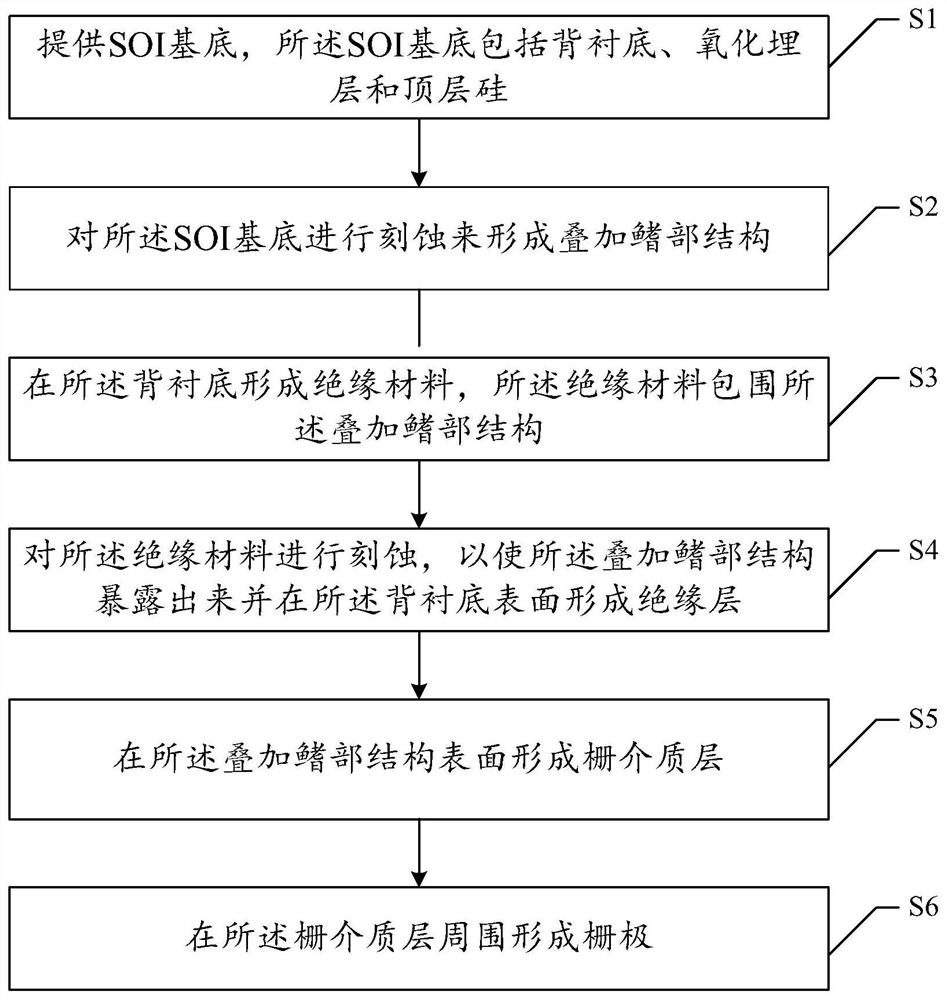

Superimposed three-dimensional transistor and its manufacturing method

A transistor and three-dimensional technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of occupying space, high cost of semiconductor chips, unfavorable integration of semiconductor chip devices, etc., to improve device integration and reduce overall cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The following will clearly and completely describe the technical solutions in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

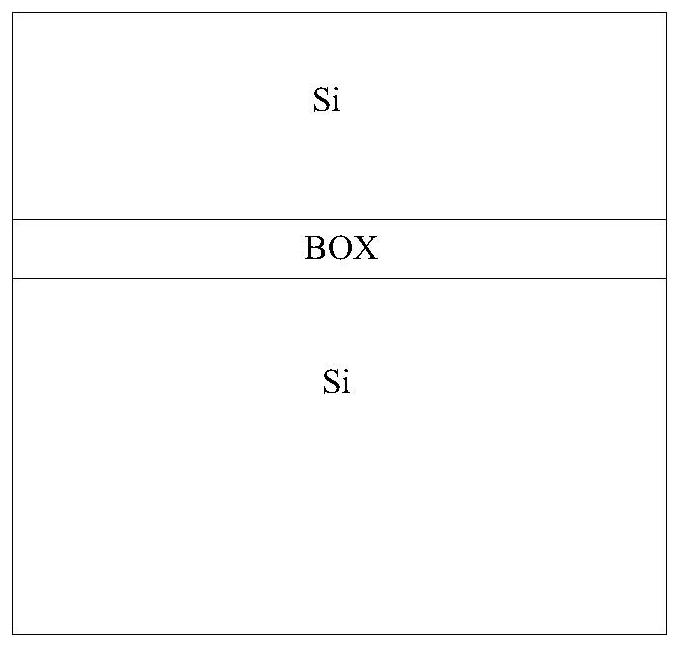

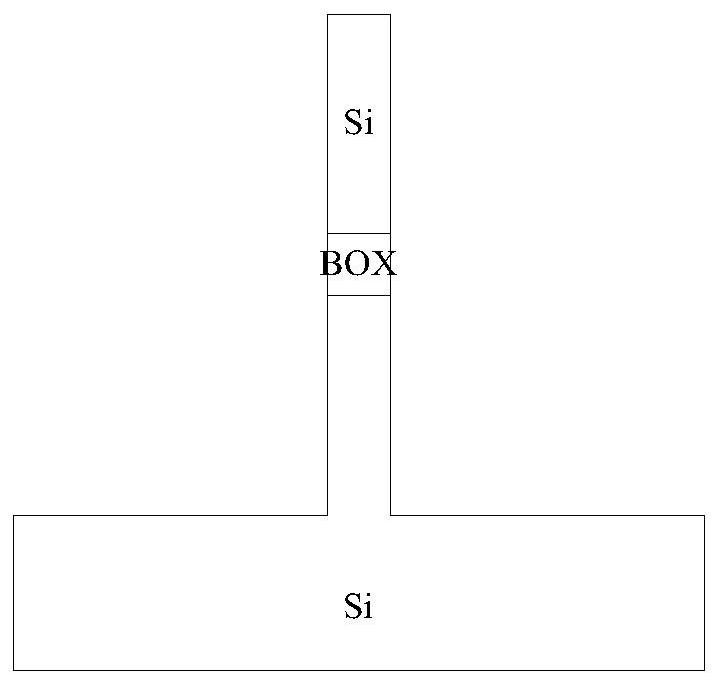

[0020] In order to solve the problems of low device integration and high cost in the existing three-dimensional field effect transistors, the present invention provides a method for manufacturing a superimposed three-dimensional transistor and a superimposed three-dimensional transistor manufactured by the above-mentioned method. By etching the buried oxide layer of the SOI substrate, the semiconductor materials above and below the buried oxide layer of the SOI substrate are used as the channel regions of the two thre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More