Method for improving high-low voltage ESD protection performance by employing well segmentation technology

An ESD protection, low-voltage technology, applied in low-voltage ESD protection design, using well segmentation technology to improve the performance of low-voltage ESD protection devices, can solve the problems of easy latch-up, high trigger voltage, etc., achieve the effect of reducing parasitic capacitance and meeting ESD protection requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail;

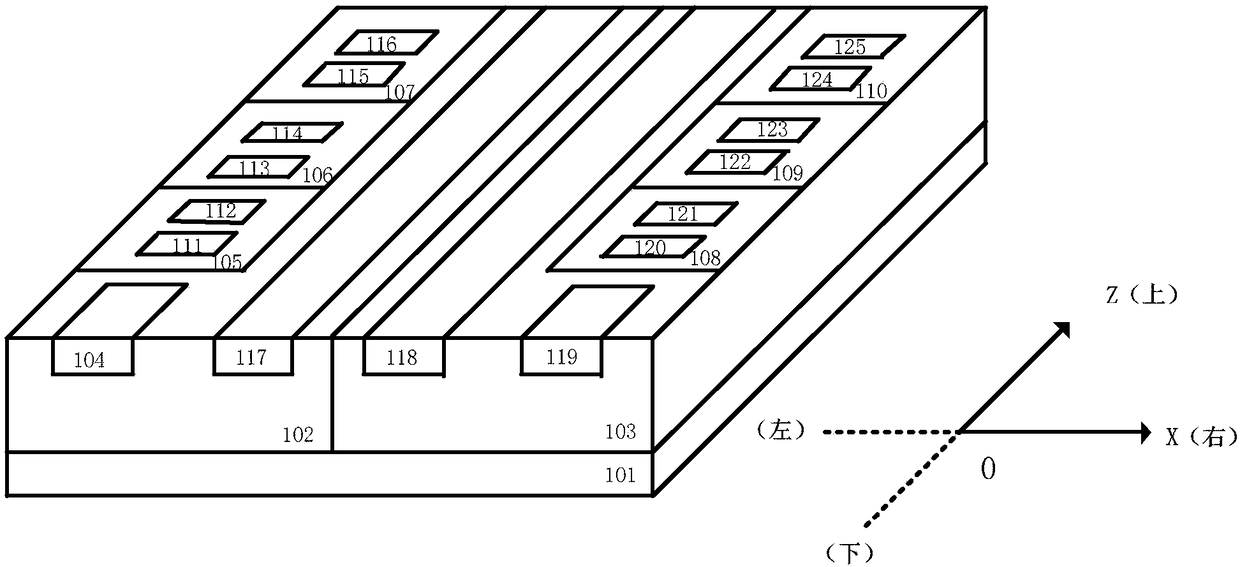

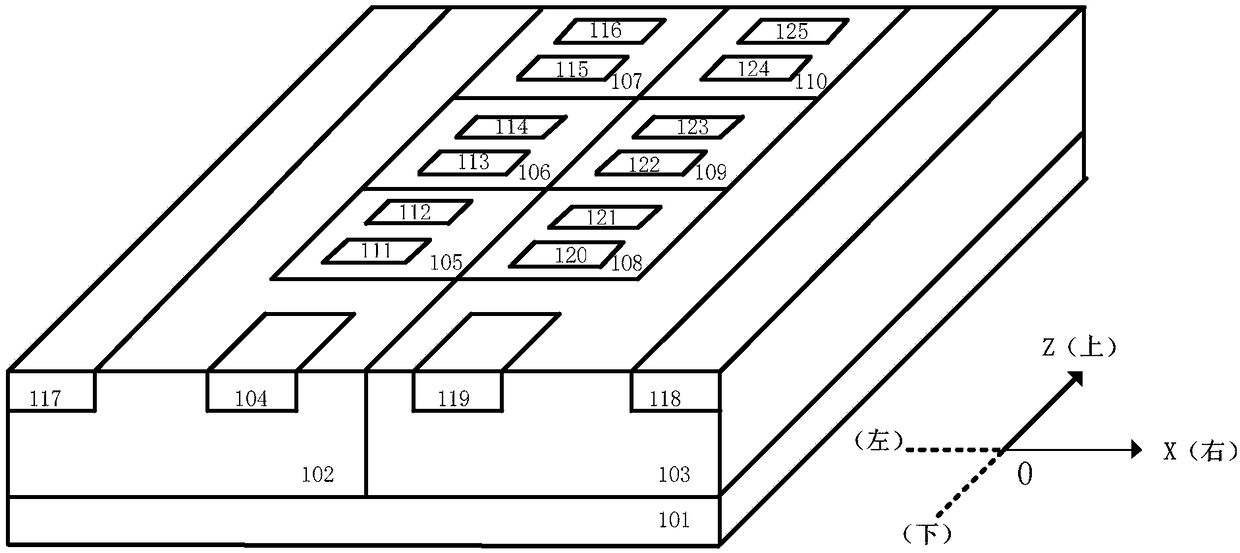

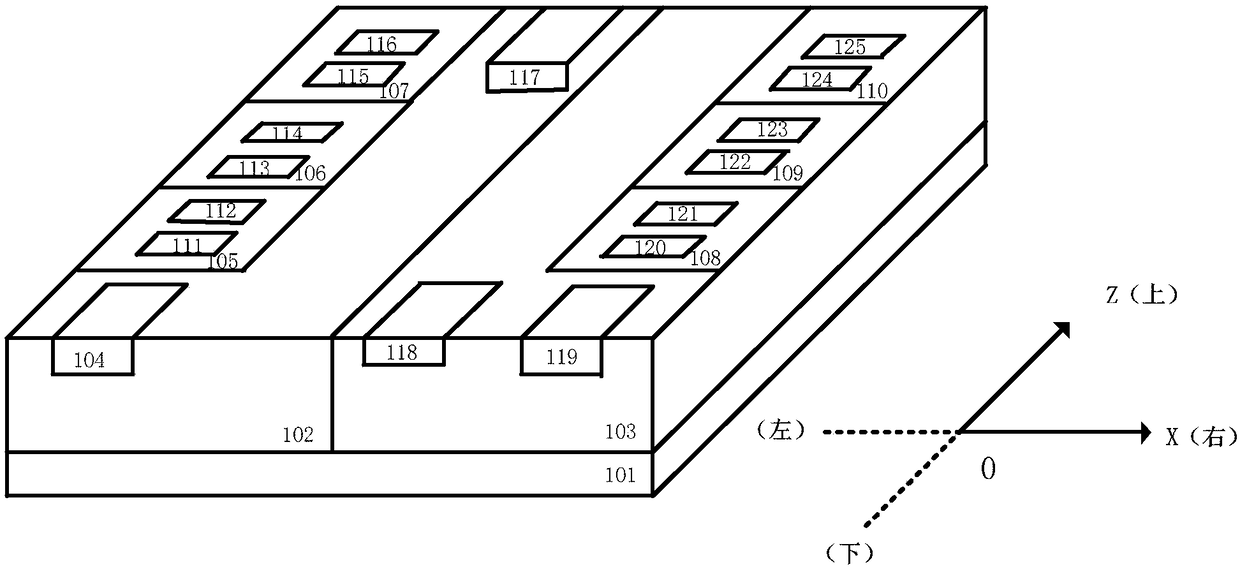

[0025] The example of the present invention has designed a kind of method that utilizes well segmentation technology to improve low-voltage ESD protection performance, and it comprises the ESD current discharge path of SCR and the ESD electric discharge path of diode forward conduction, utilizes well segmentation technology on the one hand, can not only aim at Different protected circuits are designed with different voltages to trigger and turn on the low-voltage ESD protection device. On the other hand, a special metal wiring method is used to adjust the P+ injection region in the first N well and the first P well inside the device. The position of the stripe layout of the N+ injection region changes the sustaining voltage of the low-voltage ESD protection device.

[0026] Such as figure 1 The structure sectional view of the shown method examp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More