Method for optimizing efficient clock tree physical wiring in rear-end design of integrated circuit semi-customization

An integrated circuit and physical winding technology, which is applied in the direction of electrical digital data processing, calculation, special data processing applications, etc., can solve problems such as poor design quality and long iteration time, shorten the chip design cycle and improve work efficiency , reduce the effect of ineffective work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

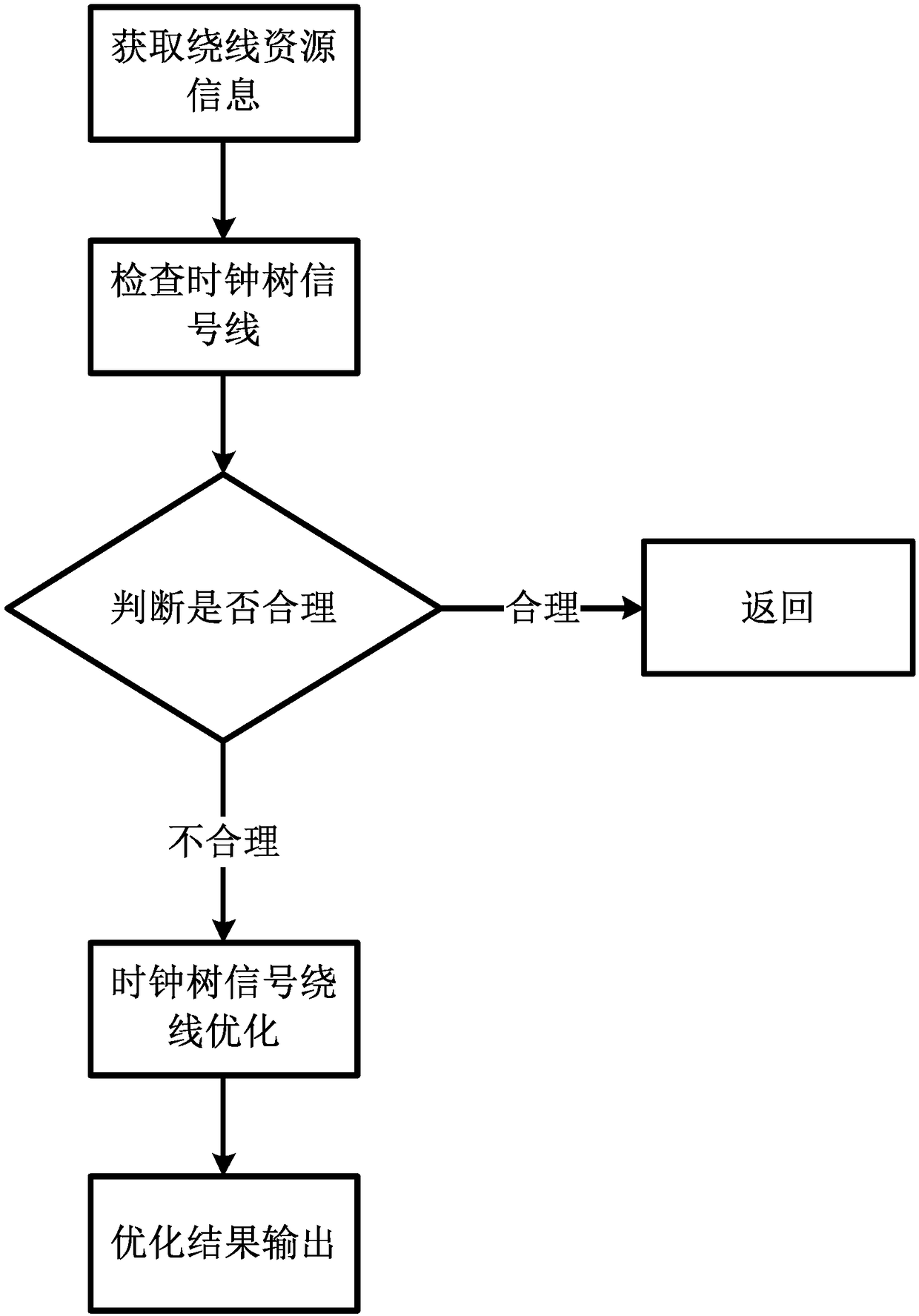

[0026] The invention discloses a method for optimizing the physical wiring of an integrated circuit semi-customized back-end design and high-efficiency clock tree physical winding. The specific implementation of the invention will be further described below in combination with preferred embodiments.

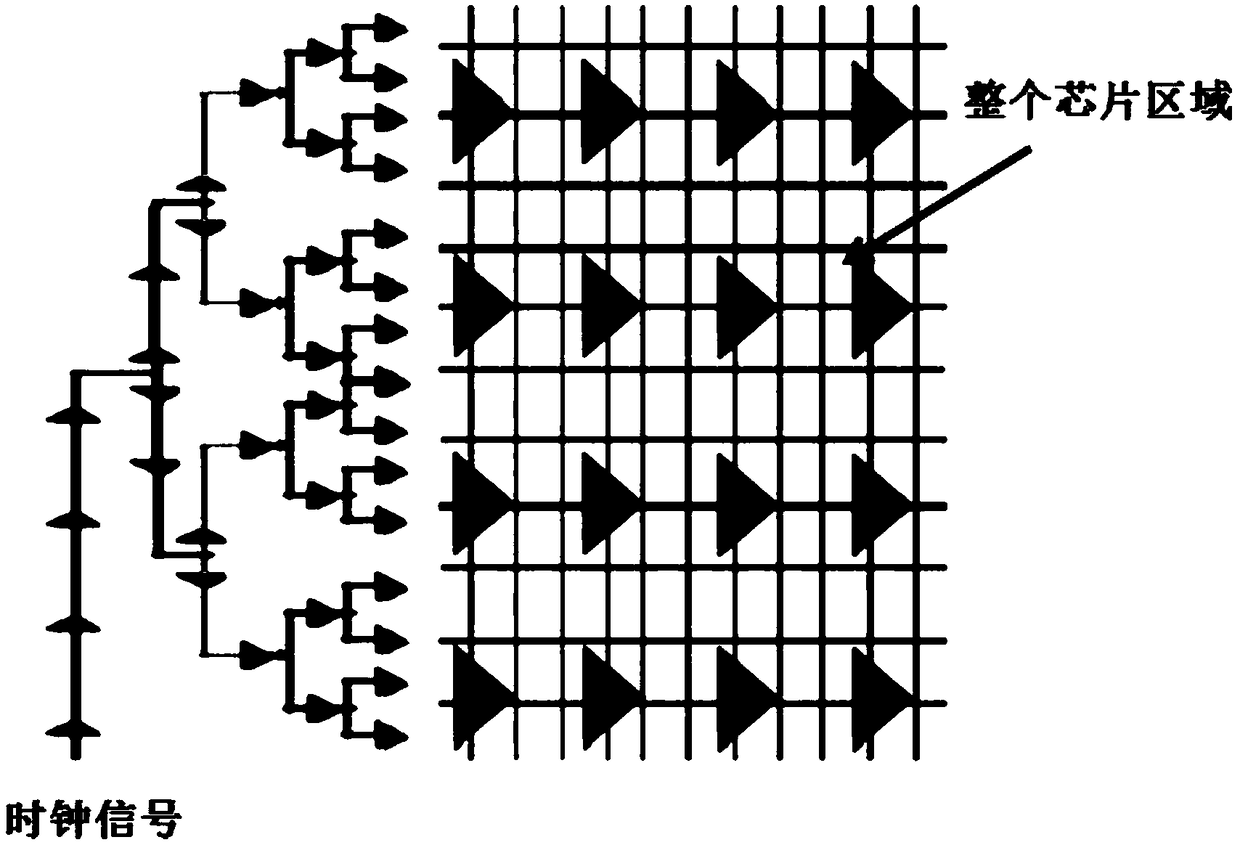

[0027] see attached figure 1 , it is worth noting that during the design process of an integrated chip, data transmission between functional elements is controlled by a synchronous signal, which is usually a clock signal. Therefore, the design quality of the clock signal plays an important role in the high-performance chip design process. The clock signal is usually the signal with the largest fanout, the longest distance, and the highest speed in the entire integrated chip.

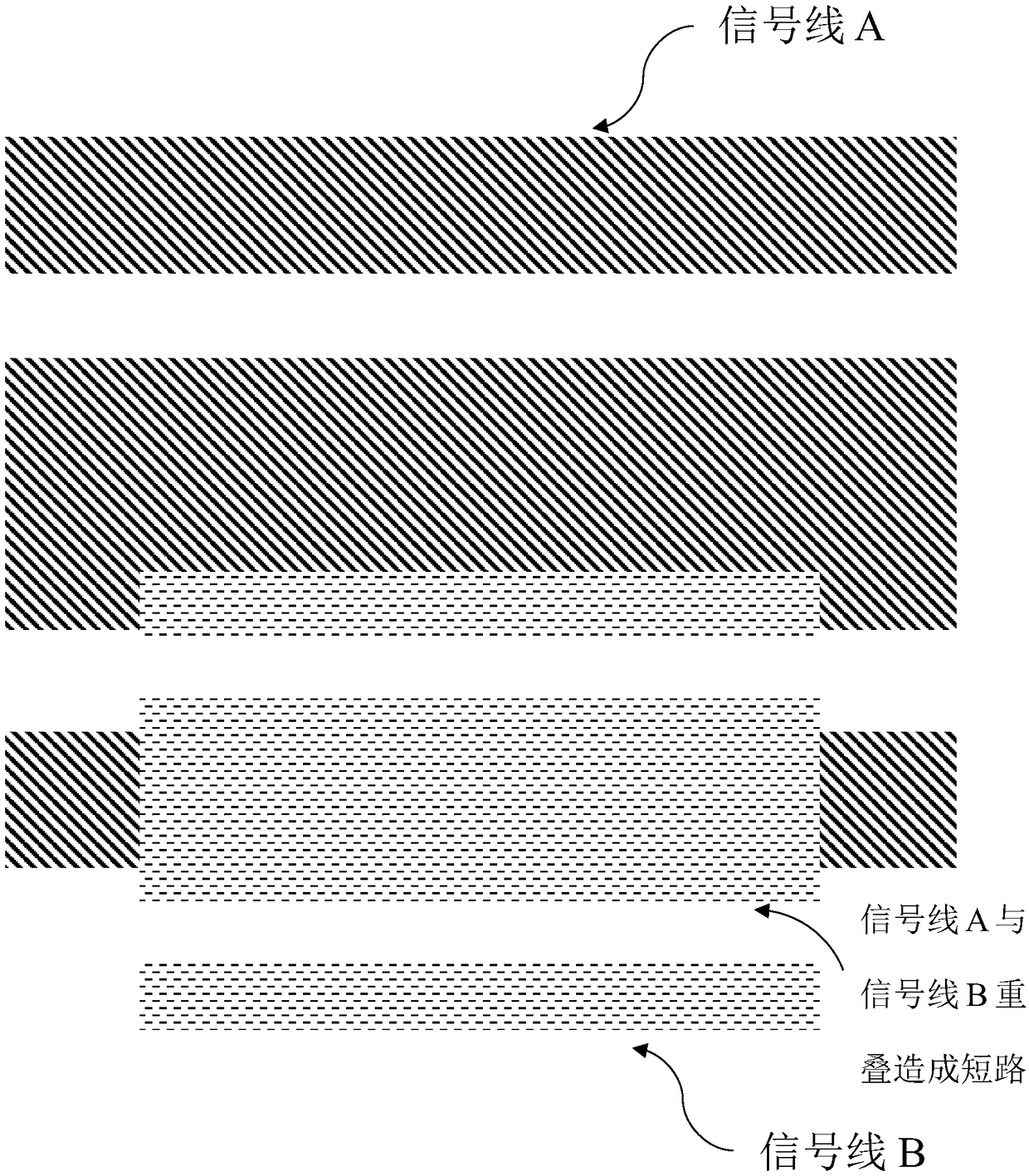

[0028] see attached figure 2 , it is worth noting that in physical implementation, physical winding is required between the components that make up the clock tree to realize signal transmission. In actu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More