Shift register unit, gate drive circuit, display panel and display device

A shift register and circuit technology, applied in the fields of display panels, display devices, gate drive circuits, and shift register units, can solve the problem of complex gate drive circuit structure design, disadvantageous ultra-narrow frame design, large display panel space, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

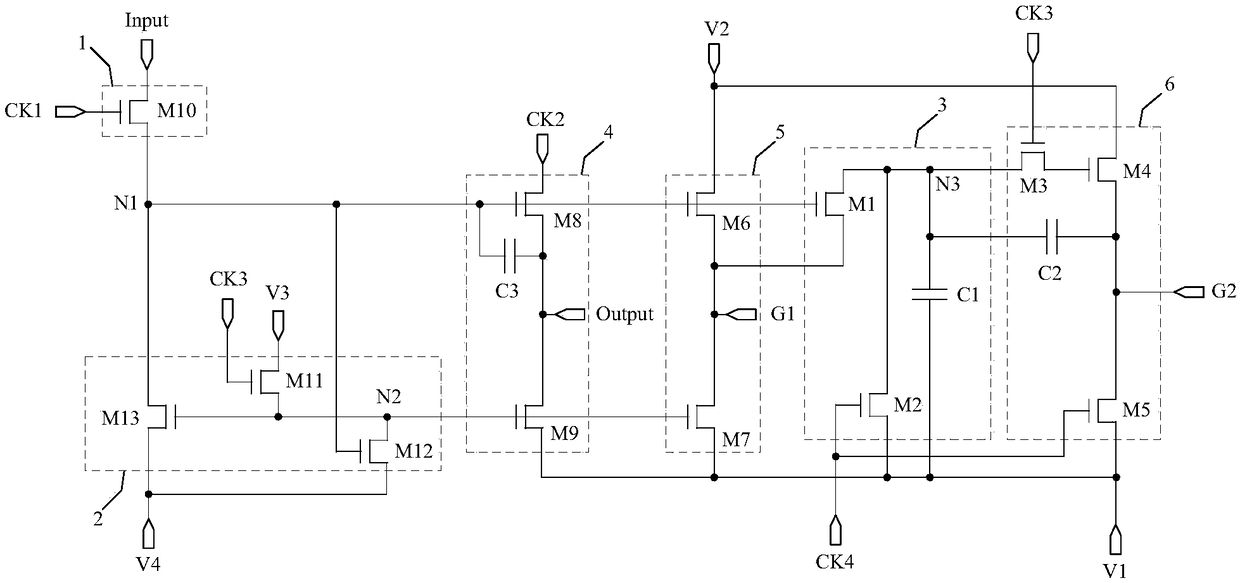

[0111] Such as Figure 3ashown, select Figure 3a There are four stages in the circuit timing diagram shown: the first stage T1, the second stage T2, the third stage T3 and the fourth stage T4.

[0112] In the first stage T1, Input=1, CK1=1, CK2=0, CK3=0, CK4=0.

[0113] Since CK1=1, the tenth switching transistor M10 is turned on to provide the high-level signal of the input signal terminal Input to the first node N1, so that the signal of the first node N1 is a high-level signal. Since the signal of the first node N1 is a high level signal, the first switch transistor M1 , the sixth switch transistor M6 , the eighth switch transistor M8 and the twelfth switch transistor M12 are all turned on. The turned-on twelfth switch transistor M12 provides the low-level signal of the fourth reference signal terminal V4 to the second node N2, making the signal of the second node N2 a low-level signal, thereby controlling the first sub-transistor M131, the second The second sub-transis...

Embodiment 2

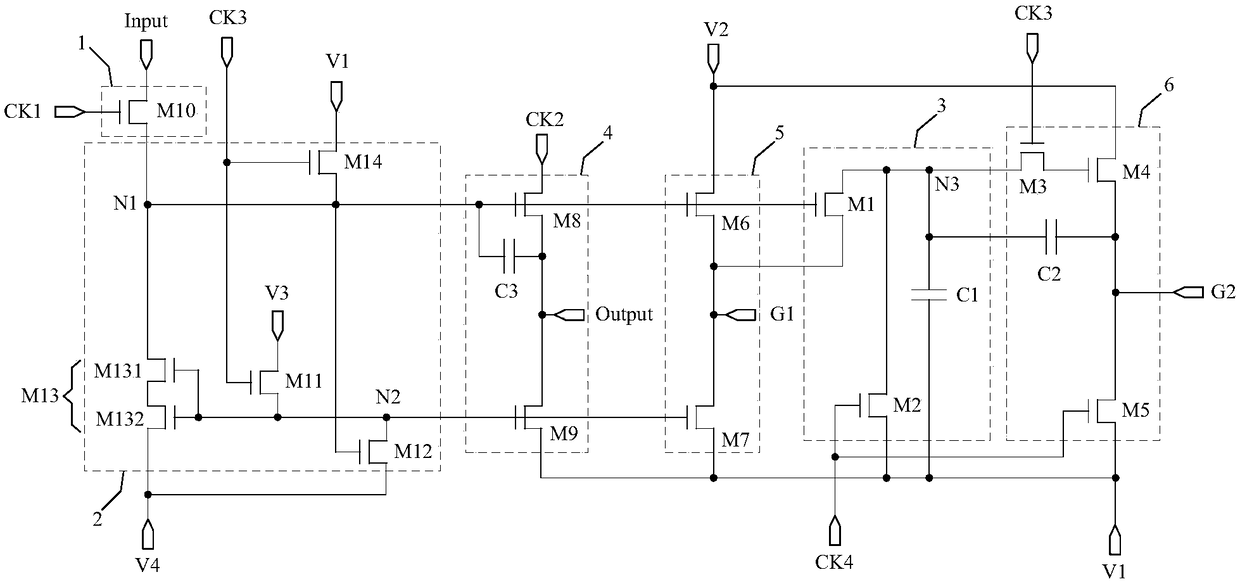

[0124] The first clock signal terminal CK1 and the fourth clock signal terminal CK4 can receive the same signal. The following description will be made by taking the first clock signal terminal CK1 and the fourth clock signal terminal CK4 both receiving the signal of the first clock signal terminal CK1 as an example.

[0125] Such as Figure 3b shown, select Figure 3b There are four stages in the circuit timing diagram shown: the first stage T1, the second stage T2, the third stage T3 and the fourth stage T4.

[0126] In the first stage T1, Input=1, CK1=1, CK2=0, CK3=0.

[0127] Since CK1=1, the second switch transistor M2 , the fifth switch transistor M5 and the tenth switch transistor M10 are all turned on. The turned-on tenth switch transistor M10 provides the high-level signal of the input signal terminal Input to the first node N1, so that the signal of the first node N1 is a high-level signal. Since the signal of the first node N1 is a high level signal, the first s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More