Layout method of dynamic reconfigurable FPGA

A layout method and dynamic technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as single model layout, achieve the effects of reducing external fragments, improving utilization, and enhancing flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

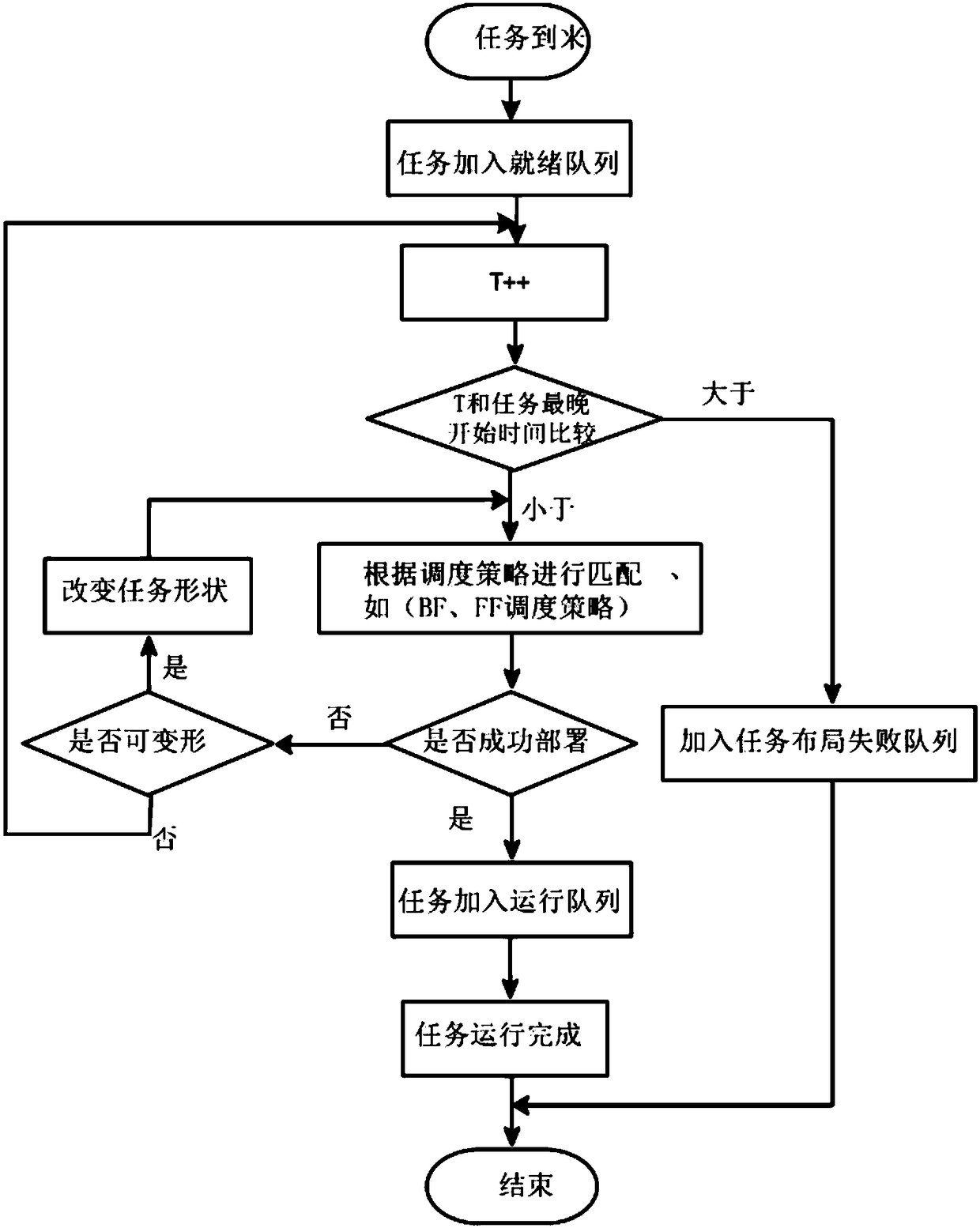

[0047] The present invention is a layout method of dynamically reconfigurable FPGA, constructs computing resources of FPGA dynamically reconfigurable system, and establishes a single hardware task T n In the FPGA online layout process, the FF Reshaped-Task-Model scheduling algorithm is used to deform the task model to complete the layout and improve the utilization of FPGA resources.

[0048] Include the following steps:

[0049] S1. Define the size of resources in the reconfigurable area;

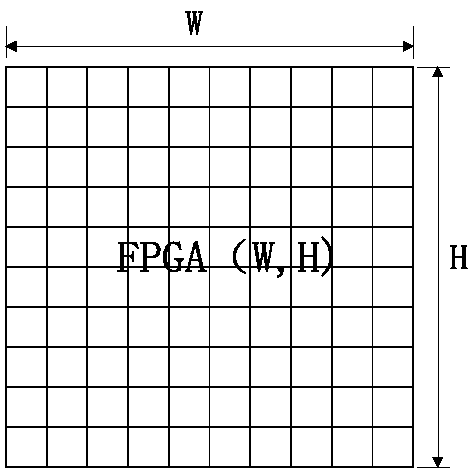

[0050] see figure 1 , FPGA(W,H) represents the computing resource of the dynamic reconfigurable system, W represents the width of the reconfigurable resource, H represents the height of the reconfigurable resource, W×H represents the size of the reconfigurable resource, then:

[0051]

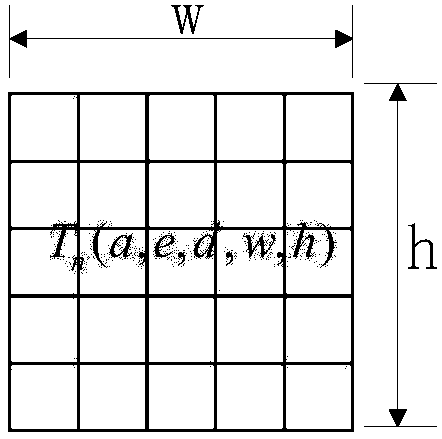

[0052] S2. Establish a Reshaped-Task-Model model based on a single hardware task

[0053] see figure 2 , a single hardware task uses T n =(a, e, d, w, h) means that a is the arrival time of the tas...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More