Manufacturing method of semiconductor element

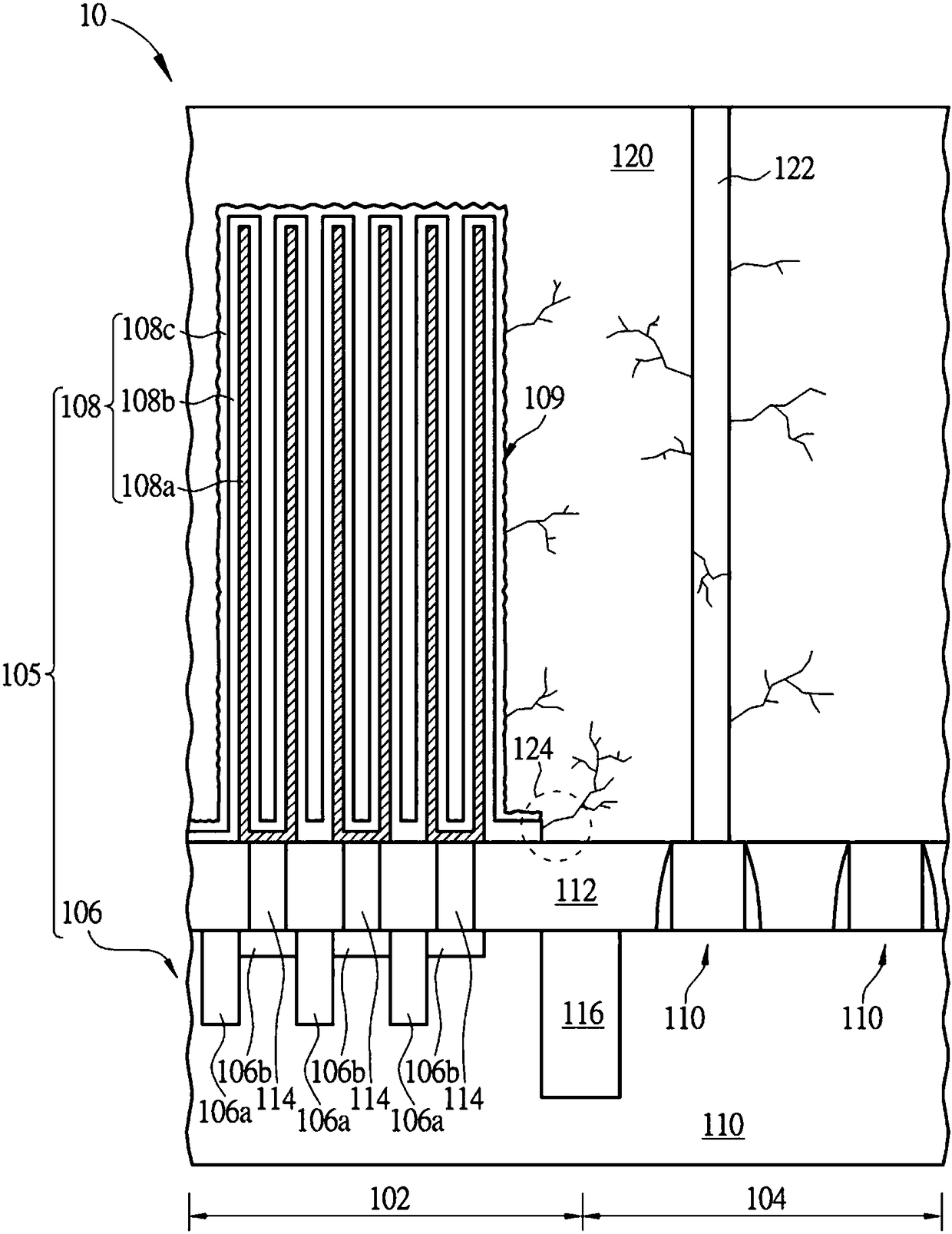

一种制作方法、半导体的技术,应用在半导体器件、半导体/固态器件制造、电气元件等方向,能够解决介电层120碎裂、流至其他地方、接触结构122断路等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

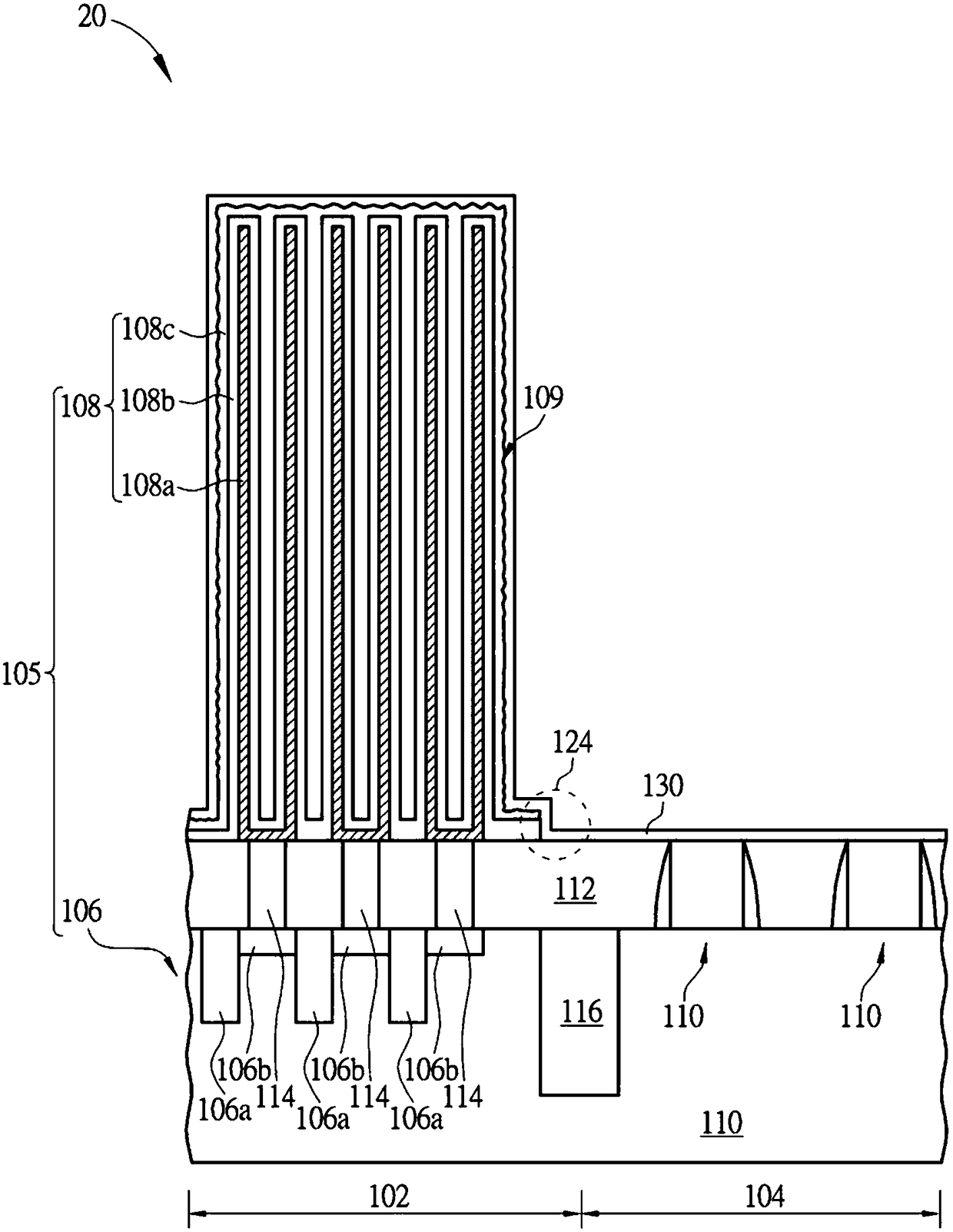

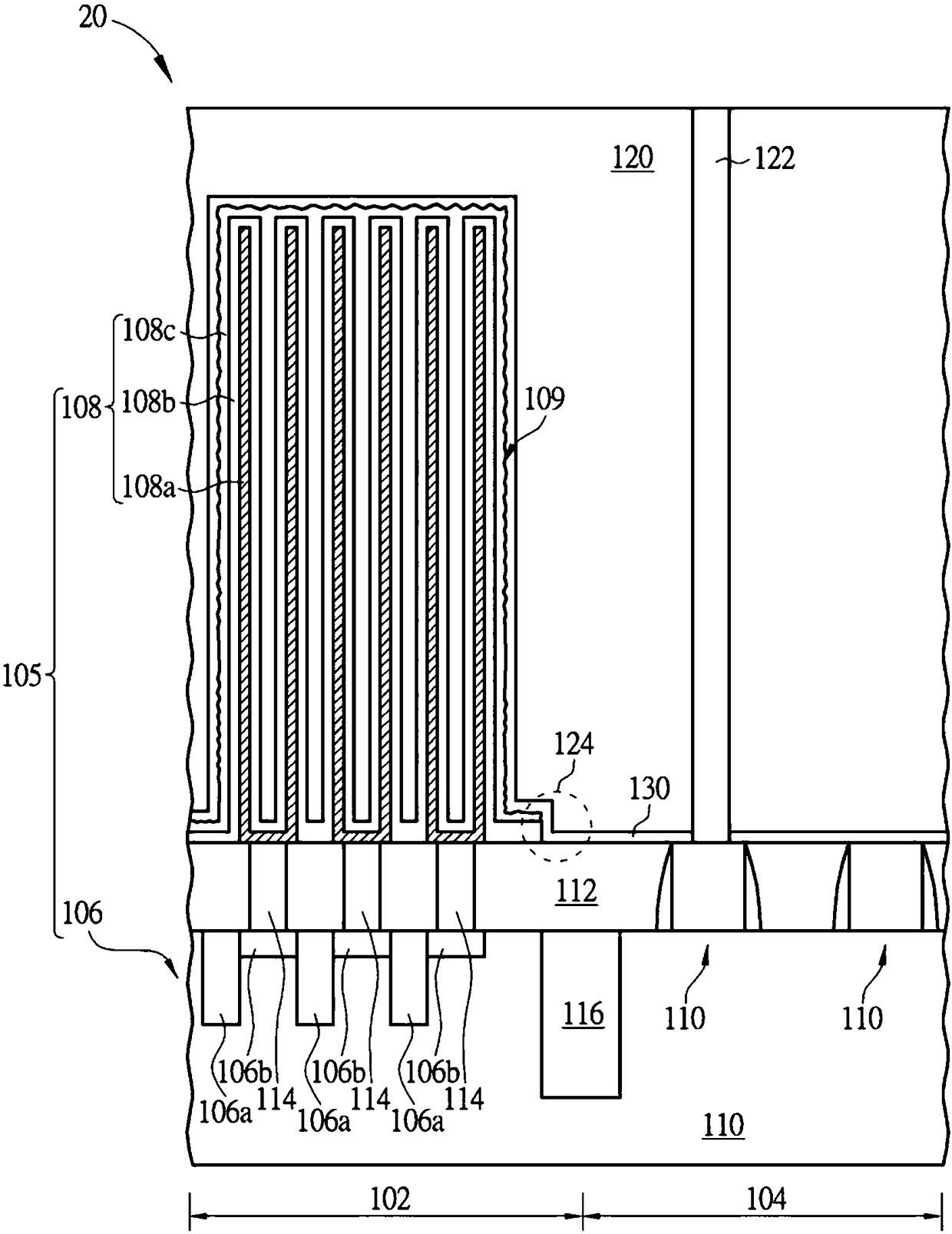

[0041] Please refer to figure 2 as well as image 3 ,in figure 2 as well as image 3 It is a schematic diagram of a dynamic random access memory located at the junction of a storage area and a peripheral area according to the first preferred embodiment of the present invention. First, if figure 2 As shown, a DRAM 20 is provided. Please note that the DRAM 20 here is based on the DRAM 10 mentioned in the background art, and the same components are denoted by the same reference numerals. The substrate 100 includes a storage area 102 and a peripheral area 104 respectively, and the storage area 102 includes at least a plurality of first transistors 106 and capacitors 108 , and the peripheral area 104 includes at least a plurality of second transistors 110 . Components that are not specifically mentioned here and in the following are the same as the DRAM 10 mentioned in the background art, and will not be further described here.

[0042] Please refer to figure 2, after the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More