Patents

Literature

46results about How to "Improve production process yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

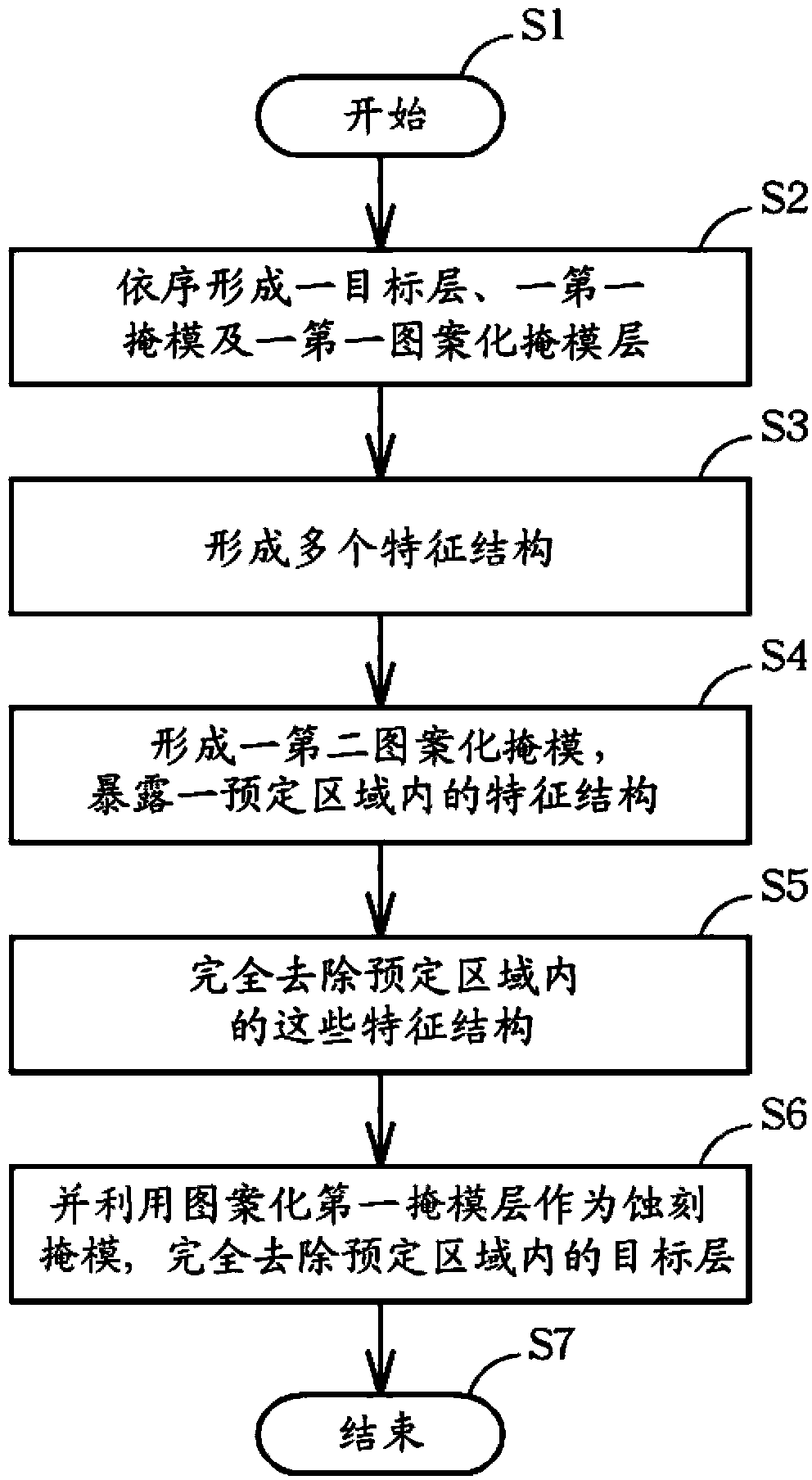

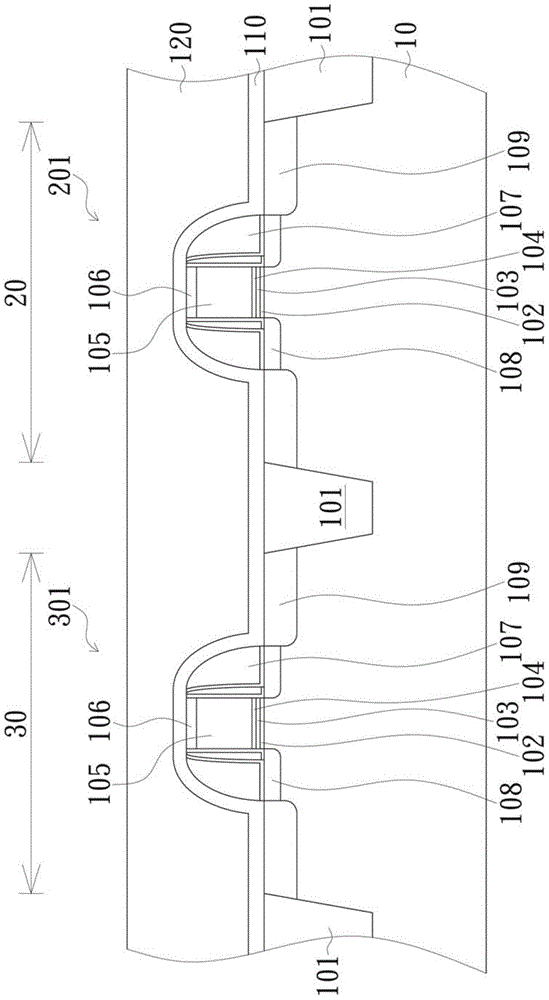

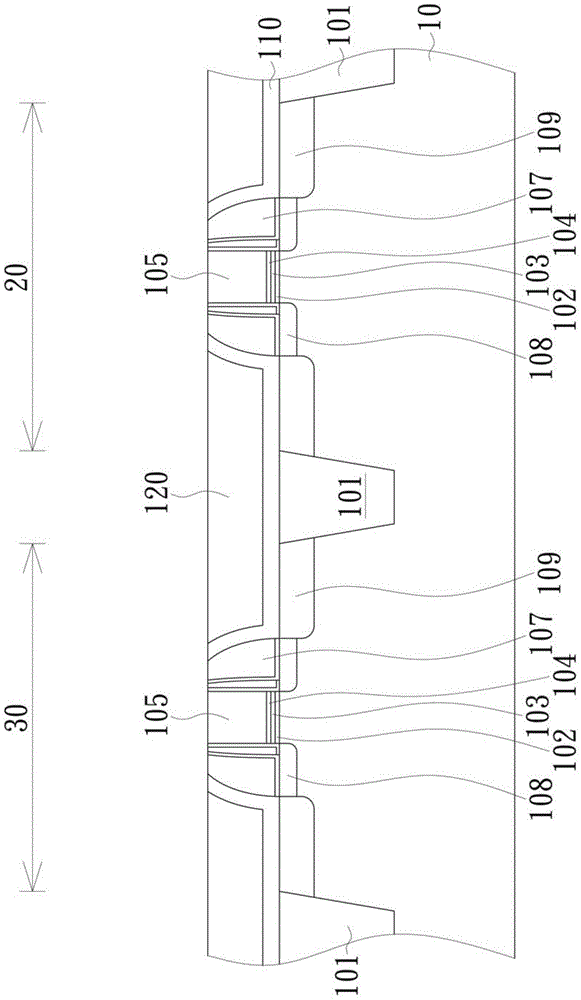

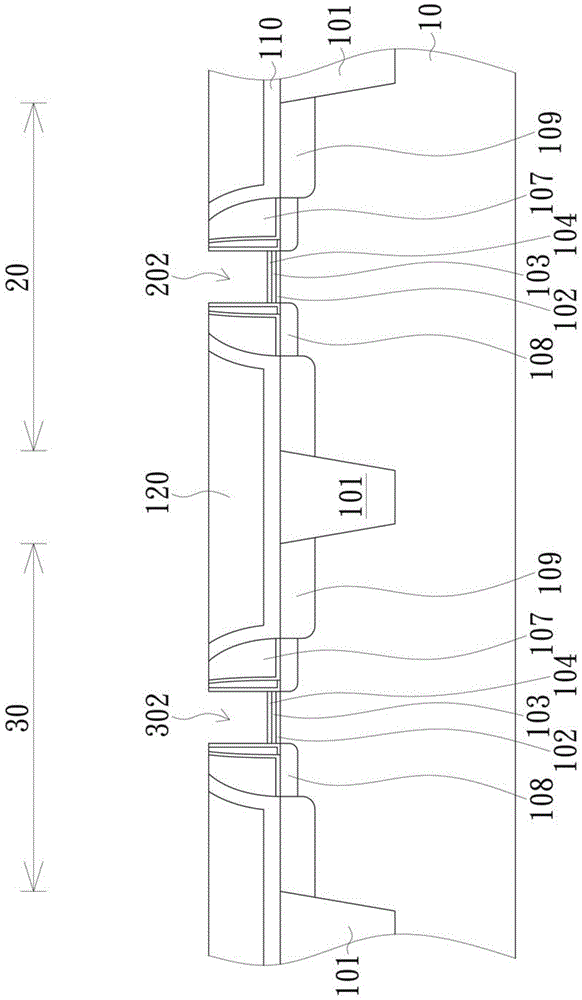

Method for manufacturing semiconductor device patterned structure

ActiveCN103390551AImprove production process yieldSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentSemiconductorFeather

The invention discloses a method for manufacturing a semiconductor device patterned structure. The method includes the steps of firstly, sequentially forming a target layer, a first mask layer and a first patterned mask layer on a substrate, then using the first patterned mask layer as an etching mask, forming a plurality of feature structures on the substrate, wherein each feature structure comprises a first patterned mask layer and a patterned target layer, forming a second patterned mask on the substrate so as to cover a part of the feature structures and expose a preset region, carrying out a second etching manufacturing process, completely eliminating the feather structures in the preset region and the position, in the preset region, of the second patterned mask, finally, carrying out a third etching manufacturing process, using the first pattering mask layers as etching masks, and completely eliminating the positions, which are not covered by the first patterned mask layers, of the target layer.

Owner:UNITED MICROELECTRONICS CORP

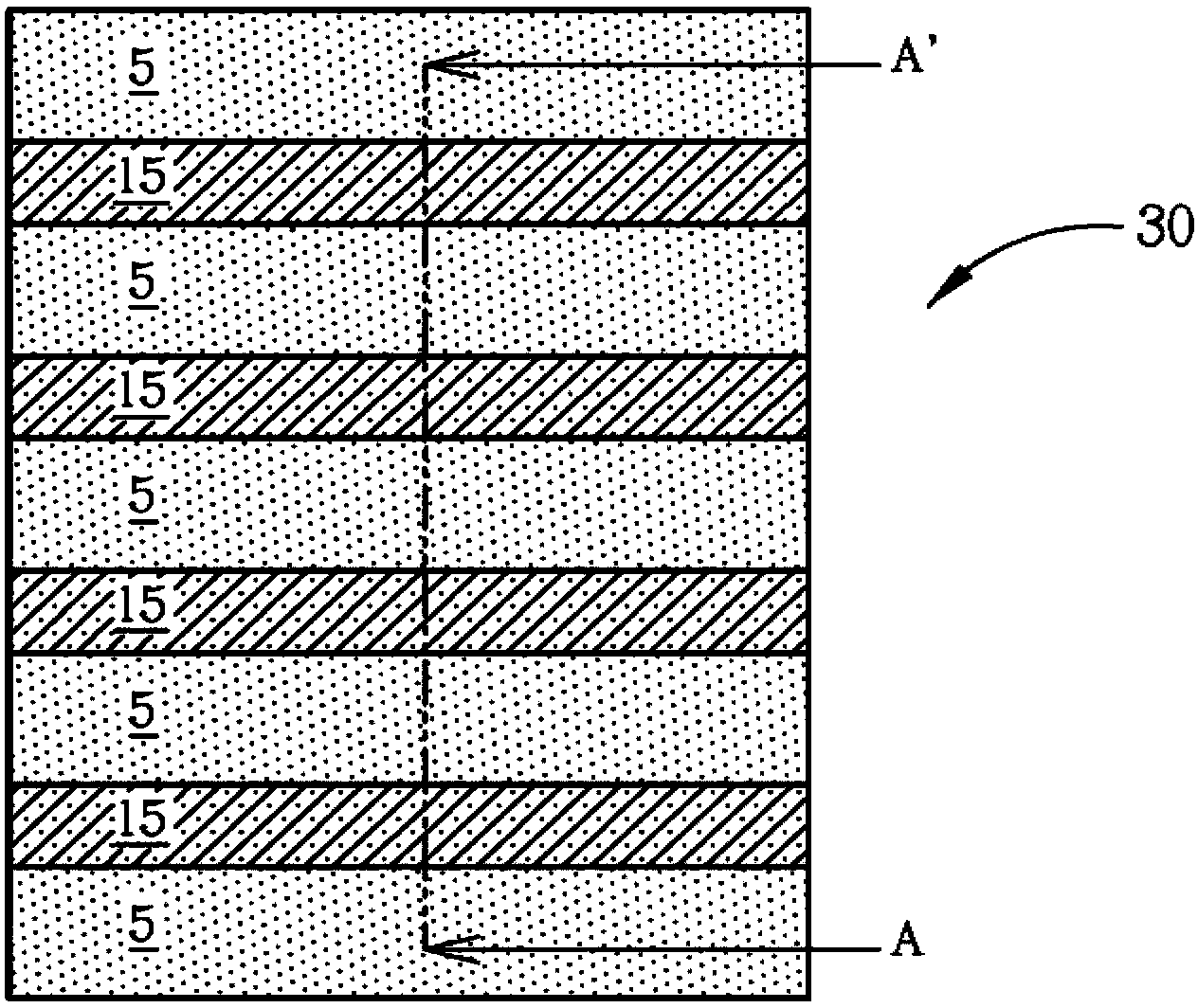

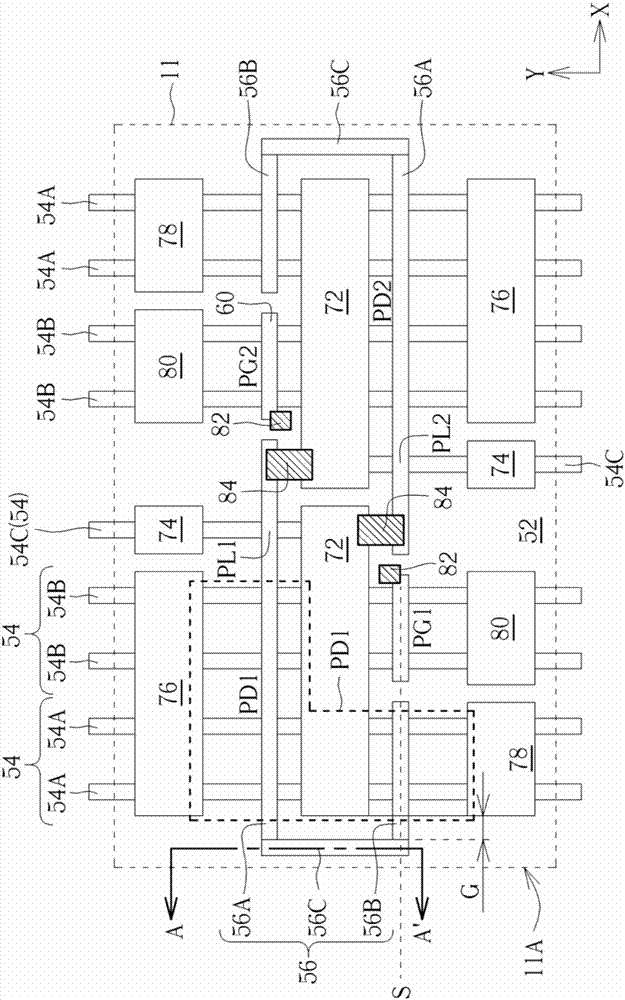

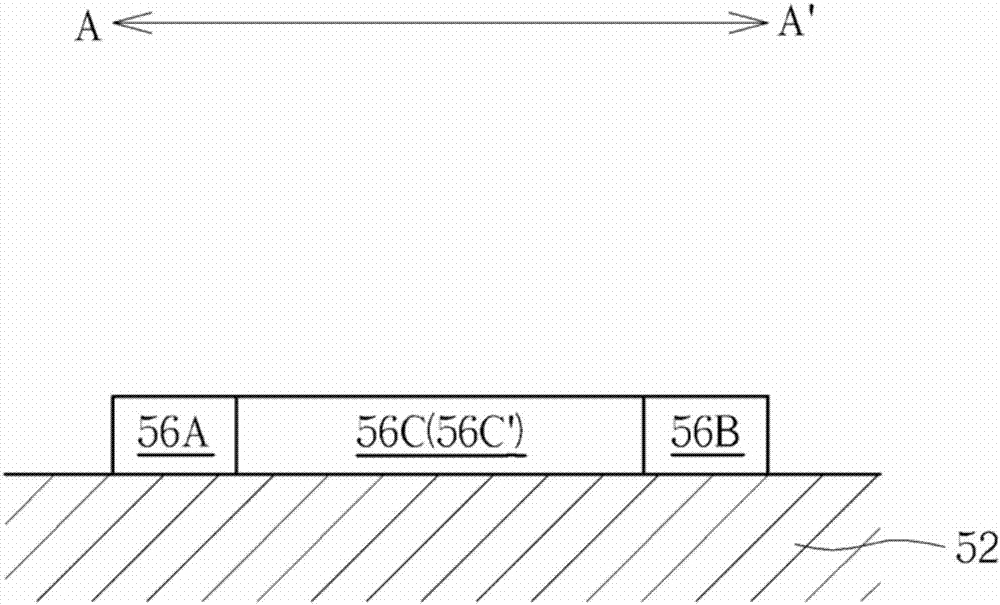

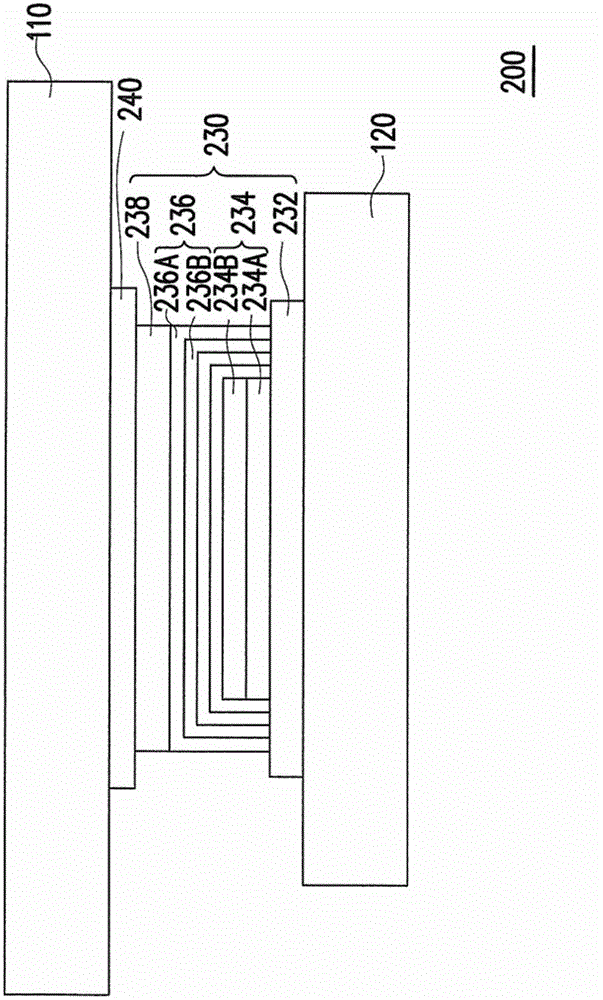

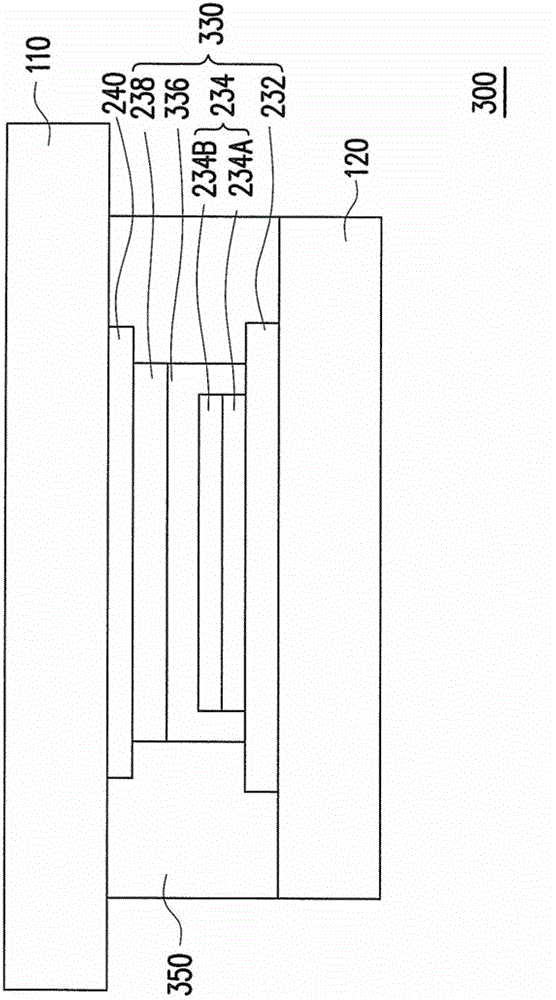

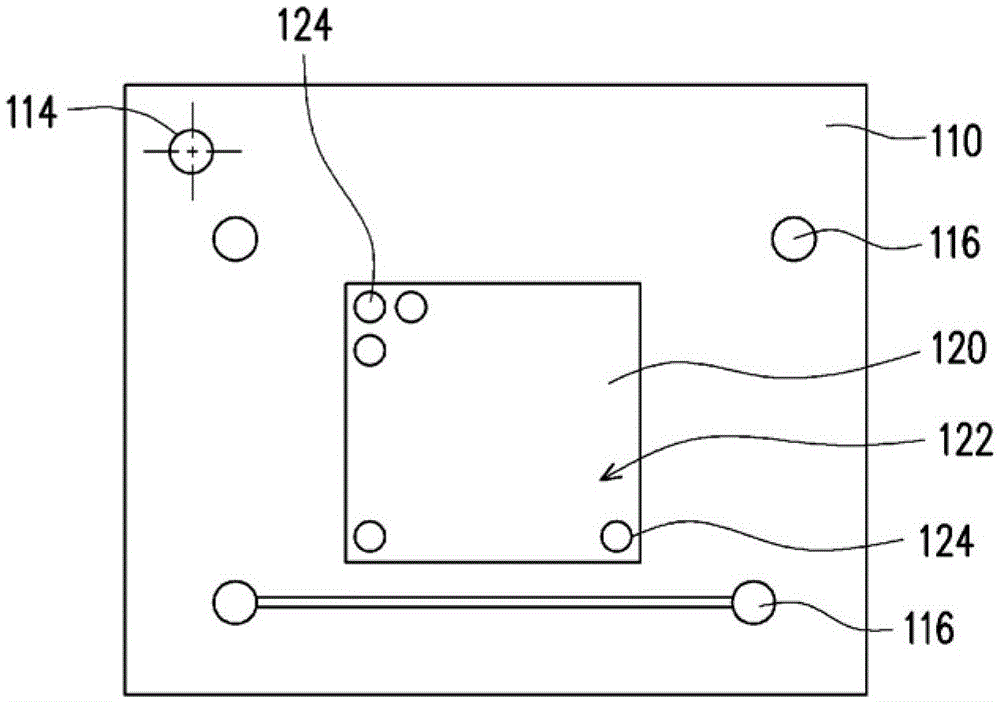

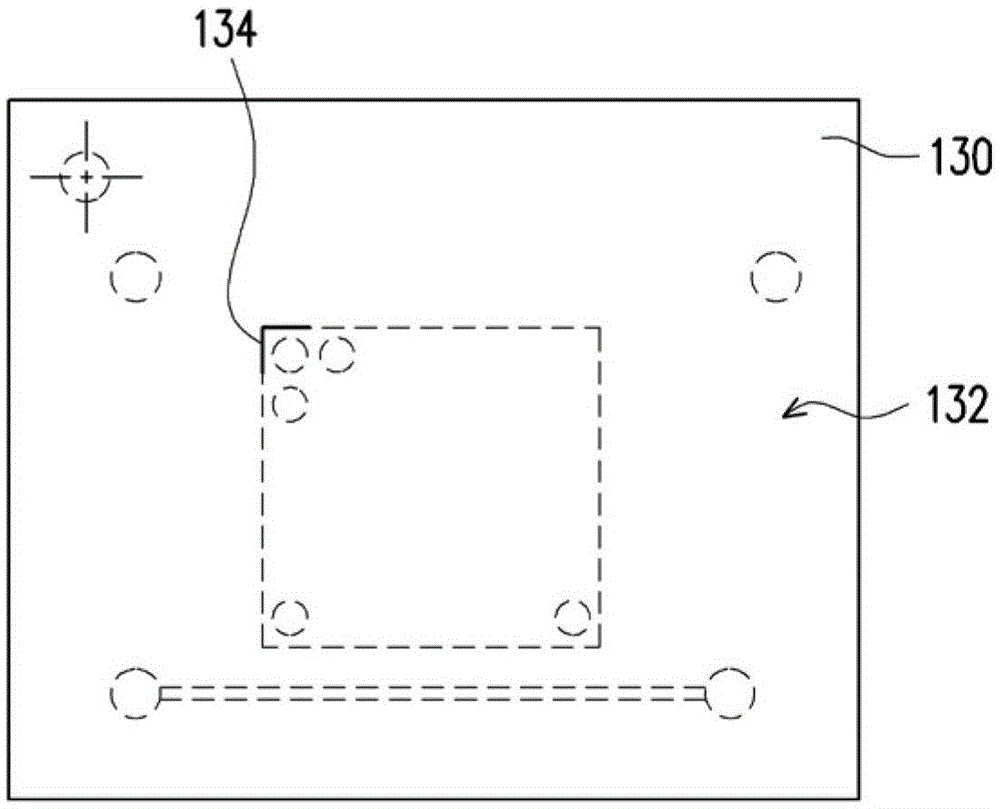

Layout pattern for static random access memory

ActiveCN107346770AImprove reading speedReduce generationSolid-state devicesDigital storageStatic random-access memoryRandom access memory

Owner:UNITED MICROELECTRONICS CORP

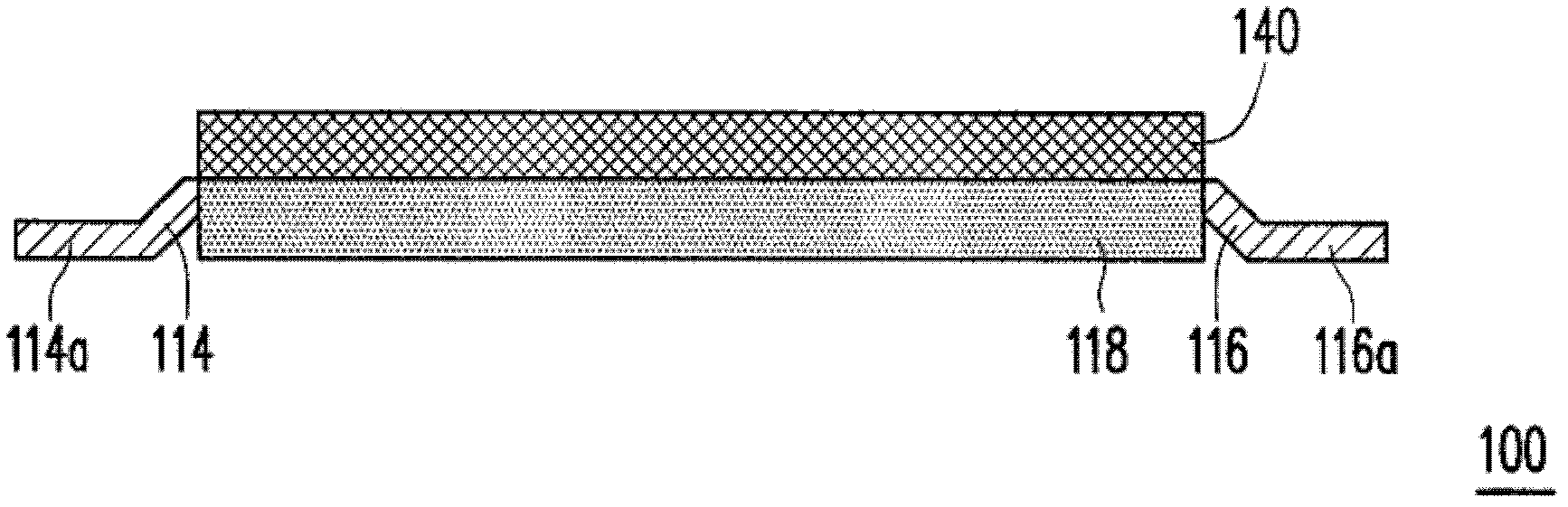

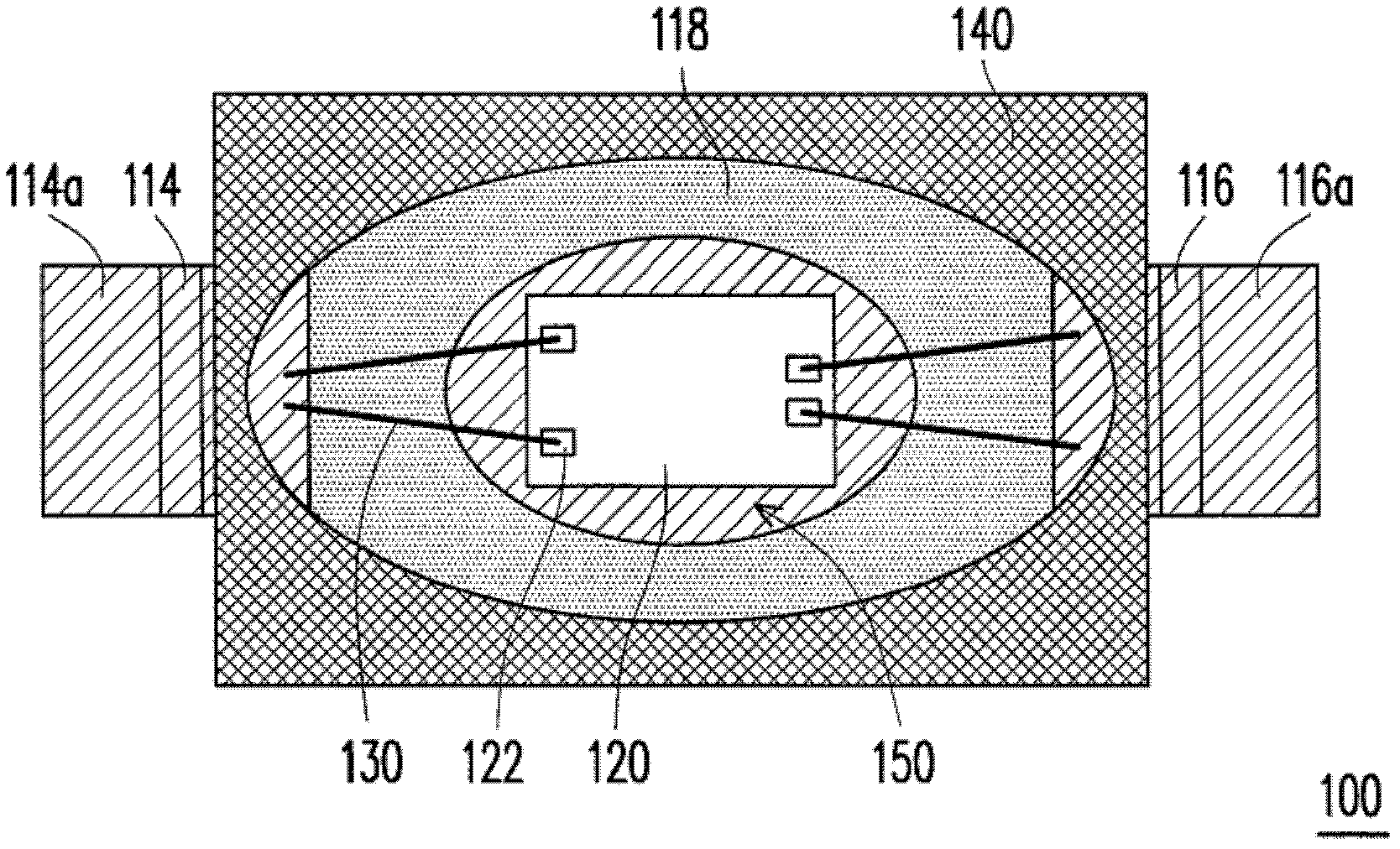

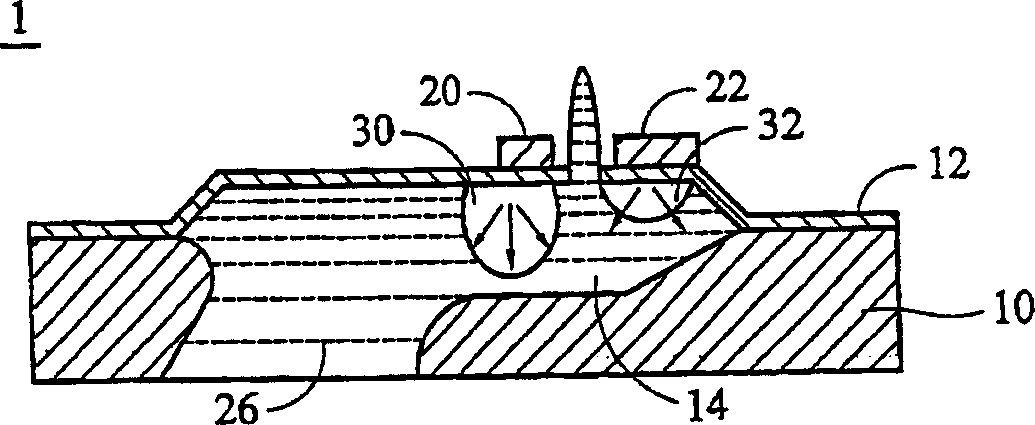

Manufacturing method for embedded type semiconductor package piece of element

ActiveCN103489796AImprove production process yieldReduce difficultySemiconductor/solid-state device manufacturingResistInsulation layer

The invention discloses a manufacturing method for an embedded type semiconductor package piece of an element. A metal substrate is provided. A metal layer is formed on the metal substrate and coats the metal substrate. The metal layer is provided with the upper surface, the lower surface and the first side surface, wherein the upper surface and the lower surface are mutually opposite and are connected through the first side surface. A patterning photo-resist layer is formed on the metal layer, and a part of the upper surface and a part of the lower surface are exposed out of the patterning photo-resist layer. A plurality of connecting pads are formed on the portion, exposed out of the patterning photo-resist layer, of the upper surface and the portion, exposed out of the patterning photo-resist layer, of the lower surface, and the patterning photo-resist layer coats second side surfaces of the connecting pads. The second side surfaces of the connecting pads are exposed after the patterning photo-resist layer is removed. A plurality of electronic elements are arranged on the connecting pads. An insulation layer is pressed on the metal layer in a combination mode and coats the electronic elements, the connecting pads and a part of the metal layer.

Owner:TRIPOD WUXI ELECTRONICS

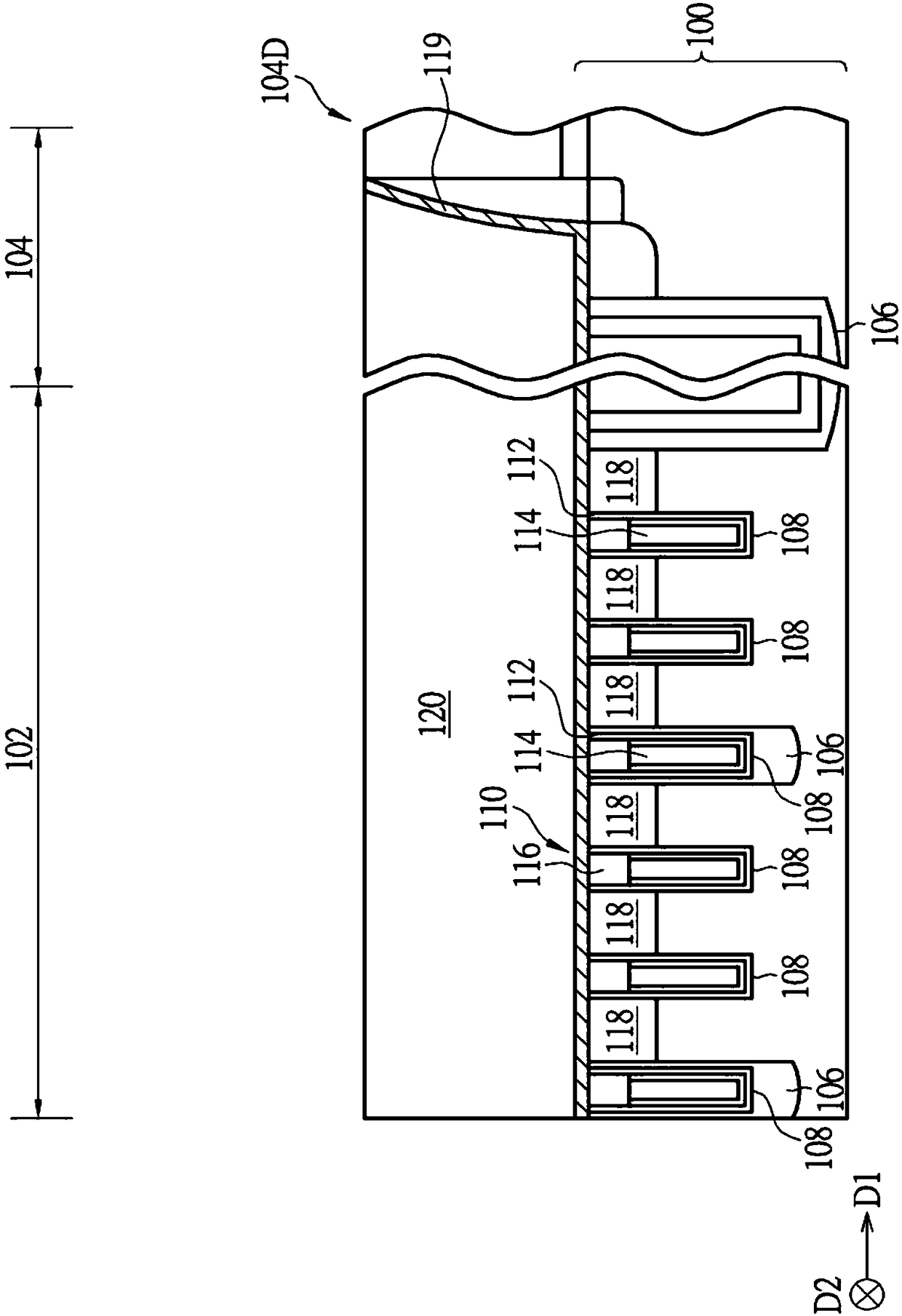

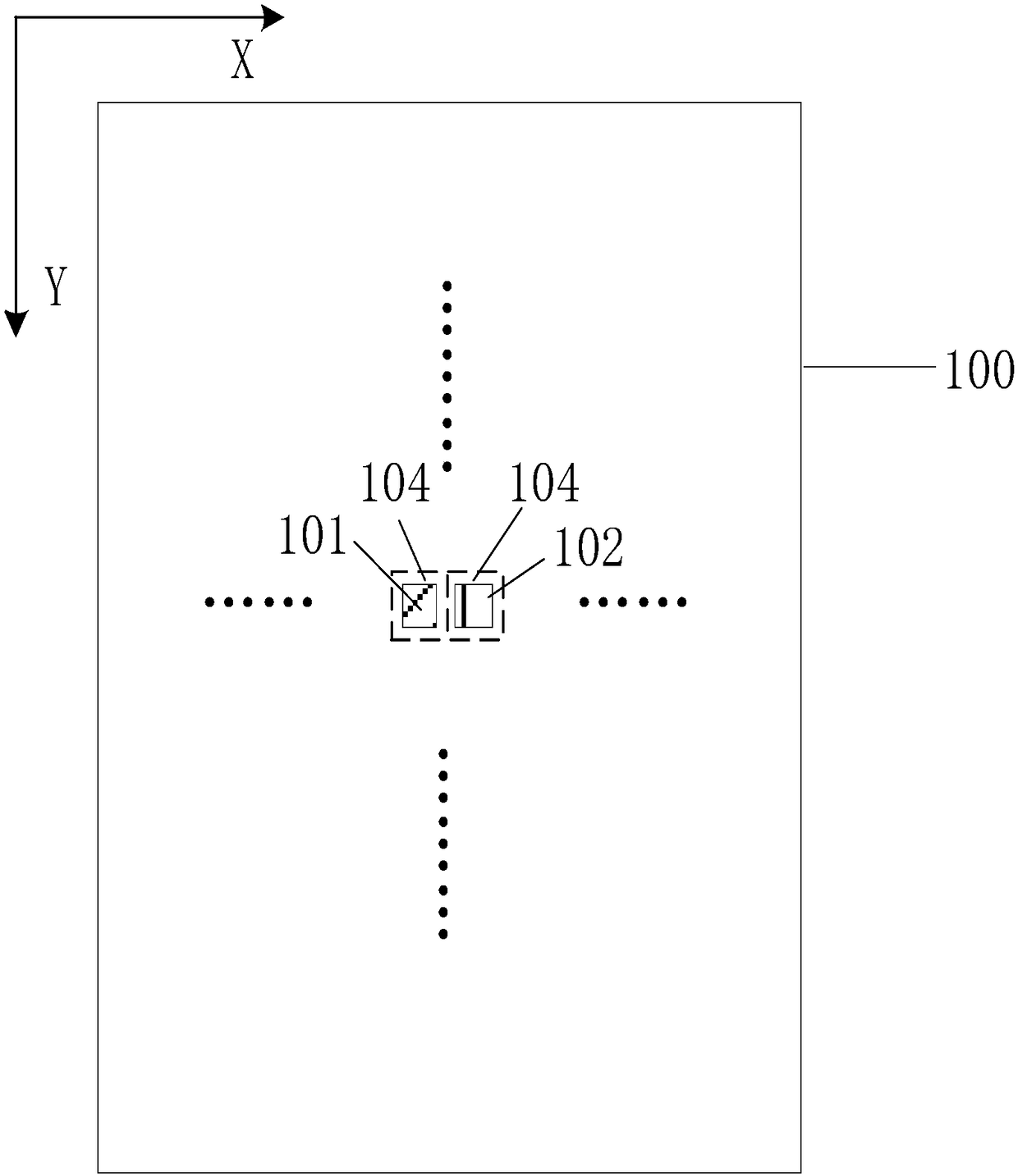

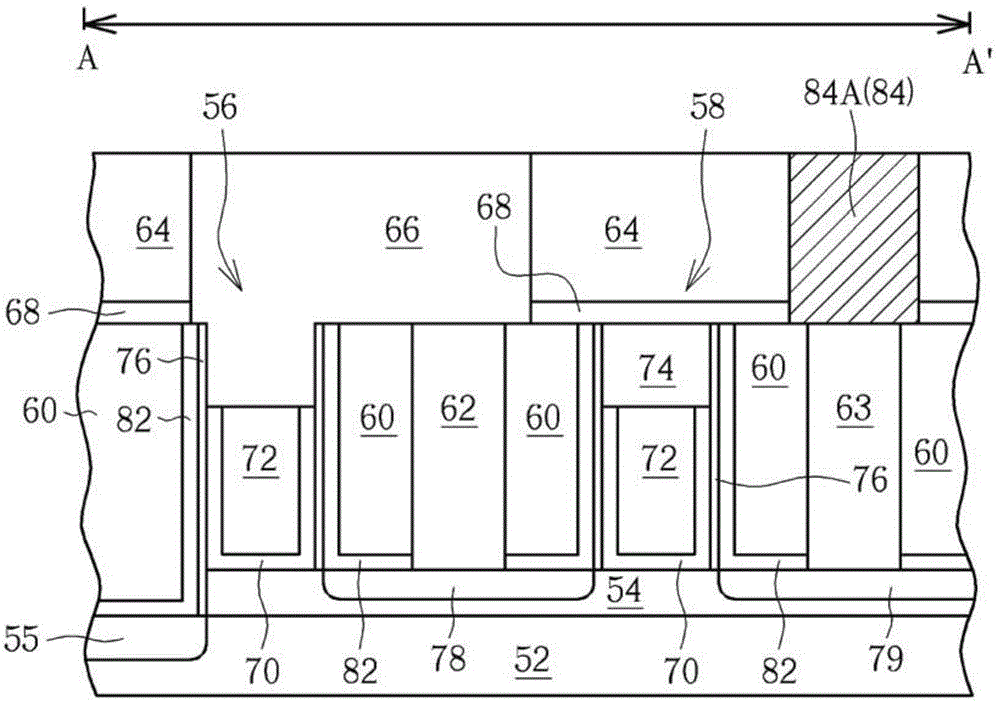

Manufacturing method of buried word line

ActiveCN107968073ASave materialGood hole filling abilityTransistorSemiconductor/solid-state device manufacturingEngineeringMask layer

The invention discloses a manufacturing method of a buried word line. The manufacturing method comprises the steps of providing a substrate firstly, wherein the substrate comprises a plurality of shallow trench isolation parts; next, forming a plurality of first patterned material layers which are positioned above the substrate, wherein a first groove is included between any two adjacent first patterned material layers; next, forming at least one second patterned material layer which is positioned in the first groove; by taking each first patterned material layer and the second patterned material layer as a mask layer, performing a first etching step; and forming a plurality of second grooves at least in the shallow trench isolation parts and the substrate.

Owner:UNITED MICROELECTRONICS CORP +1

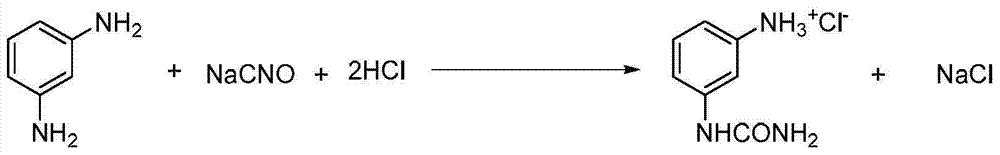

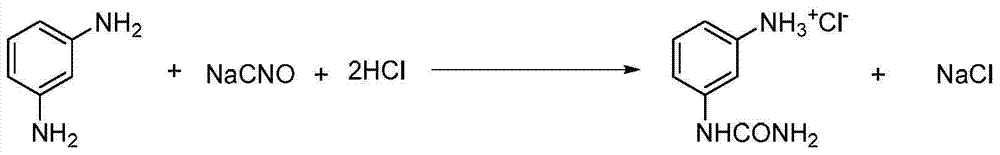

Clean production process of m-carbamidoaniline hydrochloride

ActiveCN103539705AEmission reductionAvoid reactionUrea derivatives preparationOrganic compound preparationReaction temperatureSodium cyanate

The invention discloses a clean production process of m-carbamidoaniline hydrochloride. The clean production process comprises the following steps of: dissolving m-phenylenediamine into a sodium chloride salt water reaction system; adding an auxiliary agent into the reaction system; controlling a reaction temperature at -5 DEG C to 25 DEG C; then adding sodium cyanate and hydrochloric acid for reaction; and after the reaction is completed, carrying out post-treatment on a resulting substance to obtain m-carbamidoaniline hydrochloride, wherein the auxiliary agent is nitric acid or nitrate. According to the clean production process, salt water, instead of pure water, is used as base water, m-carbamidoaniline hydrochloride produced in the reaction can be separated out in time by using salt precipitation effects of sodium chloride, a byproduct diurea is not generated, the purity of the obtained m-carbamidoaniline hydrochloride is more than 98%, the yield is more than 95%, the content is 75%-80%, the sewage quantity is reduced by 50%, and the process is simple and high in automation degree.

Owner:ZHEJIANG RUNTU INST

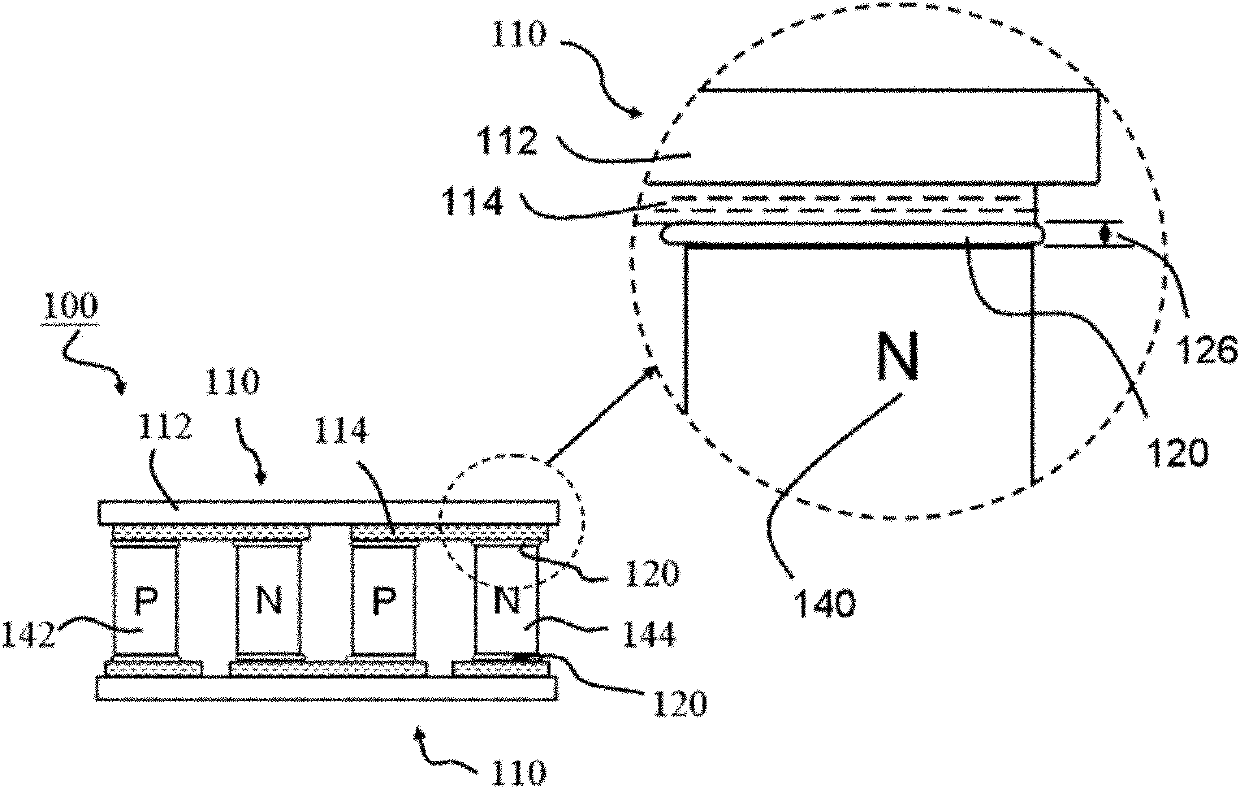

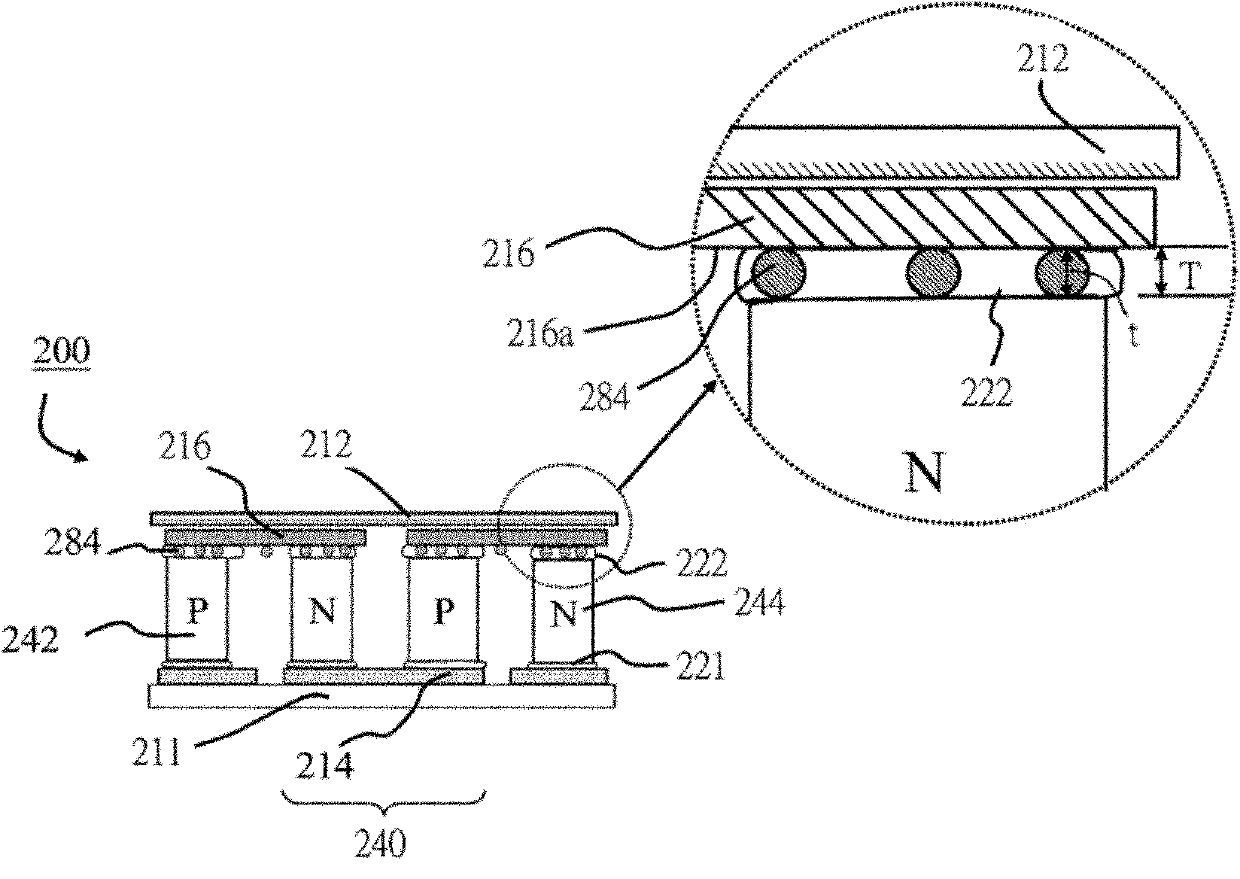

Thermoelectric module and manufacture method thereof

InactiveCN102569629AReduce thicknessHigh operational reliabilityThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentThermoelectric materialsElectricity

The invention discloses a thermoelectric module and a manufacture method of the thermoelectric module. The thermoelectric module comprises a first base plate, a second base plate, a plurality of P type thermoelectric materials, a plurality of N type thermoelectric materials, first metal electrodes, second metal electrodes, first welding alloy layers, second welding alloy layers and a support object, wherein the thermoelectric materials are arranged between the first base plate and the second base plate and each pair of thermoelectric materials comprises a P type thermoelectric material and an N type thermoelectric material which are electrically connected through the first metal electrode (positioned between the first base plate and the lower end surface of the thermoelectric materials), and the N type thermoelectric material is then electrically connected with the other adjacent P type thermoelectric material through the second metal electrode (positioned between the second base plate and the upper end surface of the thermoelectric materials). The first welding alloy layers are connected with the first metal electrodes and the lower end surfaces of the P / N type thermoelectric materials, and the second welding alloy layers are connected with the second metal electrodes and the upper end surfaces of the P / N type thermoelectric materials. The support object is positioned in a position of at least one of the first welding alloy layers and the second welding alloy layers, and in addition, the melting point is higher than the liquid phase line temperature of the first welding alloy layers and the second welding alloy layers.

Owner:IND TECH RES INST

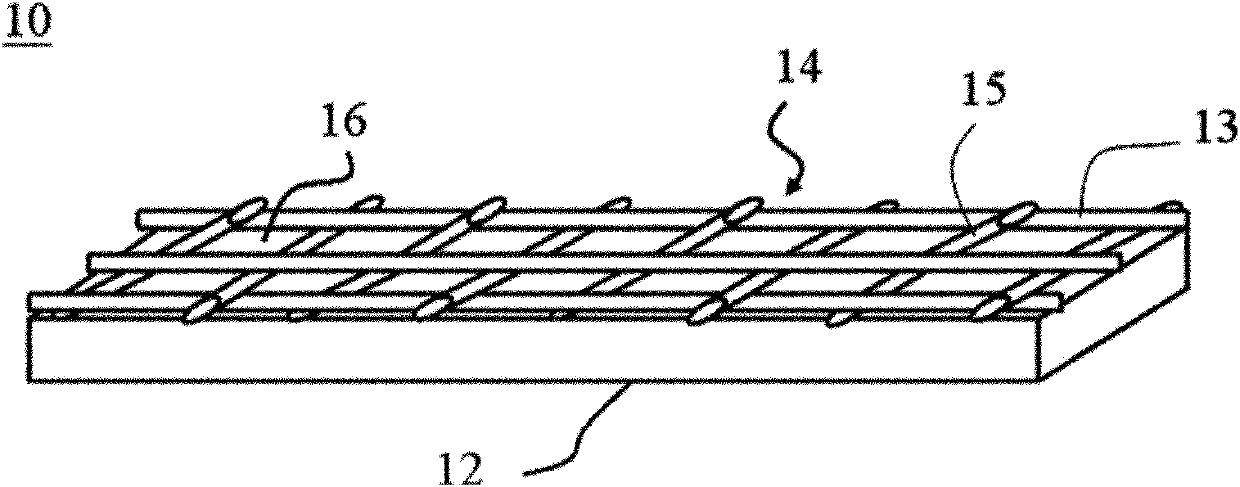

Display module and method for manufacturing same

ActiveCN104009058AReduce thicknessReduce weightSolid-state devicesSemiconductor/solid-state device manufacturingEngineering

Owner:HTC CORP

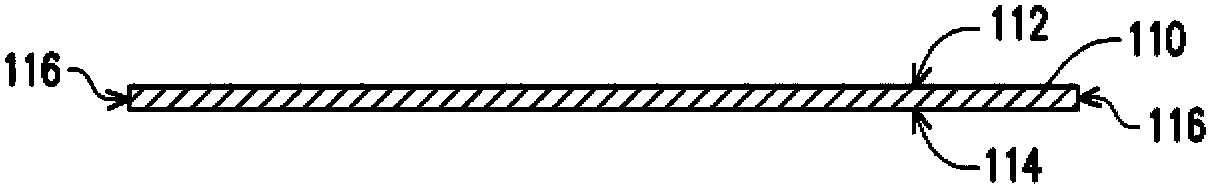

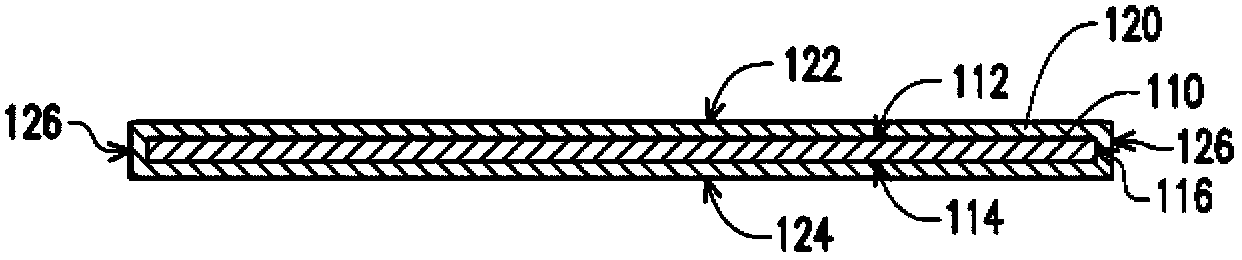

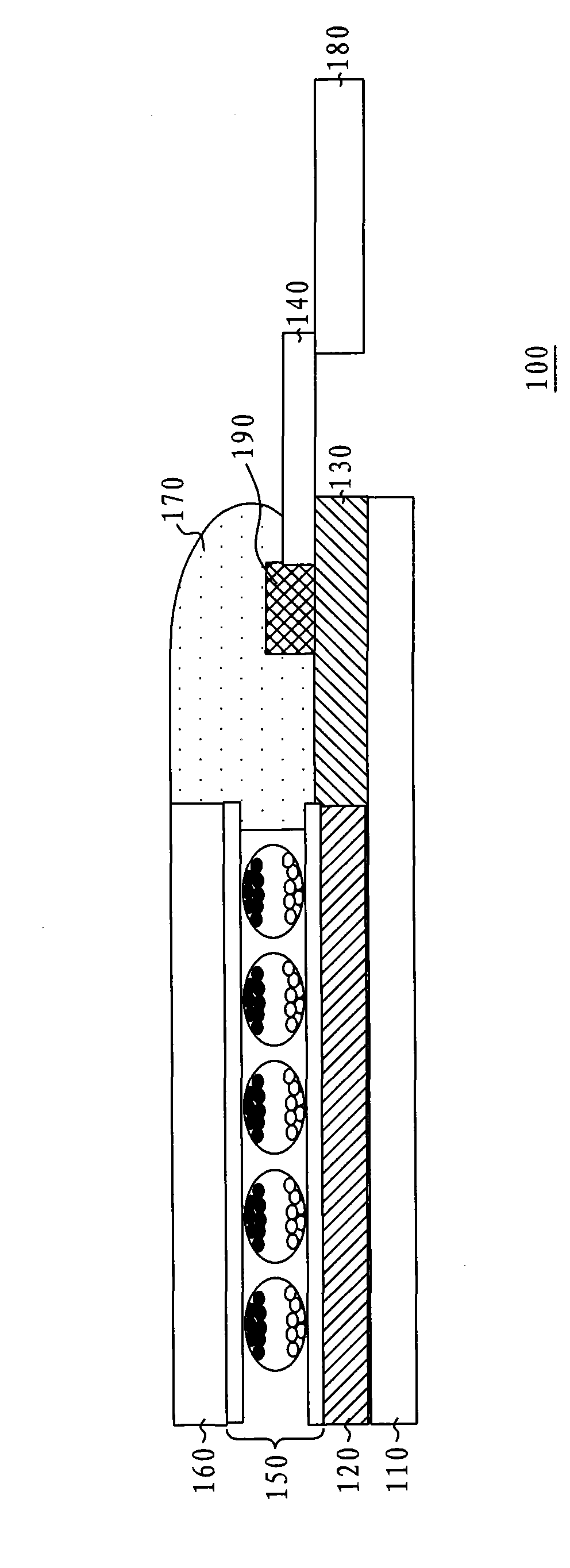

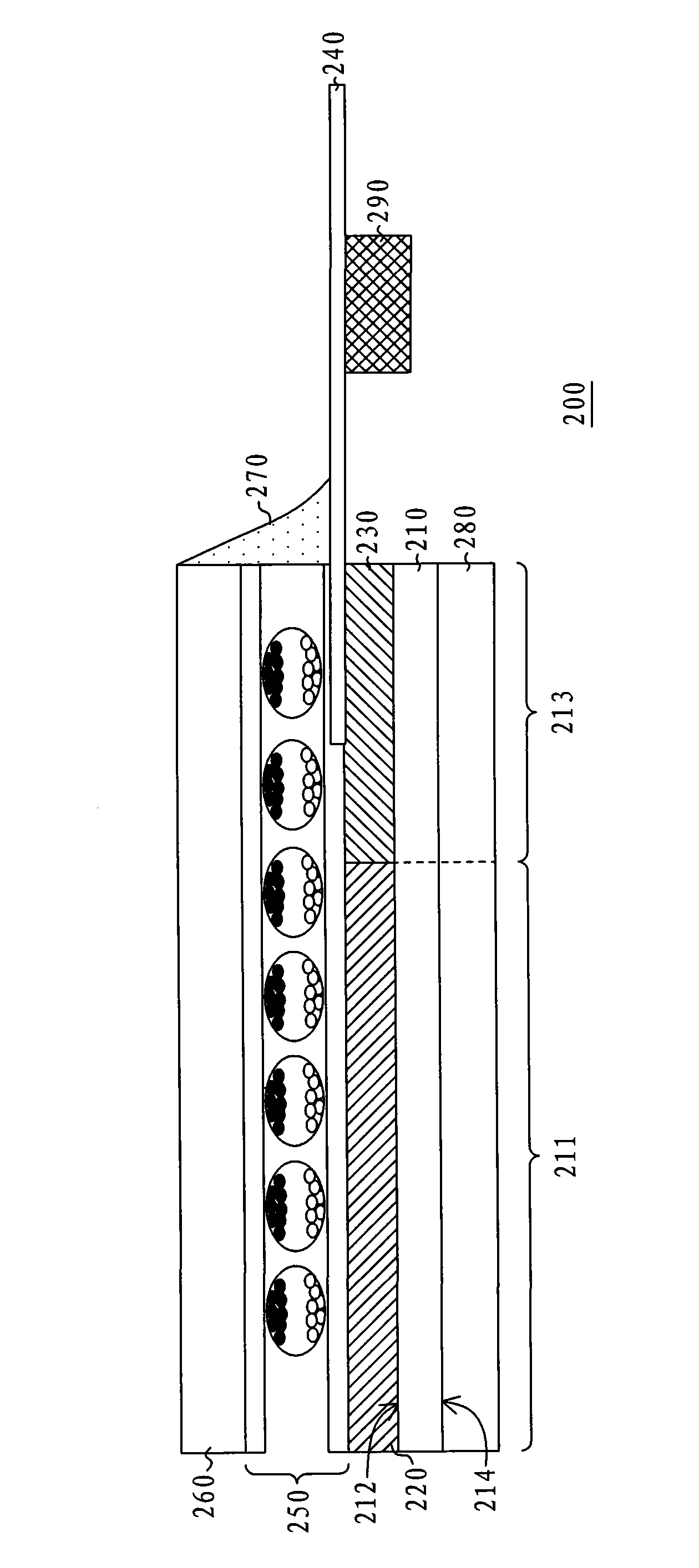

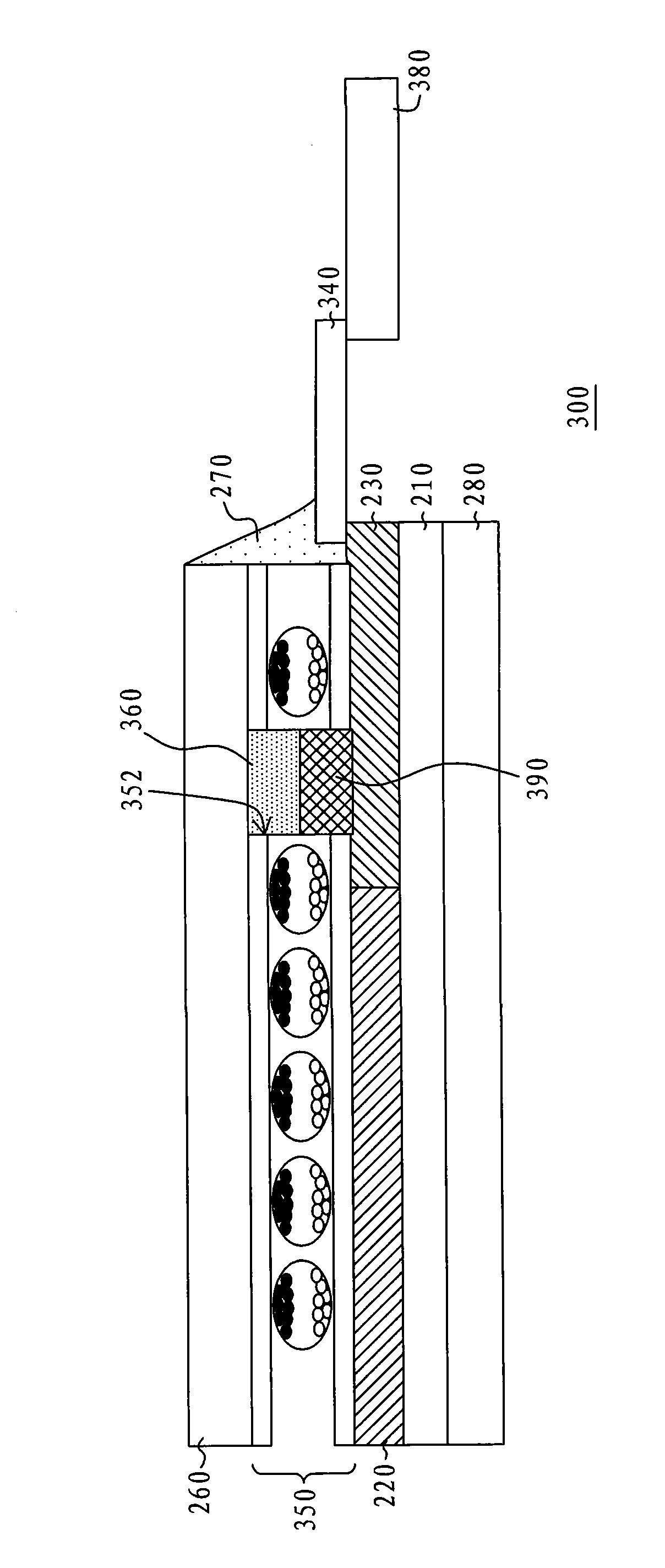

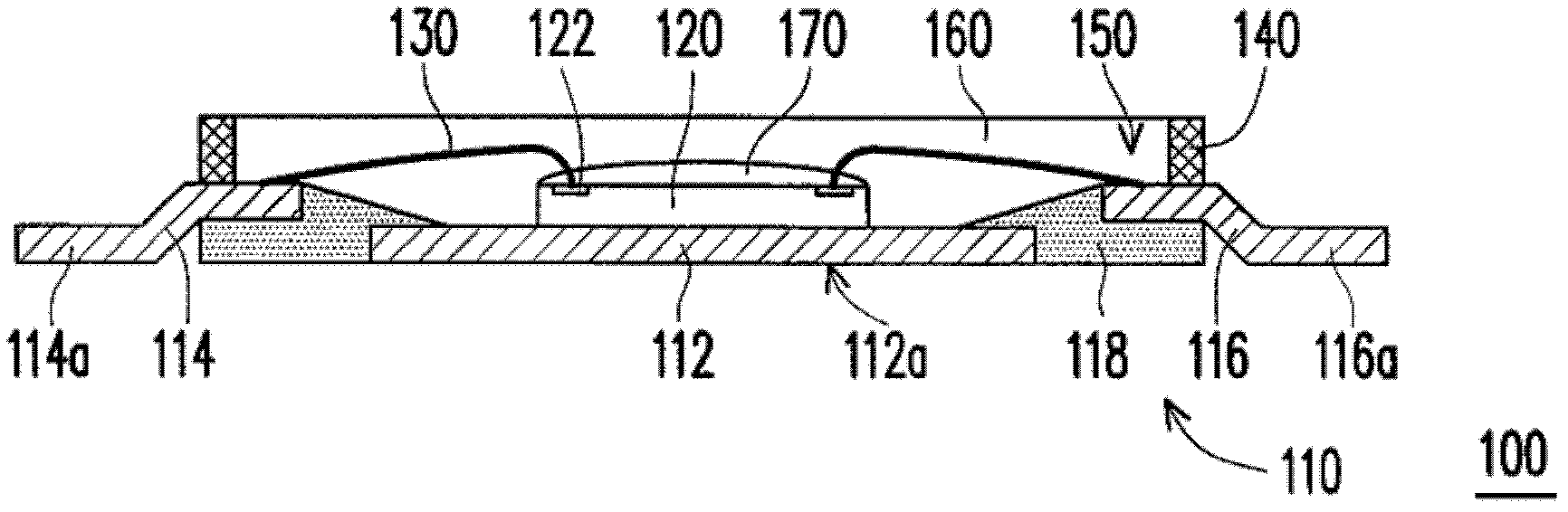

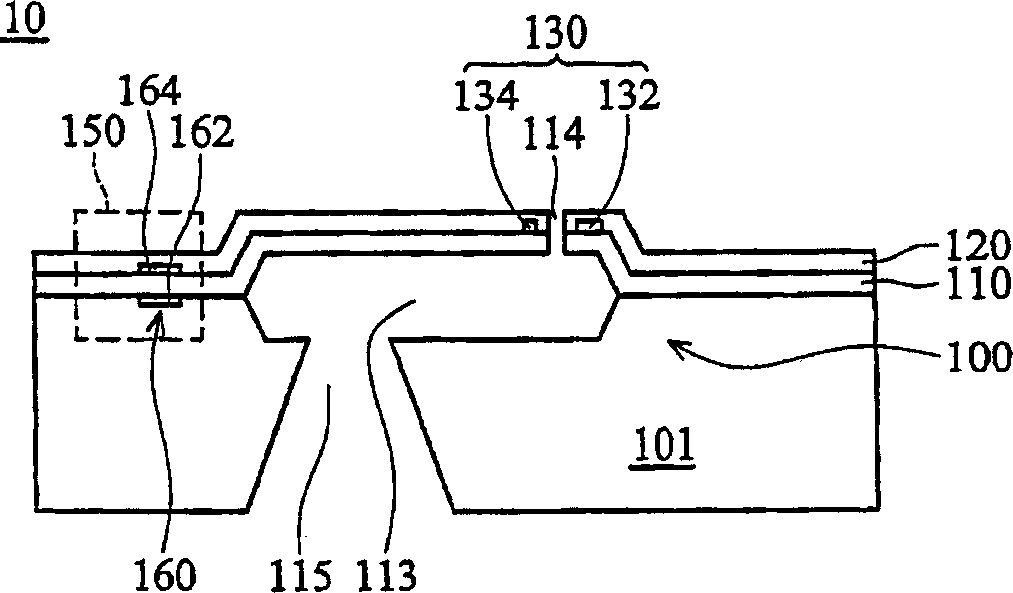

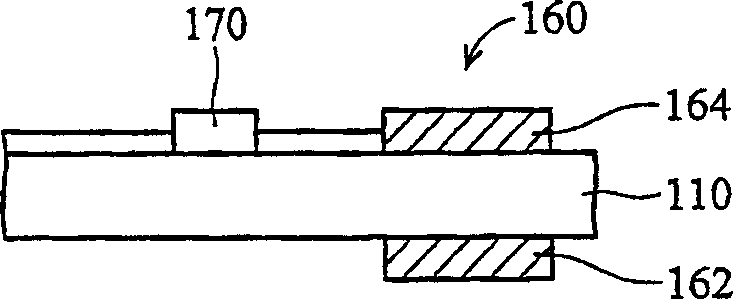

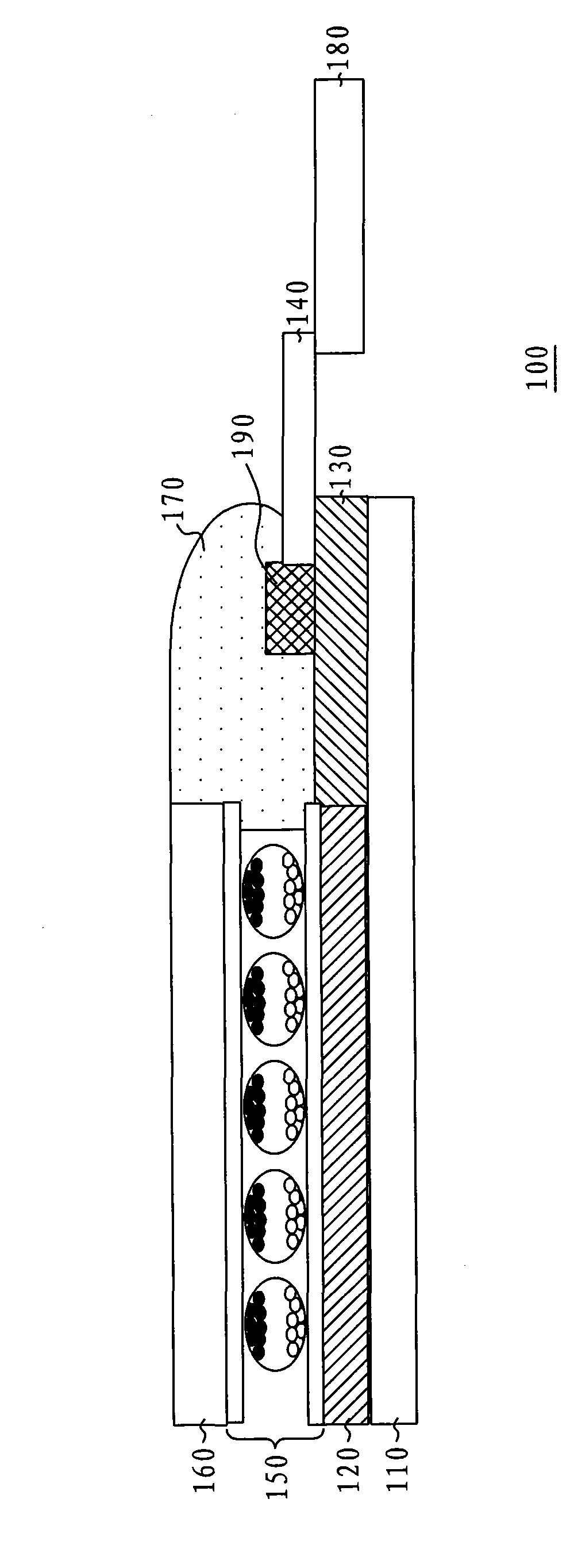

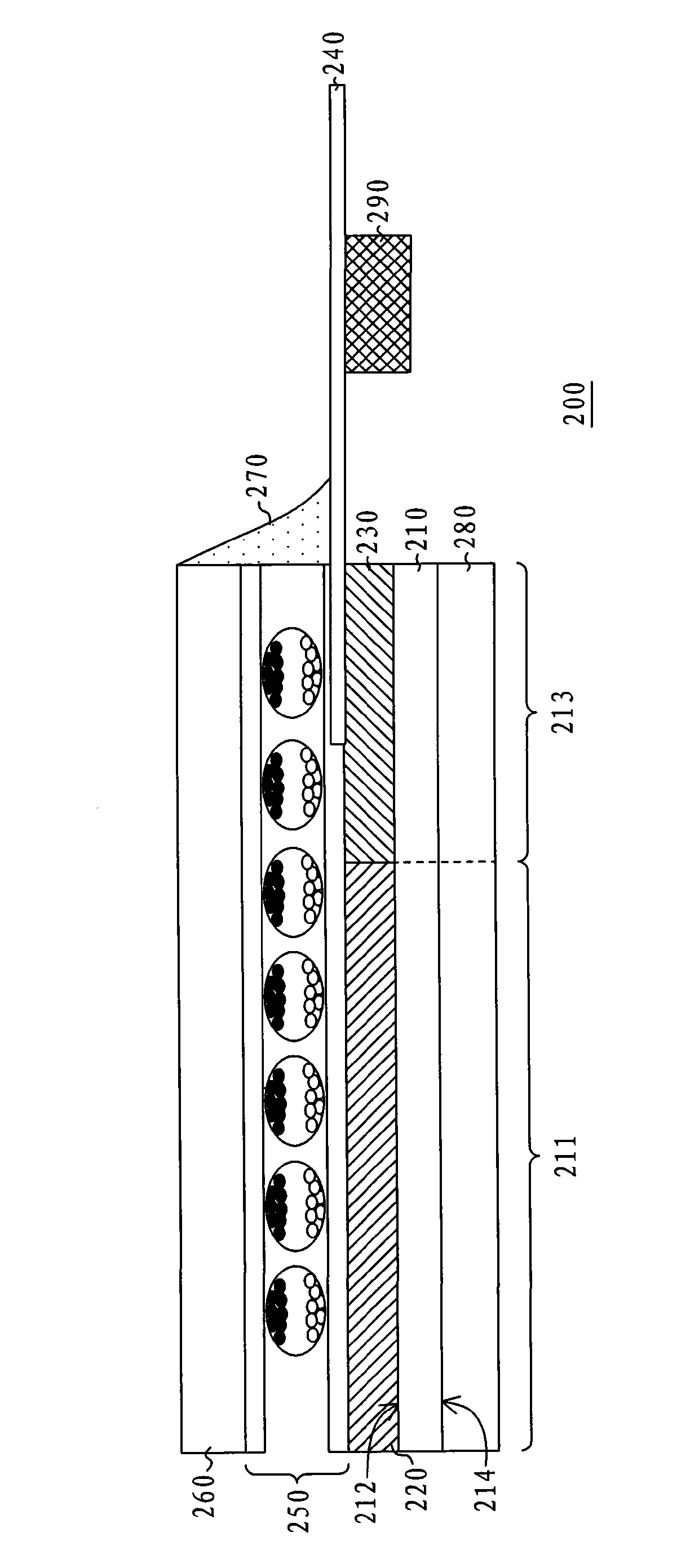

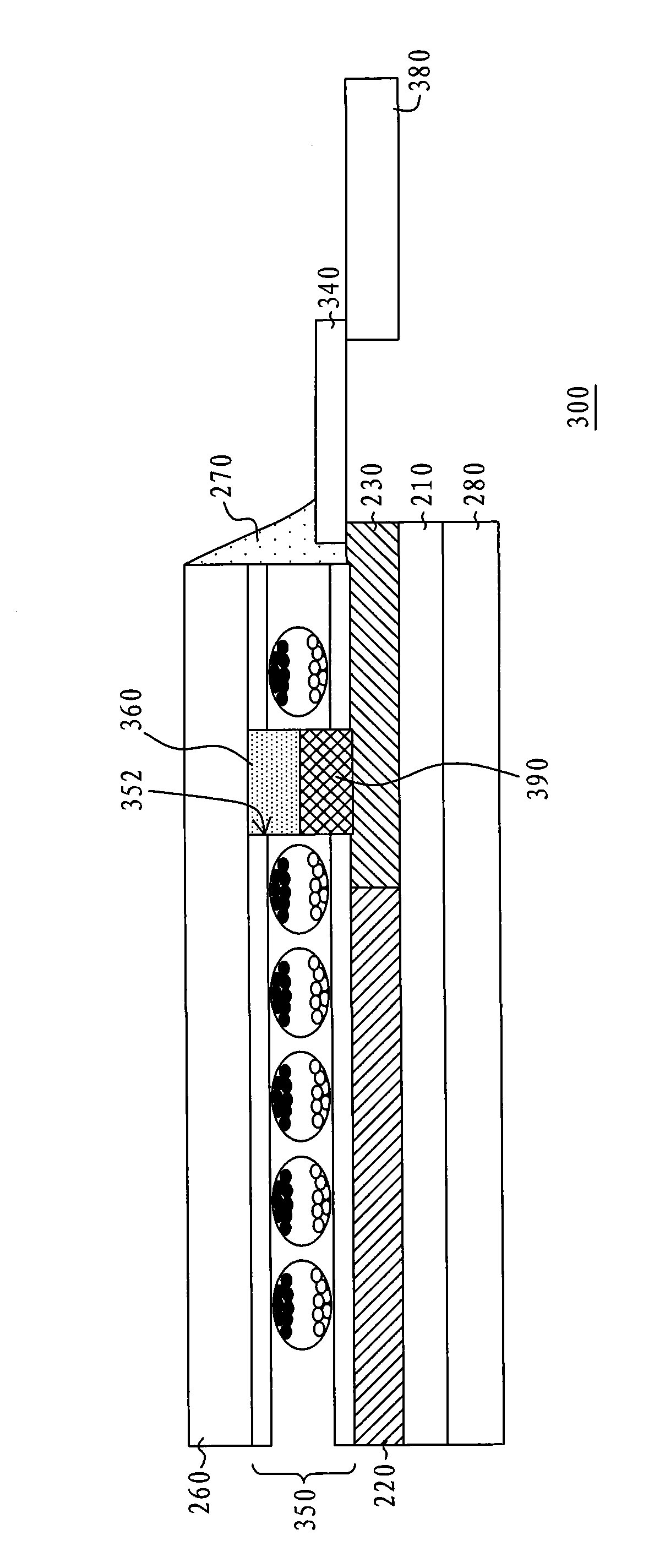

Electrophoretic display and manufacturing method thereof

ActiveCN102109727AExtended service lifeImprove production process yieldNon-linear opticsActive componentFlexible circuits

The invention relates to an electrophoretic display and a manufacturing method thereof. The electrophoretic display comprises a first base plate, an active component array, a driving circuit, a flexible printed circuit, an electrophoretic display layer, a second base plate and a driving chip. The first base plate is provided with a first surface which is provided with a display region and a line region. The active component array is arranged in the display region, the driving circuit is arranged in the line region and is electrically connected to the active component array, and an electric conduction flexible circuit is partially arranged on the first base plate and is electrically connected to the driving circuit. The electrophoretic display layer and the second base plate are arranged on the active component array and the driving circuit sequentially, and the sealing compound is adhered between the second base plate and the electric conduction flexible circuit to tightly seal the electrophoretic display layer between the first base plate and the second base plate. The driving chip is connected with the diving circuit, and the electrophoretic display layer comprises an opening to expose the driving chip. The invention also discloses a manufacturing method of the electrophoretic display.

Owner:E INK HLDG INC

Touch control display device

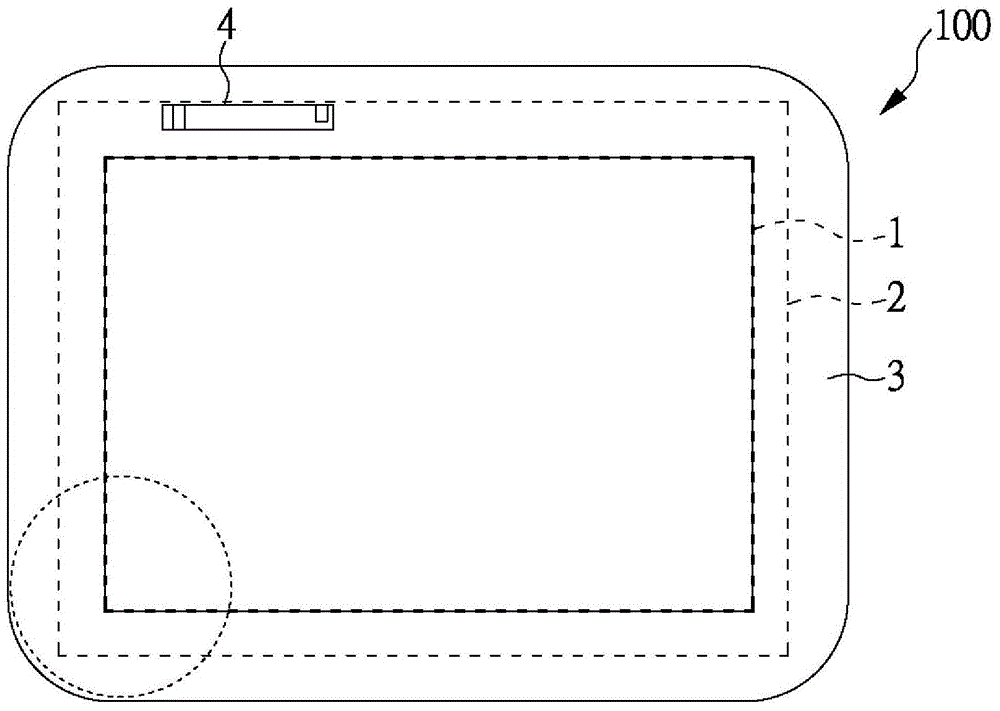

ActiveCN104679316AAvoid electrostatic damageAverage dispersionInput/output processes for data processingDisplay deviceComputer science

A touch control display device comprises a display device and a touch control panel; the touch control panel is arranged on one side of the display device, wherein the touch control panel comprises a substrate, a light shield layer, and a circuit layer, the light shield layer is arranged between the substrate and the display device. The circuit layer is arranged between the light shield layer and the display device; and the circuit layer comprises a first signal electrode and a second signal electrode. The first signal electrode has a first overlapped area and a first non-overlapped area. The second signal electrode has a second overlapped area and a second non-overlapped area, wherein the first overlapped area and the second overlapped area are overlapped with the light shield layer; and the distance between the first overlapped area and the second overlapped area is greater than the distance between the first non-overlapped area and the second non-overlapped area.

Owner:INNOLUX CORP

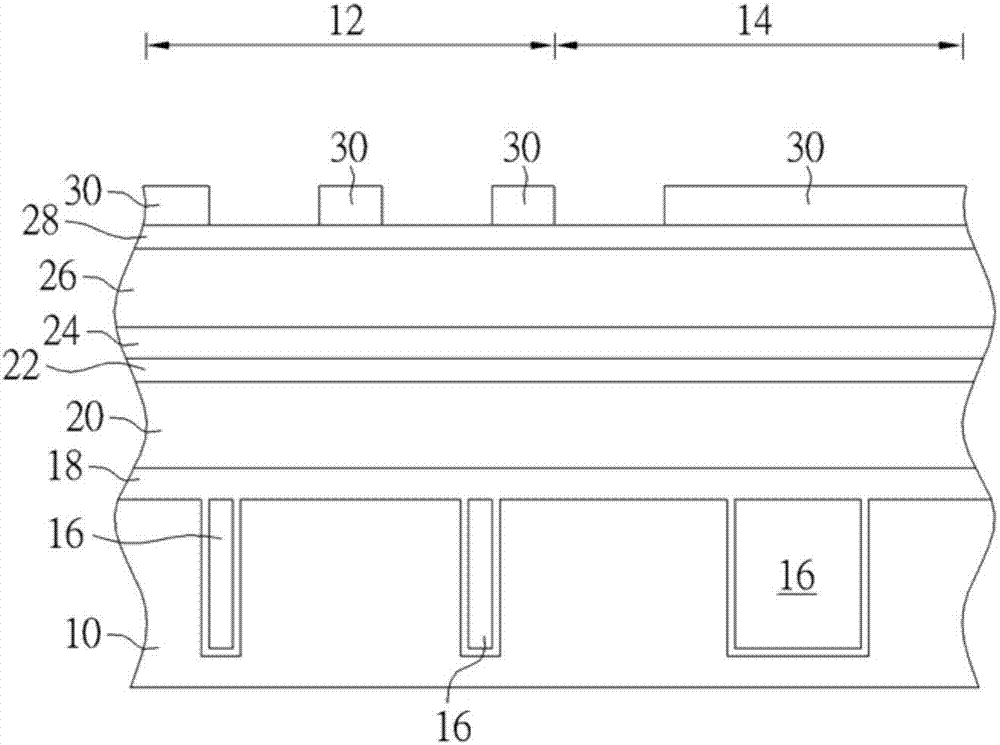

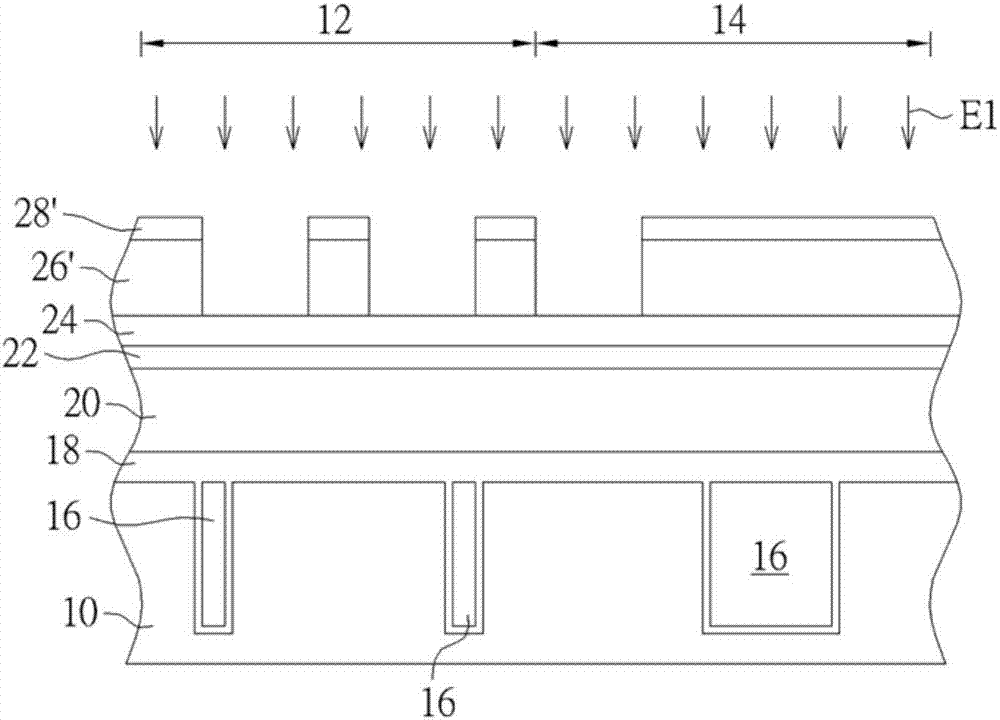

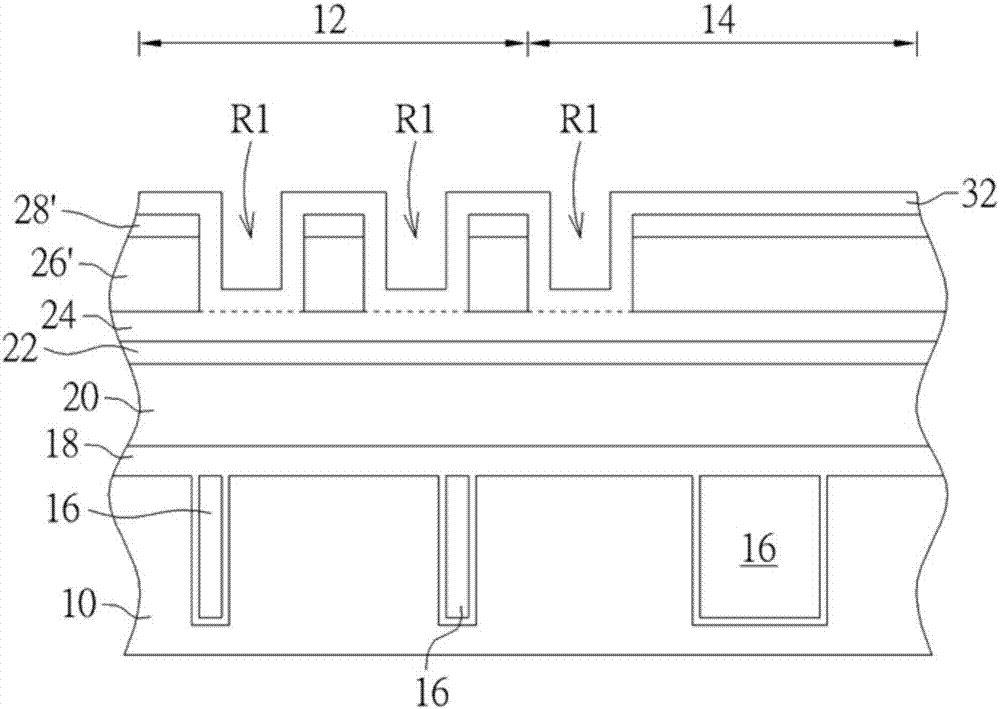

Semiconductor element manufacturing method

InactiveCN106298656ASimple manufacturing processImprove production process yieldSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionPhotoresist

The present invention discloses a semiconductor element manufacturing method. First, a substrate with a first transistor structure and a second transistor structure is provided, wherein the first transistor structure is provided with a first gate trench, and the second transistor structure is provided with a second gate trench. Then, a first work function metal layer is formed in the first gate trench and the second gate trench, and a flat layer is formed on the first work function metal layer. Then, a patterned photoresist layer is formed on the flat layer, and a part of the flat layer on the second transistor structure is etched. Then, after the patterned photoresist layer is removed, the flat layer is fully etched until the flat layer on the second transistor structure is completely removed, and a patterned flat layer is kept to cover the first transistor structure. Finally, the first work function metal layer in the second gate trench is removed.

Owner:UNITED MICROELECTRONICS CORP

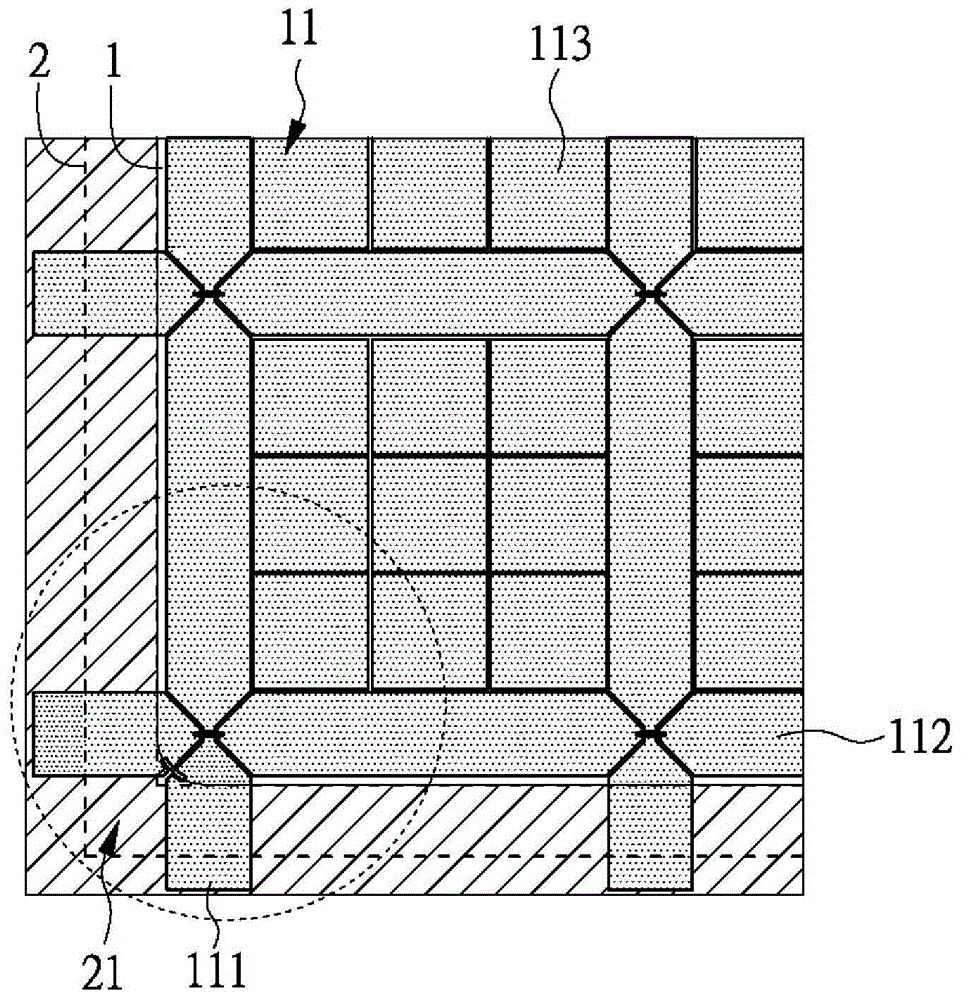

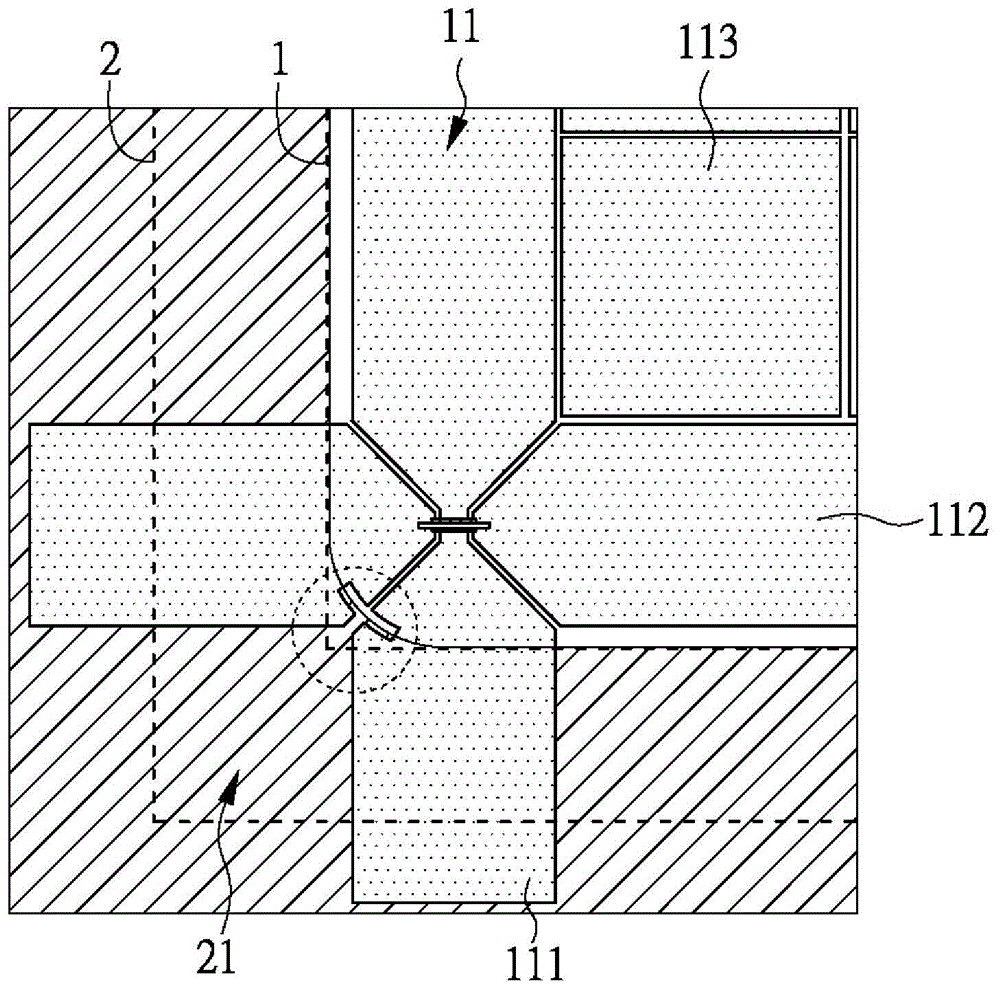

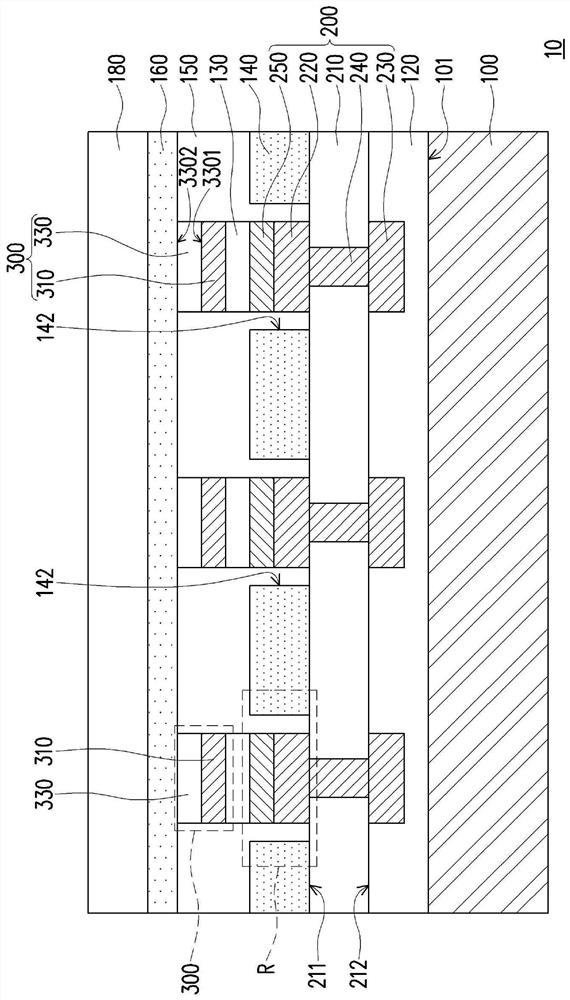

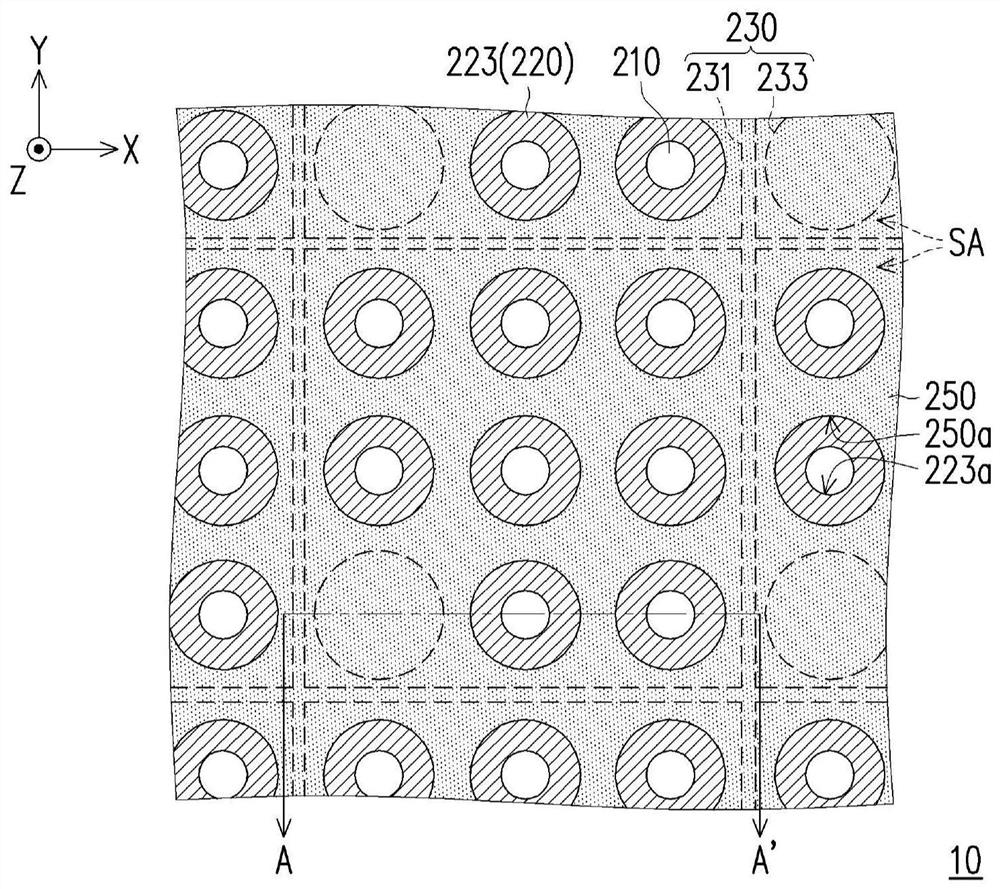

Semiconductor component and manufacturing method thereof

The invention discloses a semiconductor component and a manufacturing method thereof. The semiconductor component comprises a substrate which defines at least one storage area, a mesh type isolation structure formed on the substrate and storage electrode contact plugs. Multiple storage units are arranged in the storage area. The mesh type isolation structure comprises multiple basically homogeneous dielectric sidewalls and first openings defined by the dielectric sidewalls. The storage electrode contact plugs are arranged in the first openings and electrically connected with the storage unitsrespectively.

Owner:UNITED MICROELECTRONICS CORP +1

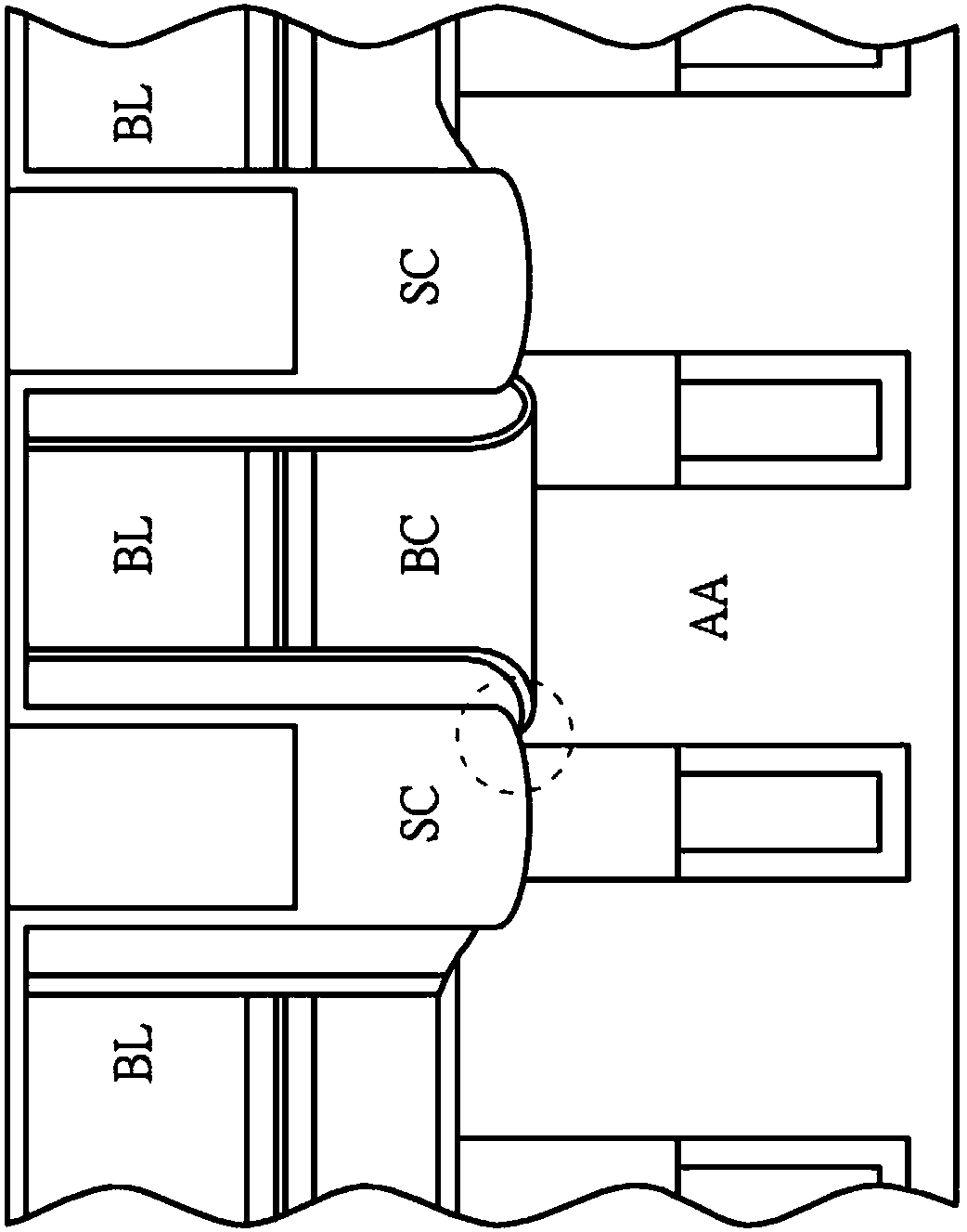

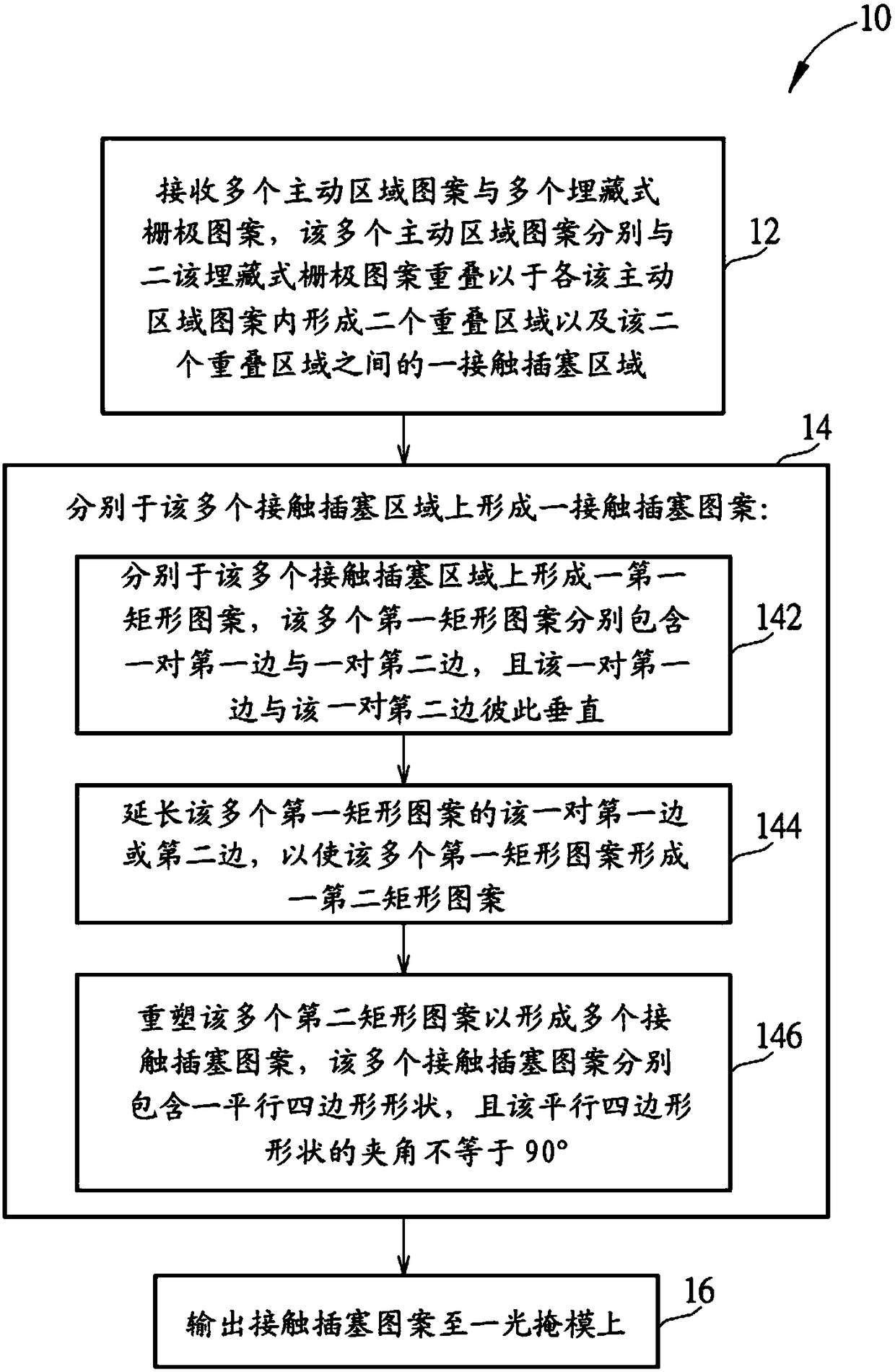

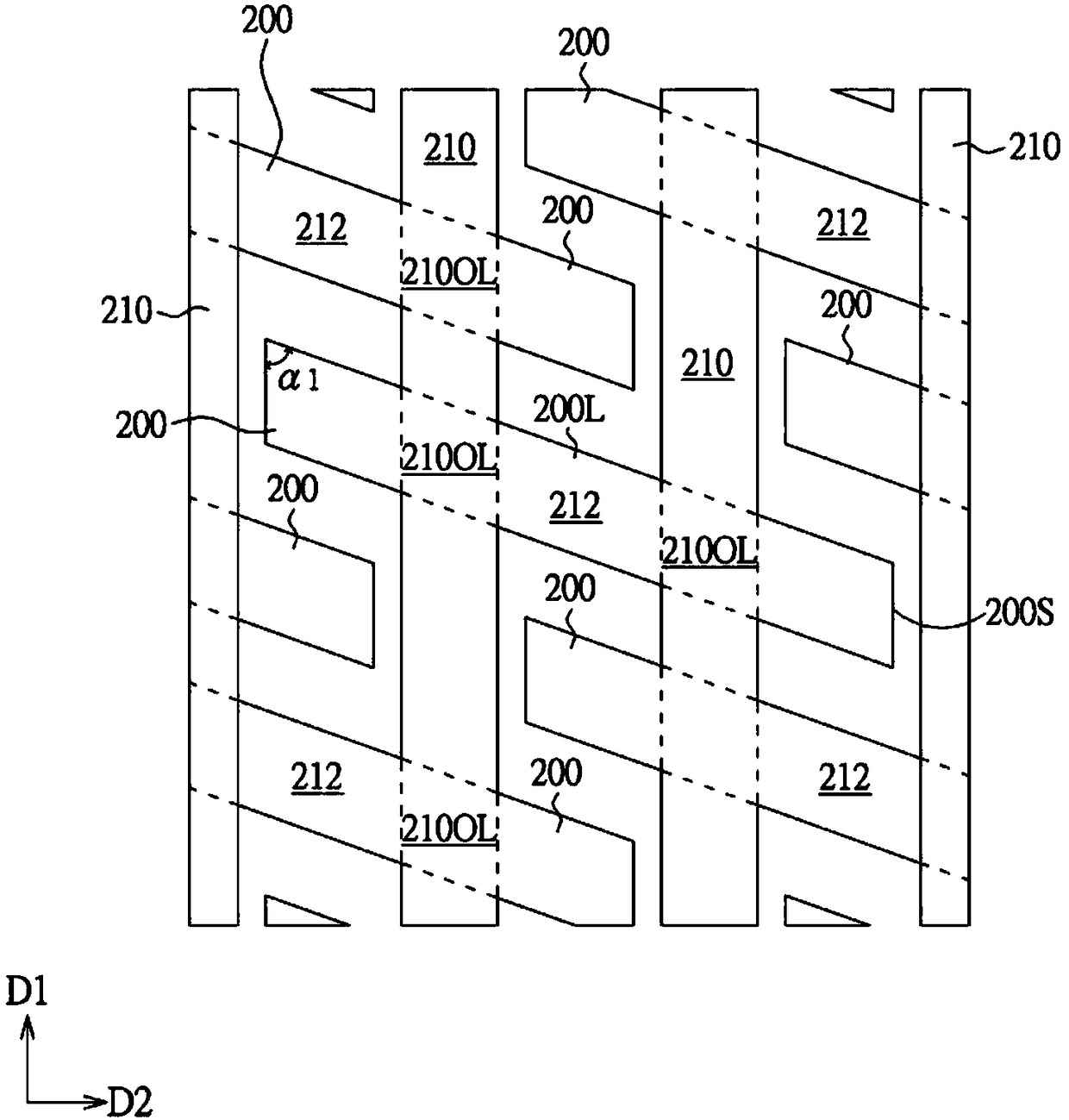

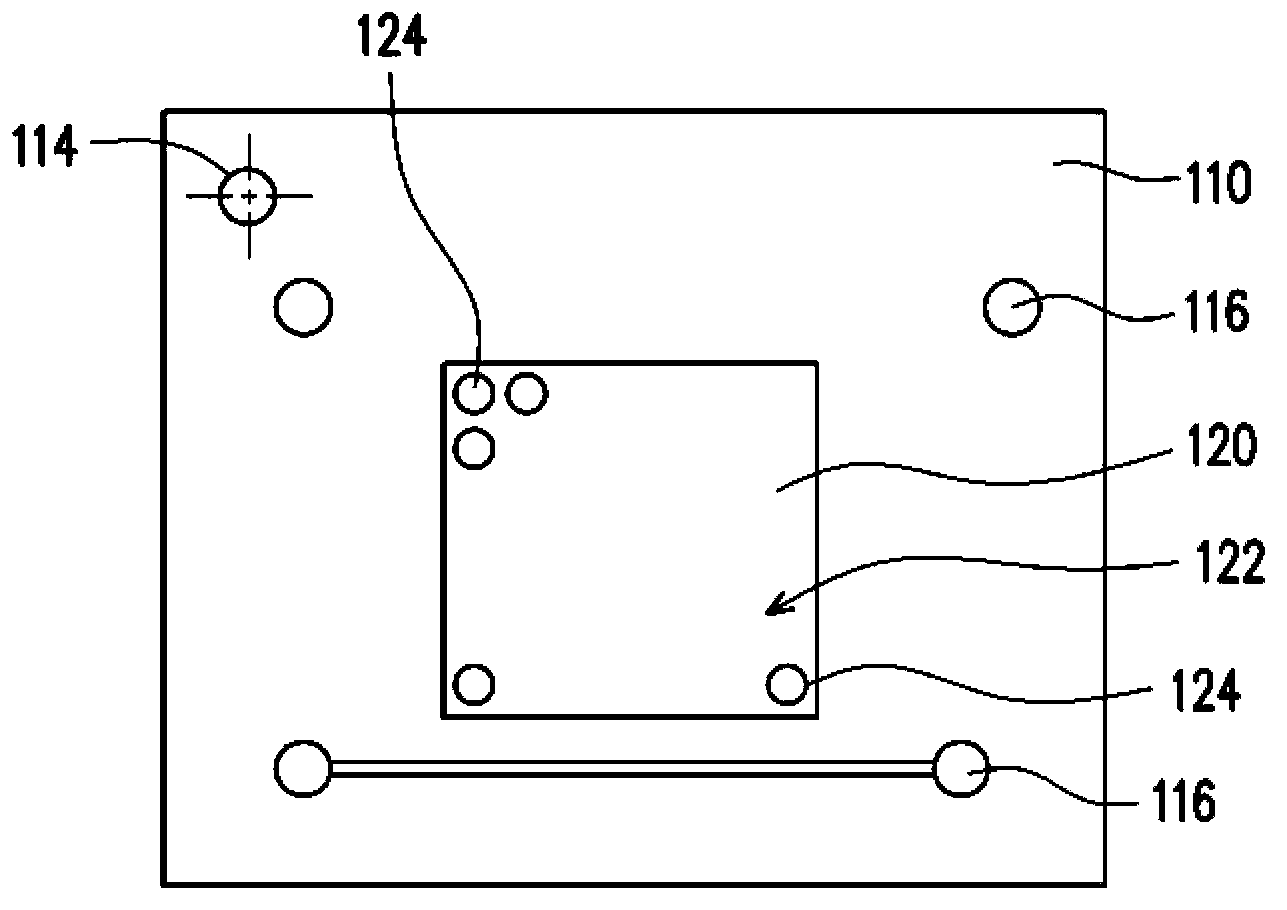

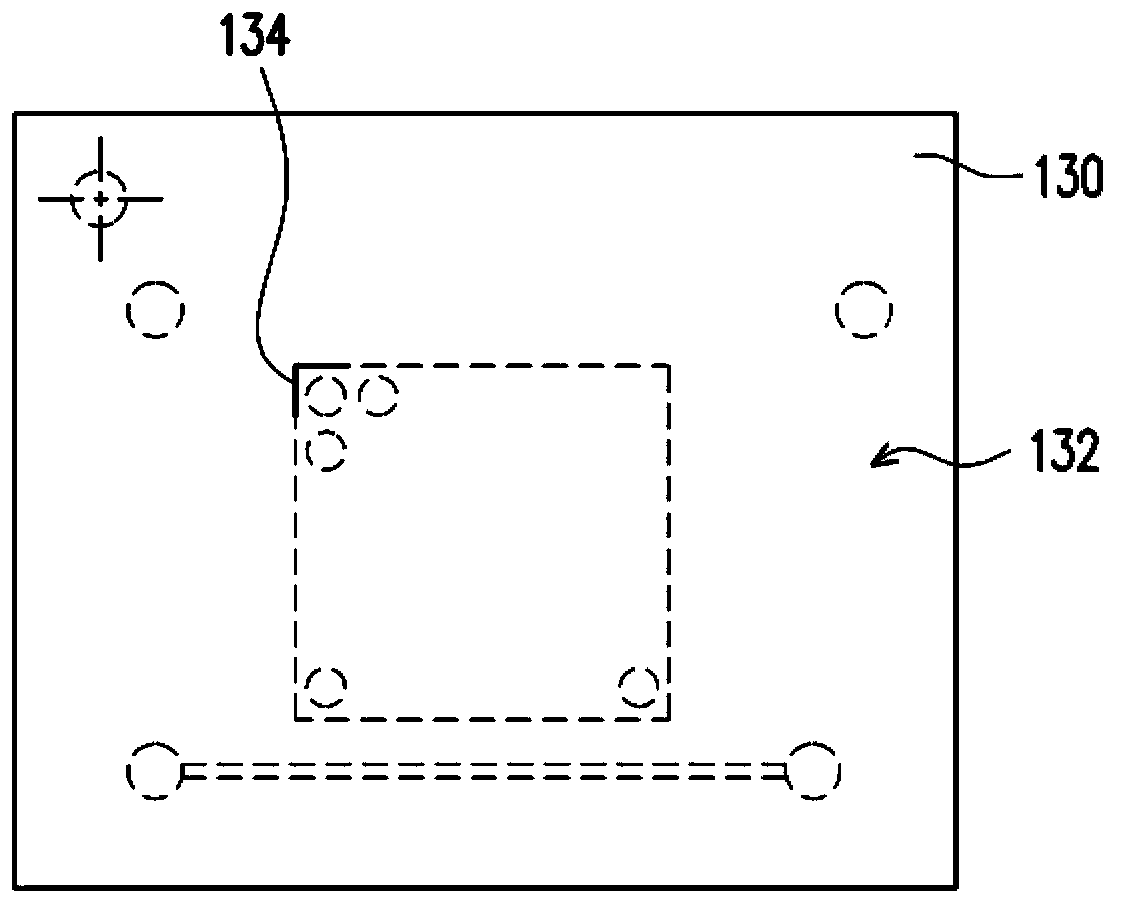

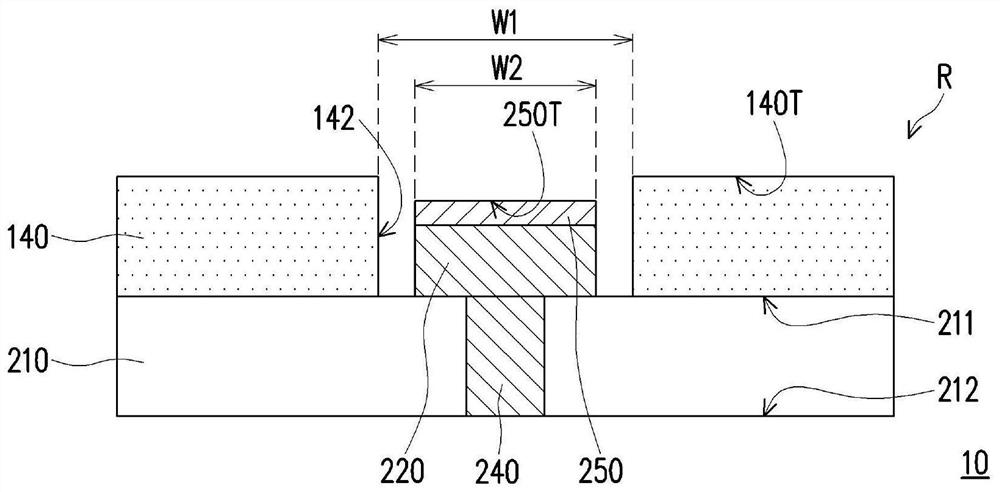

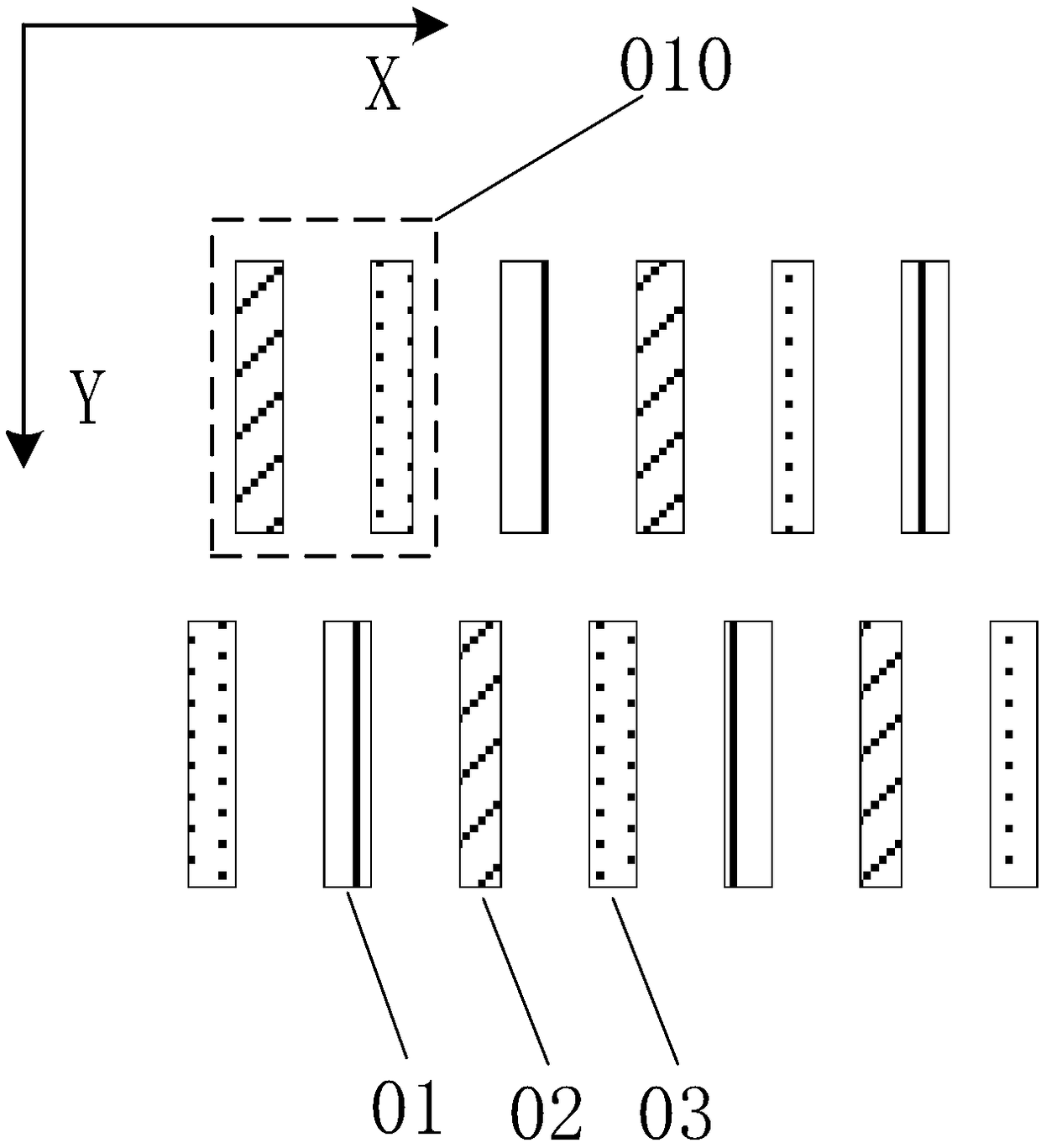

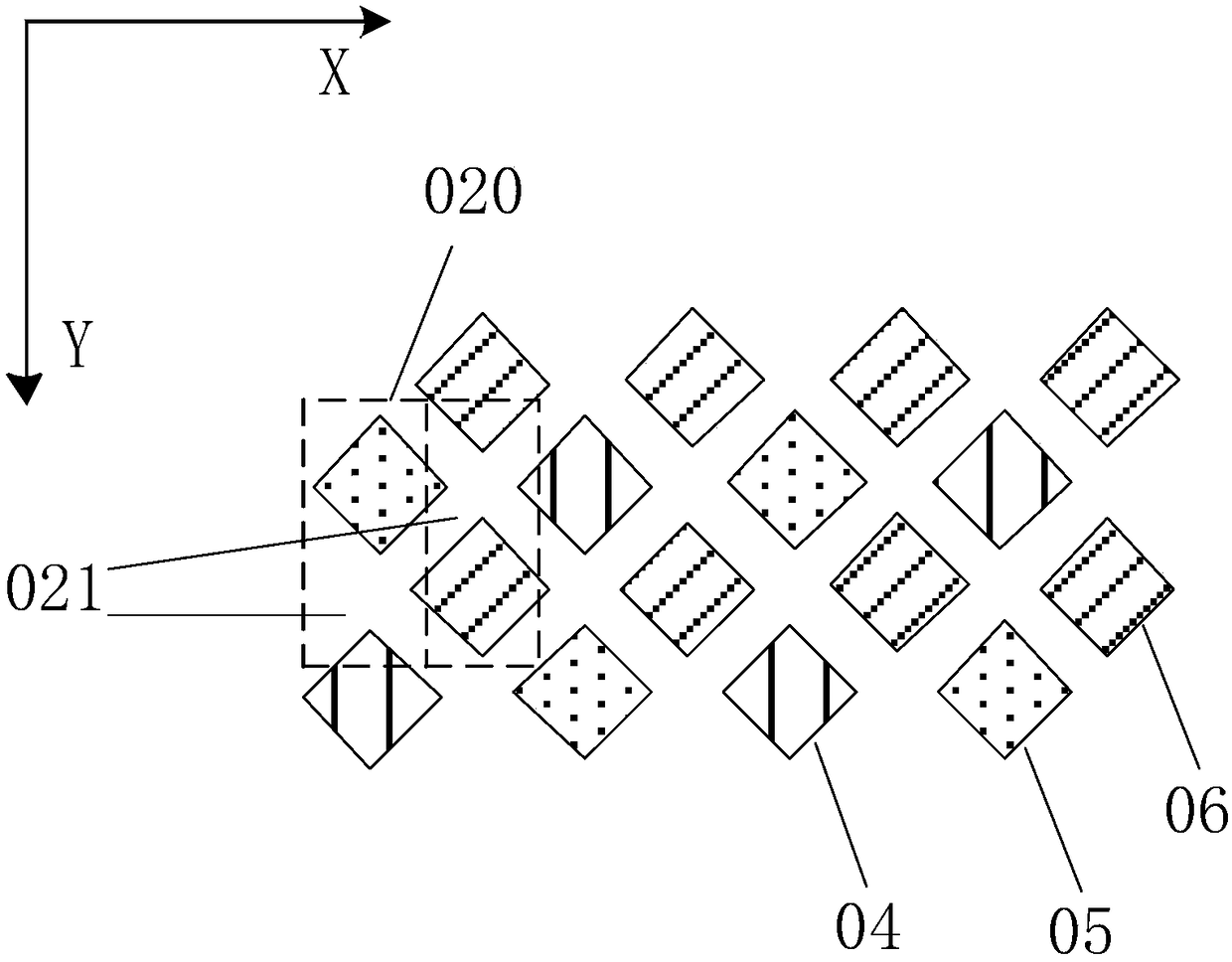

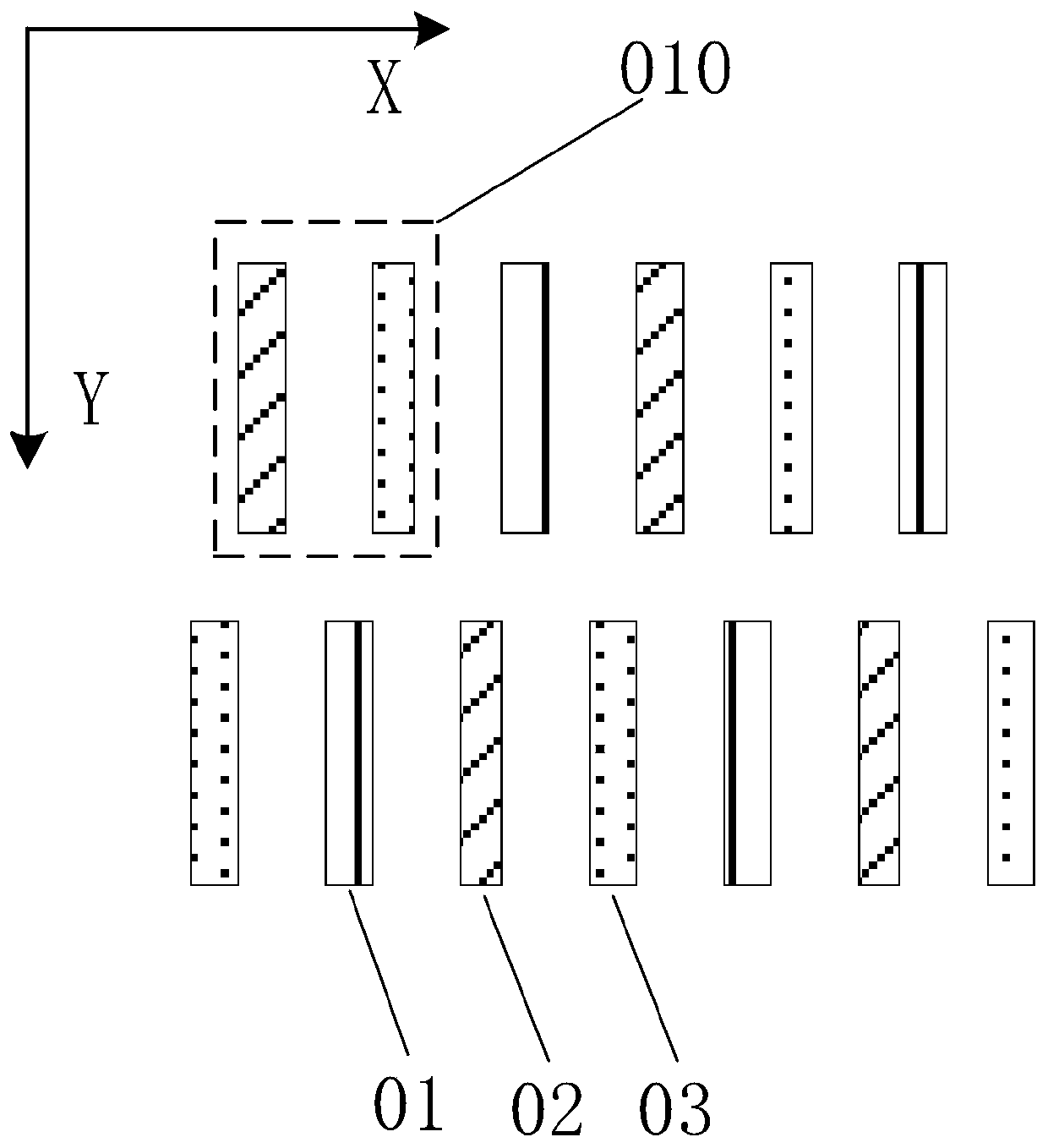

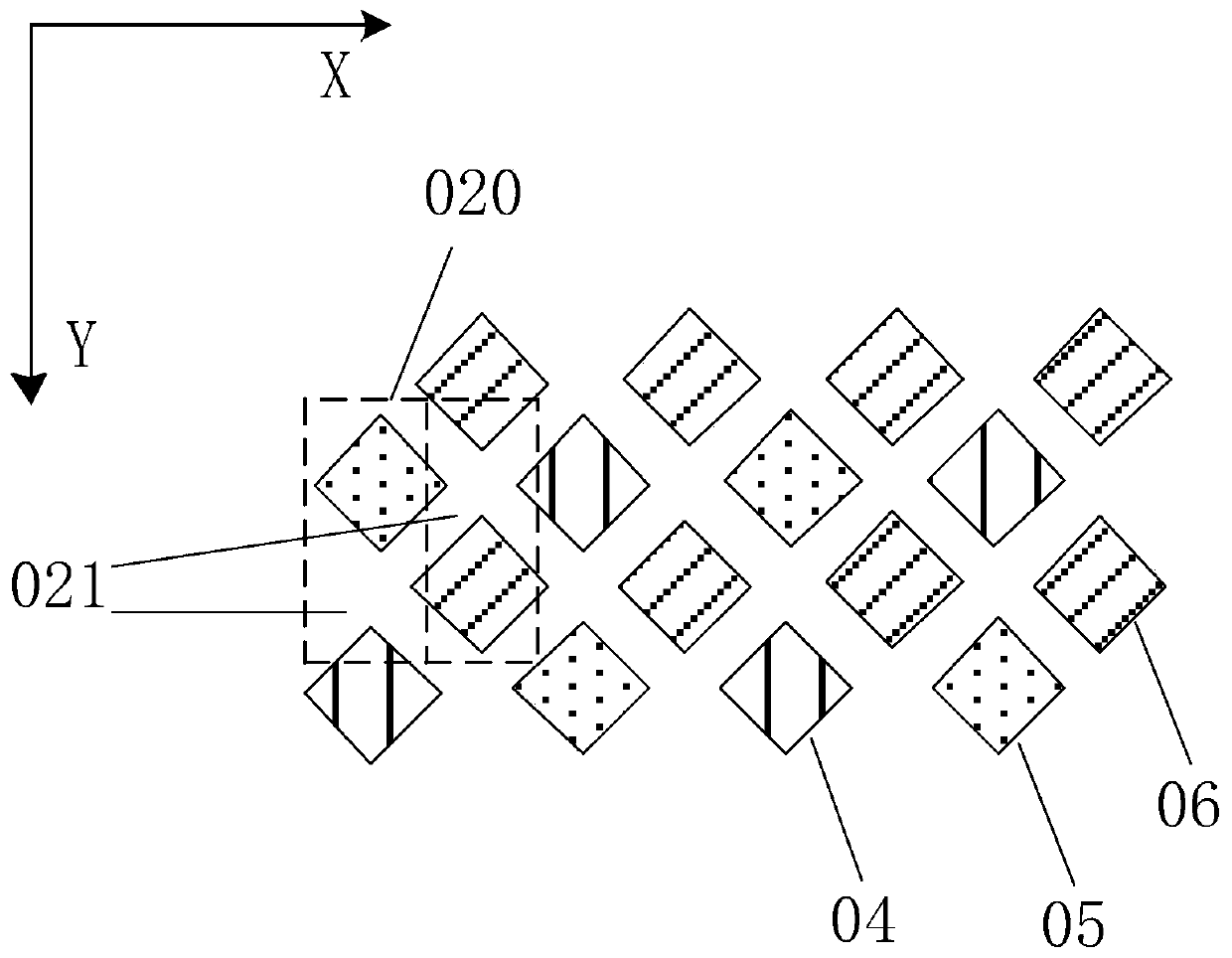

Manufacturing method for contact plug layout

ActiveCN108573079AImprove production process yieldTransistorSolid-state devicesParallelogramElectrical and Electronics engineering

The invention discloses a manufacturing method for a contact plug layout. The manufacturing method comprises the following steps of (a) receiving a plurality of active area patterns and a plurality ofburied gate patterns parallel to one another, wherein each active area pattern overlaps the two buried gate patterns separately to form two overlapping areas in the active area pattern and a contactplug area between the two overlapping areas; (b) forming contact plug patterns on the contact plug areas respectively, wherein the contact plug patterns comprise a parallelogram shape, the inner angleof the parallelogram shape is not equal to 90 degrees, the contact plug patterns overlap parts of buried gate patterns in all active areas respectively, and the step (a) and step (b) are conducted inone computer device.

Owner:UNITED MICROELECTRONICS CORP +1

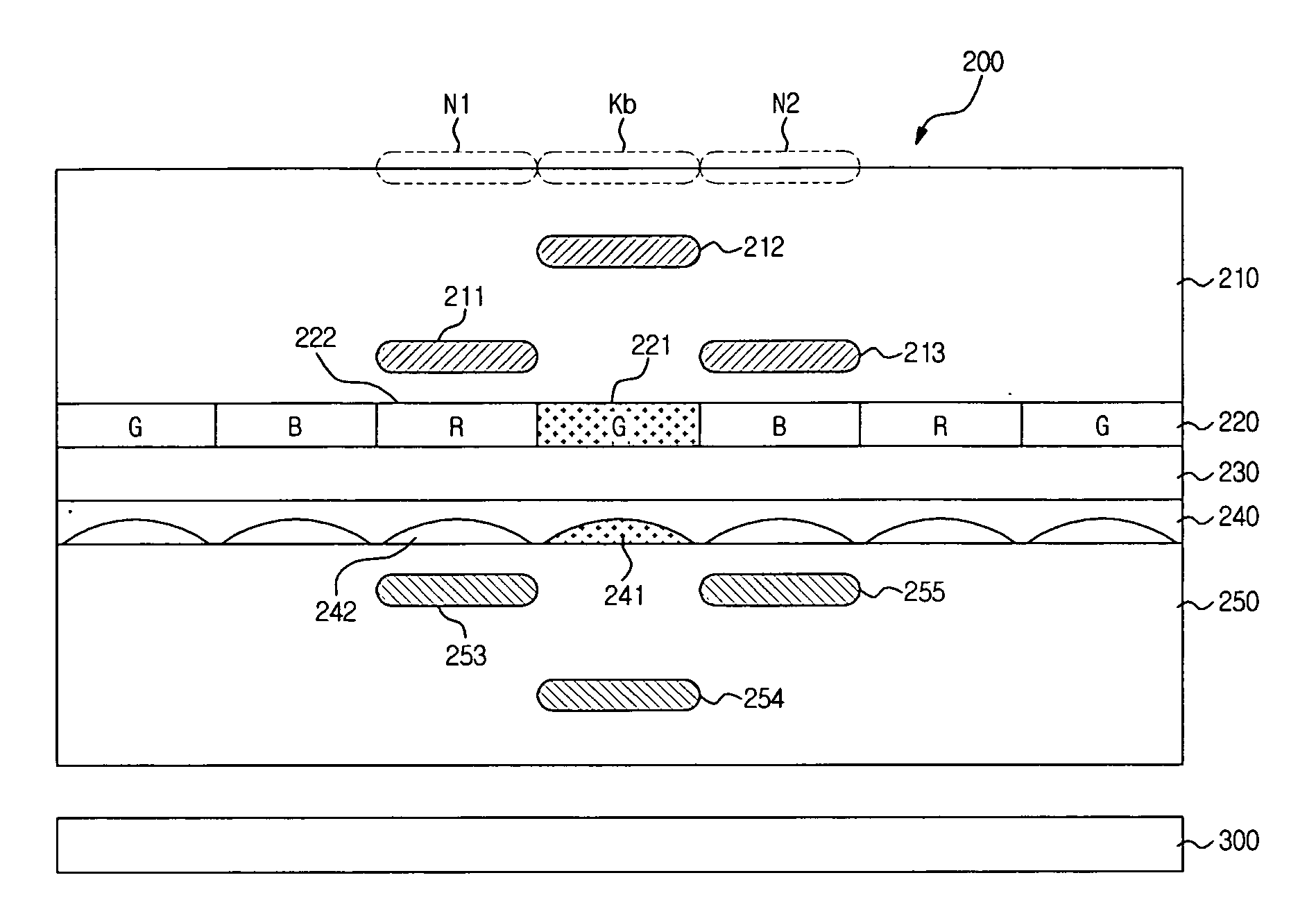

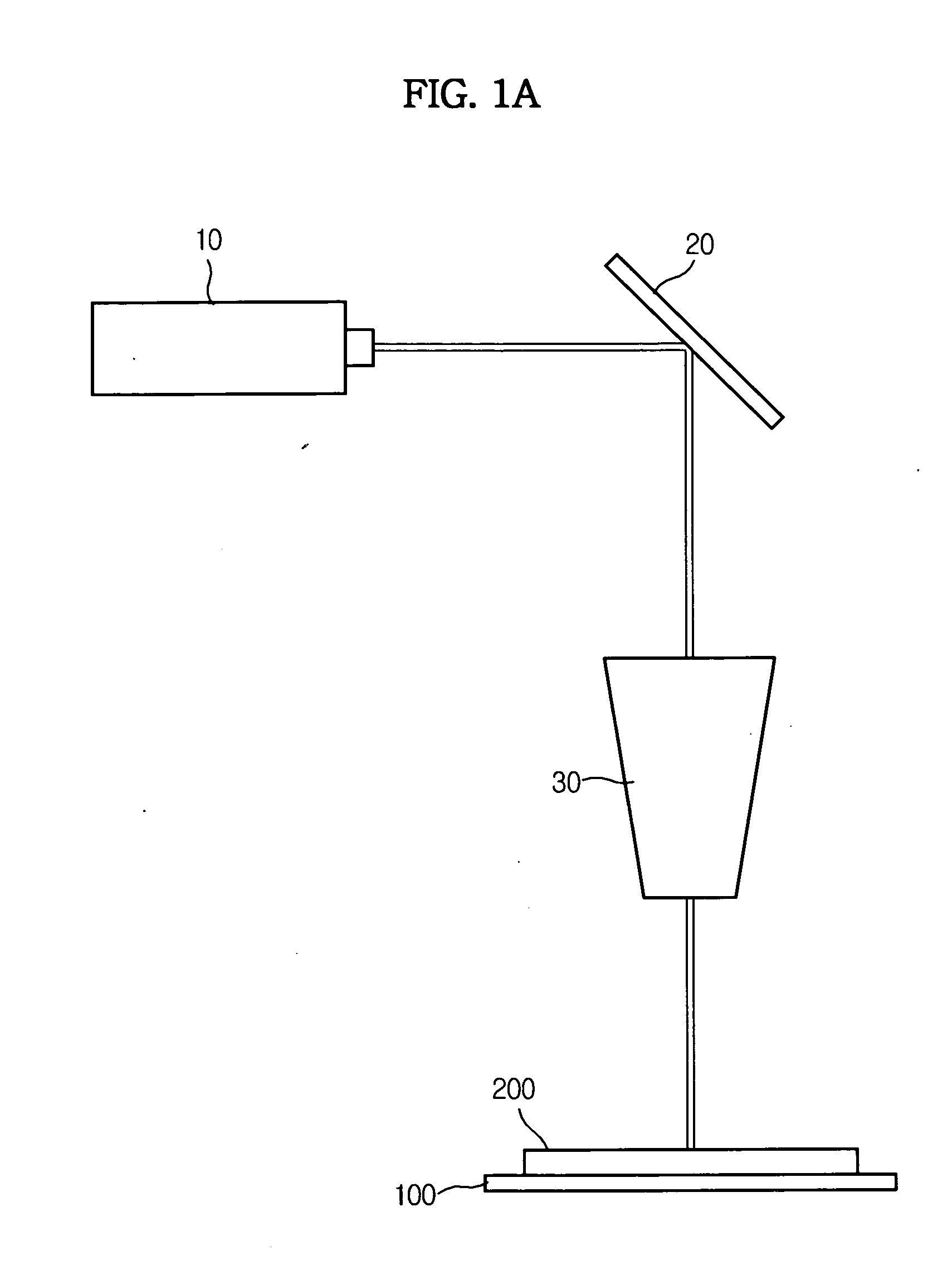

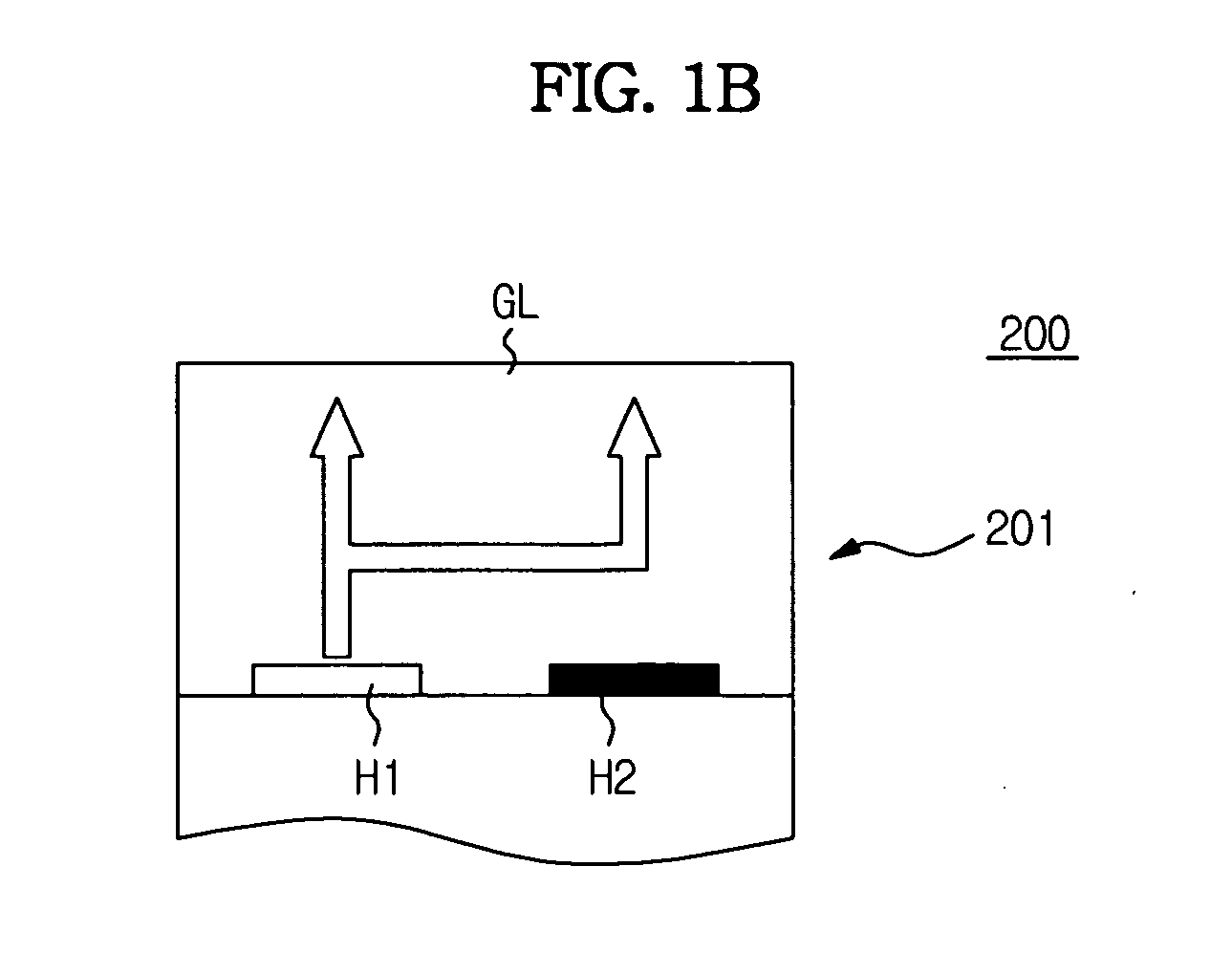

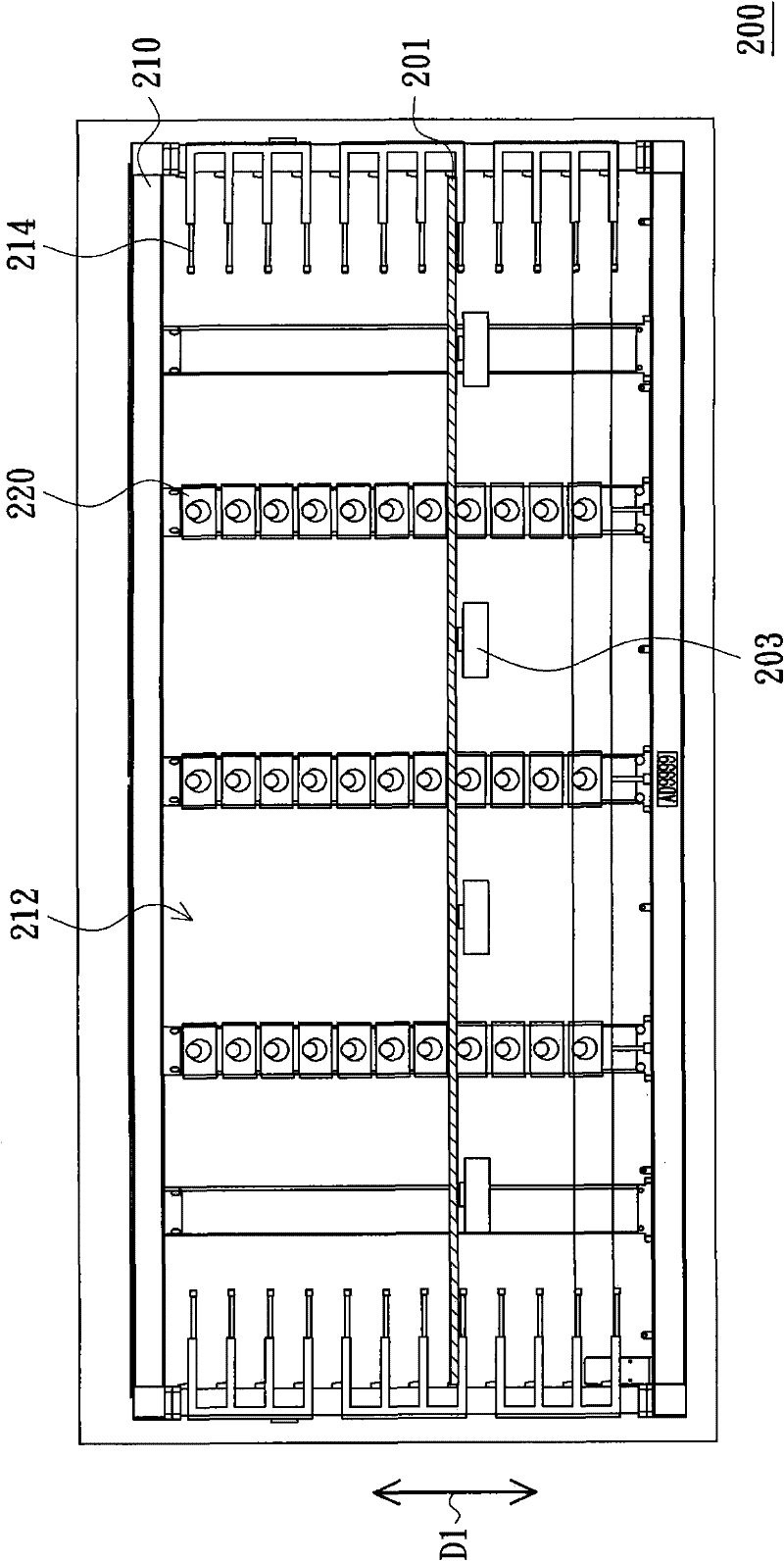

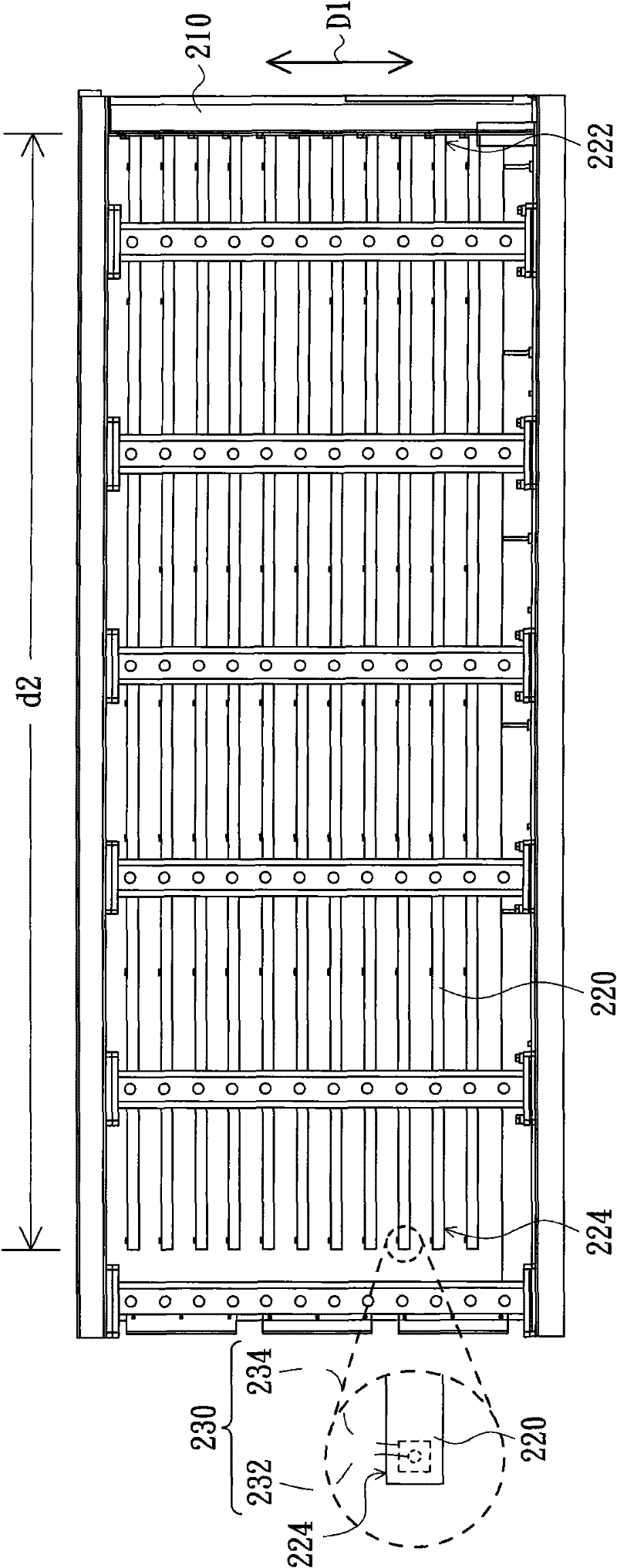

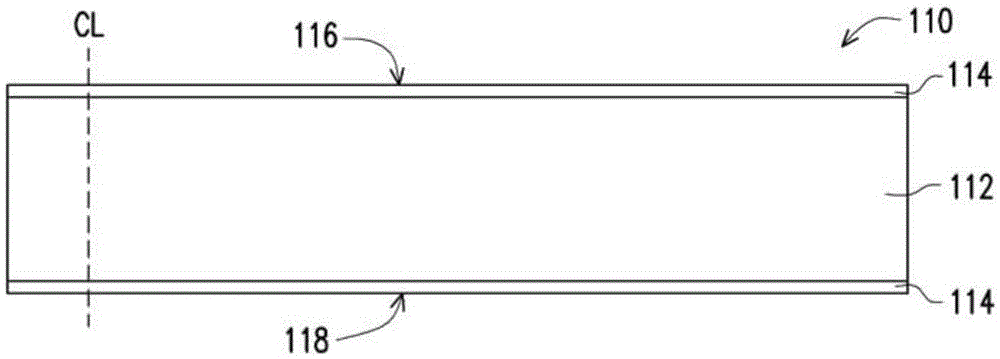

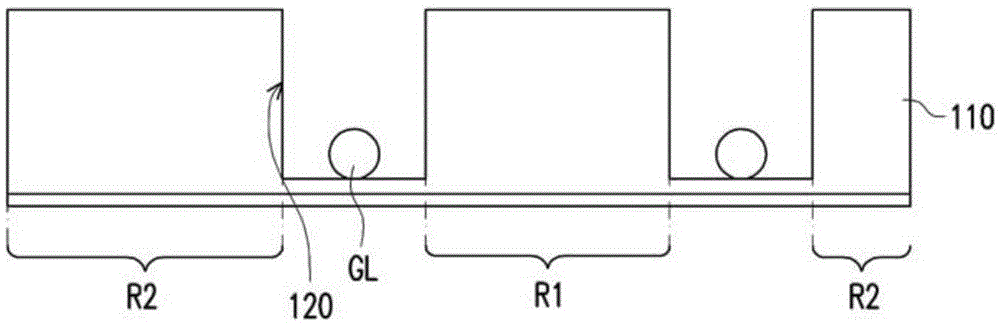

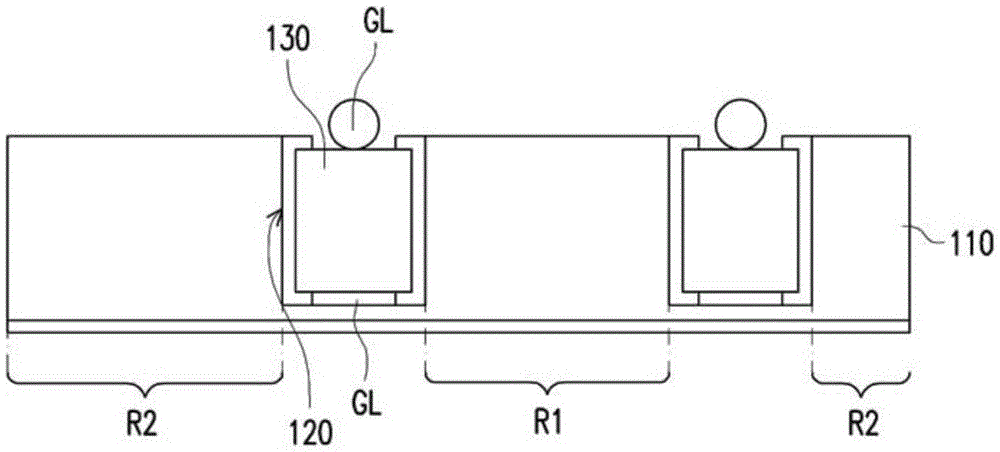

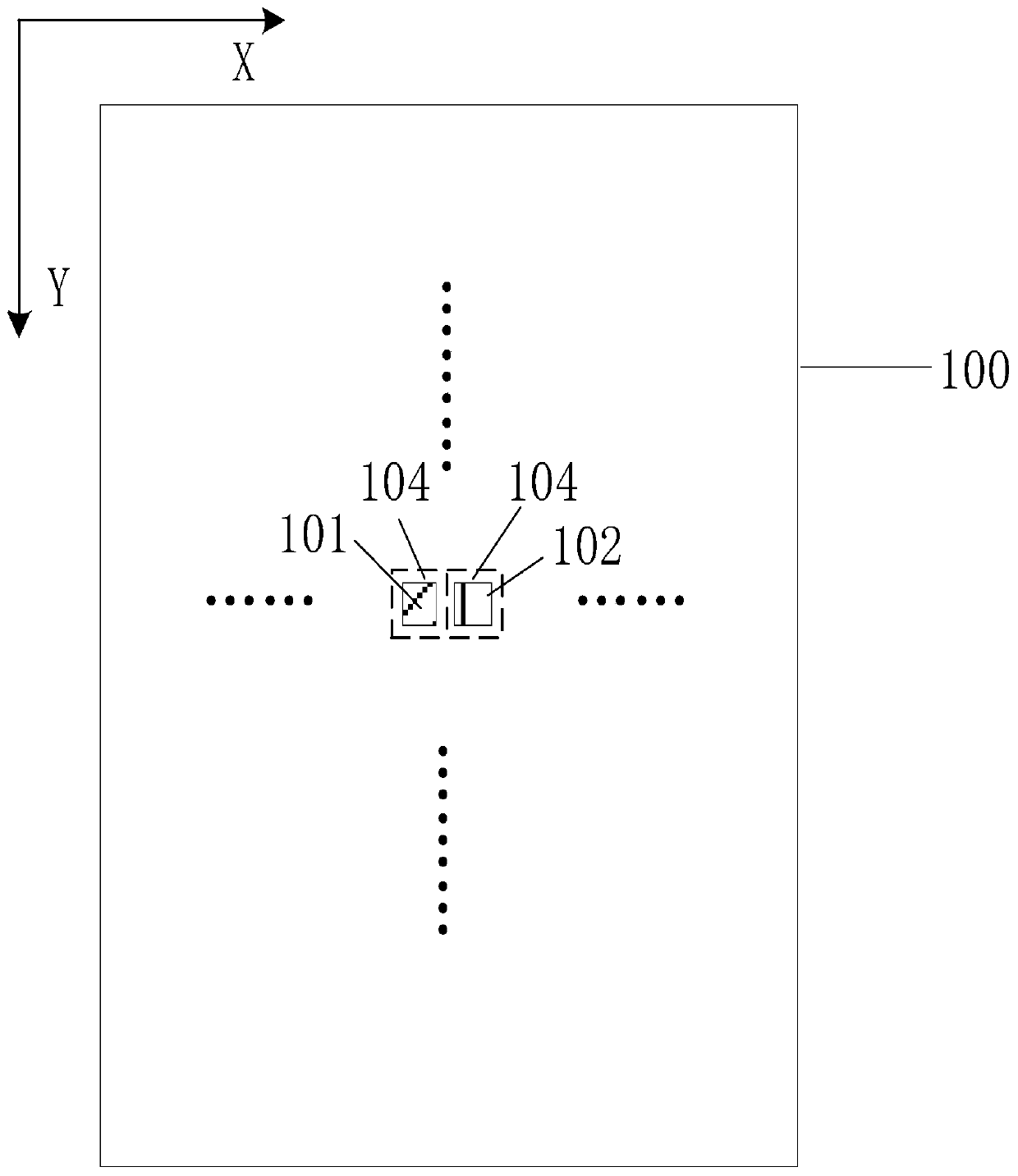

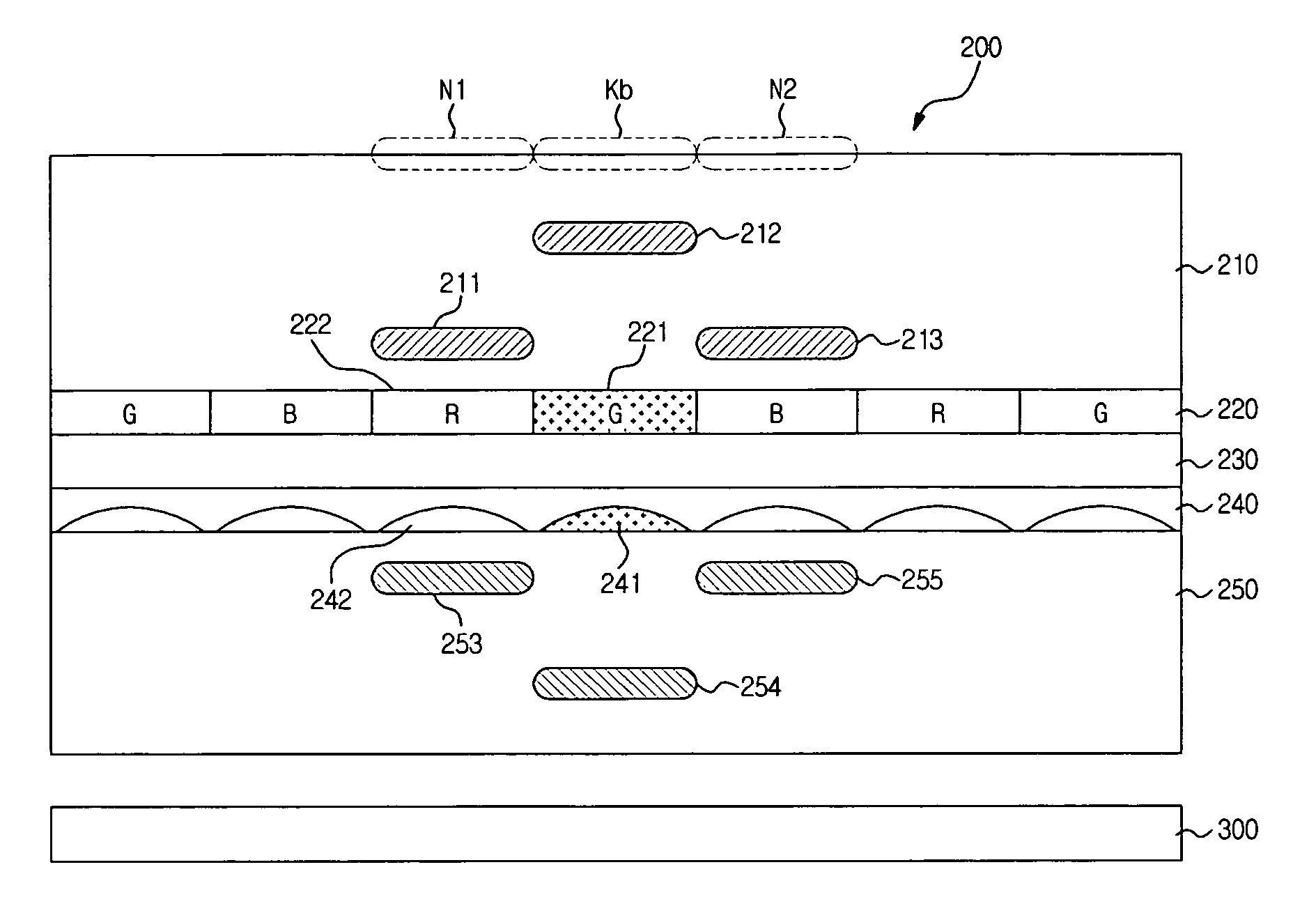

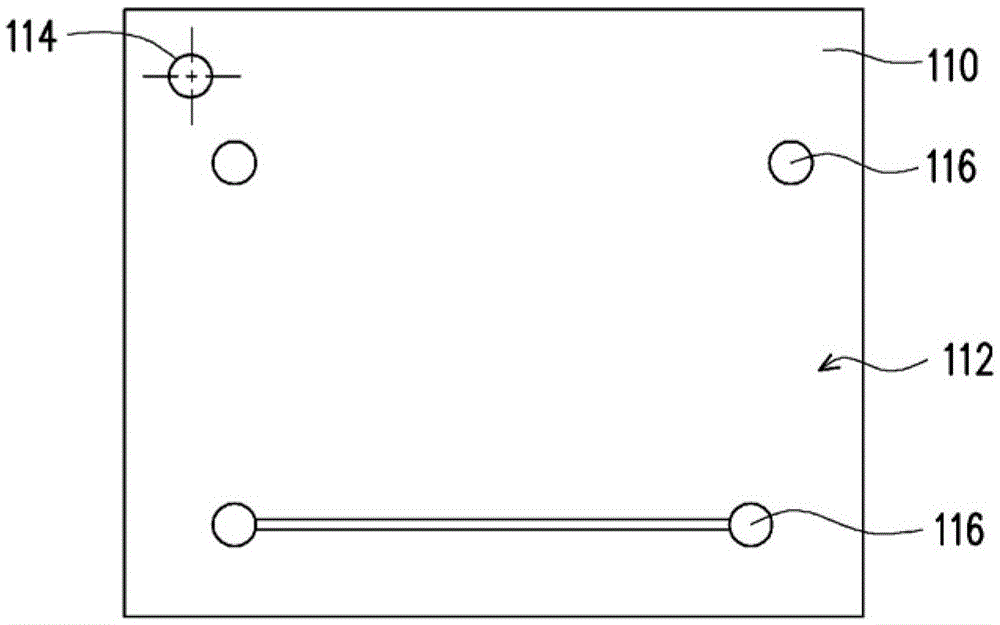

Flat display panels, methods and apparatuses to repair the same

ActiveUS20100253877A1Suppress light leakageImprove production process yieldNon-linear opticsDefective tube/lamp repair/regenerationOptoelectronicsLaser beams

When a defective pixel causing light leakage is detected in a flat display panel, an optical modulation region is formed in a substrate by emitting a laser beam such that a virtual image is displayed at a position corresponding to the defective pixel. Accordingly, quality of the flat display panel may be improved thereby increasing manufacturing process yield.

Owner:SAMSUNG ELECTRONICS CO LTD

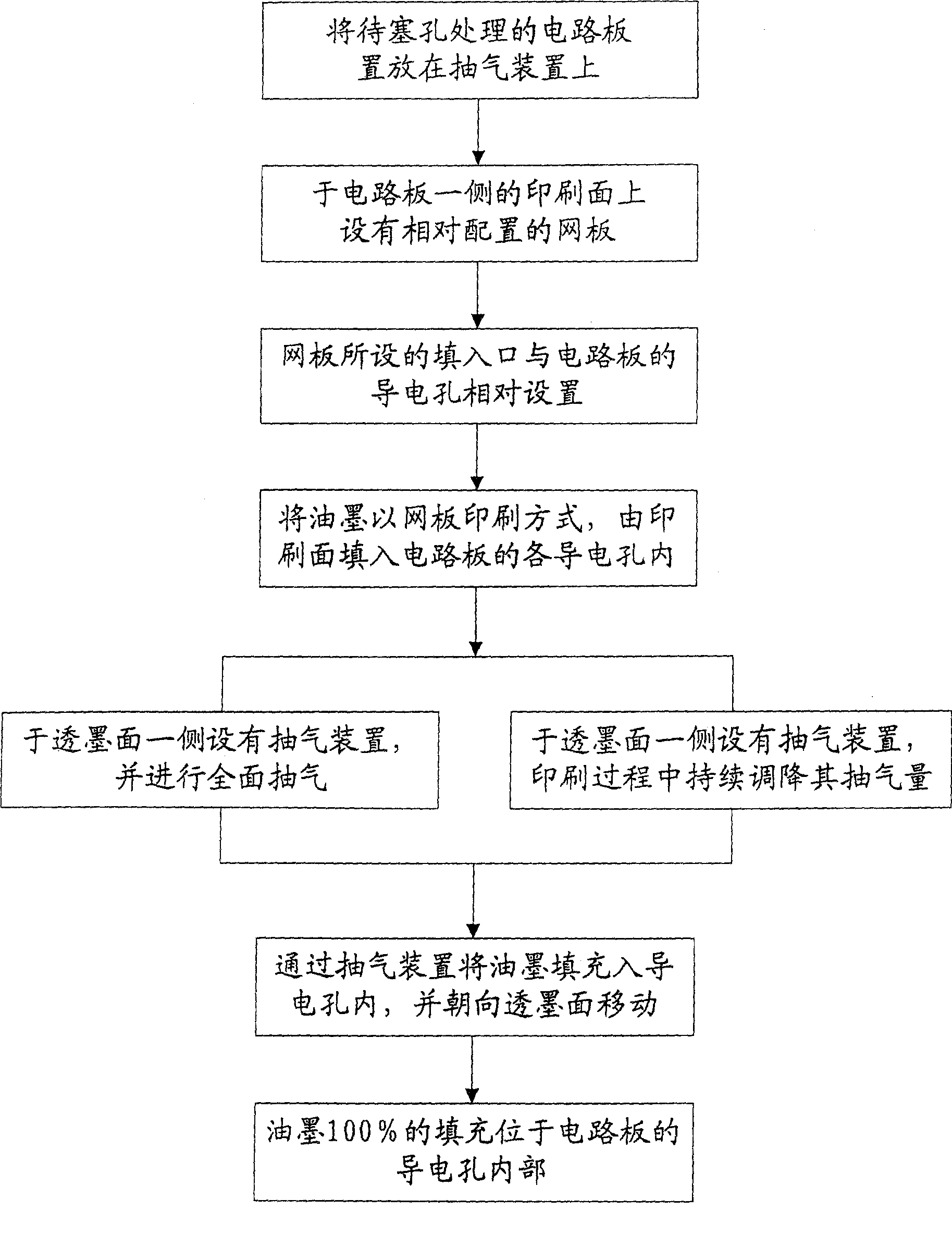

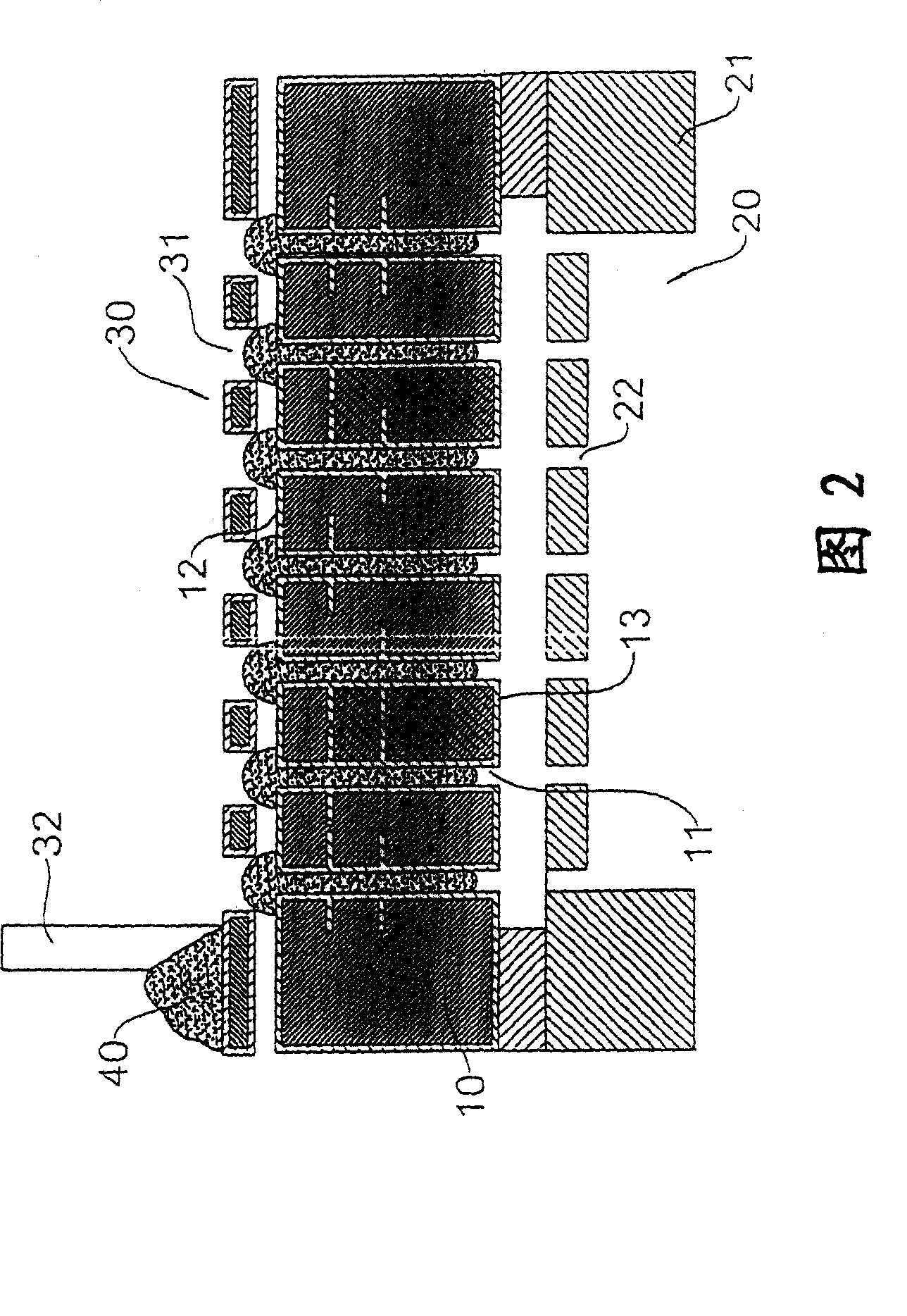

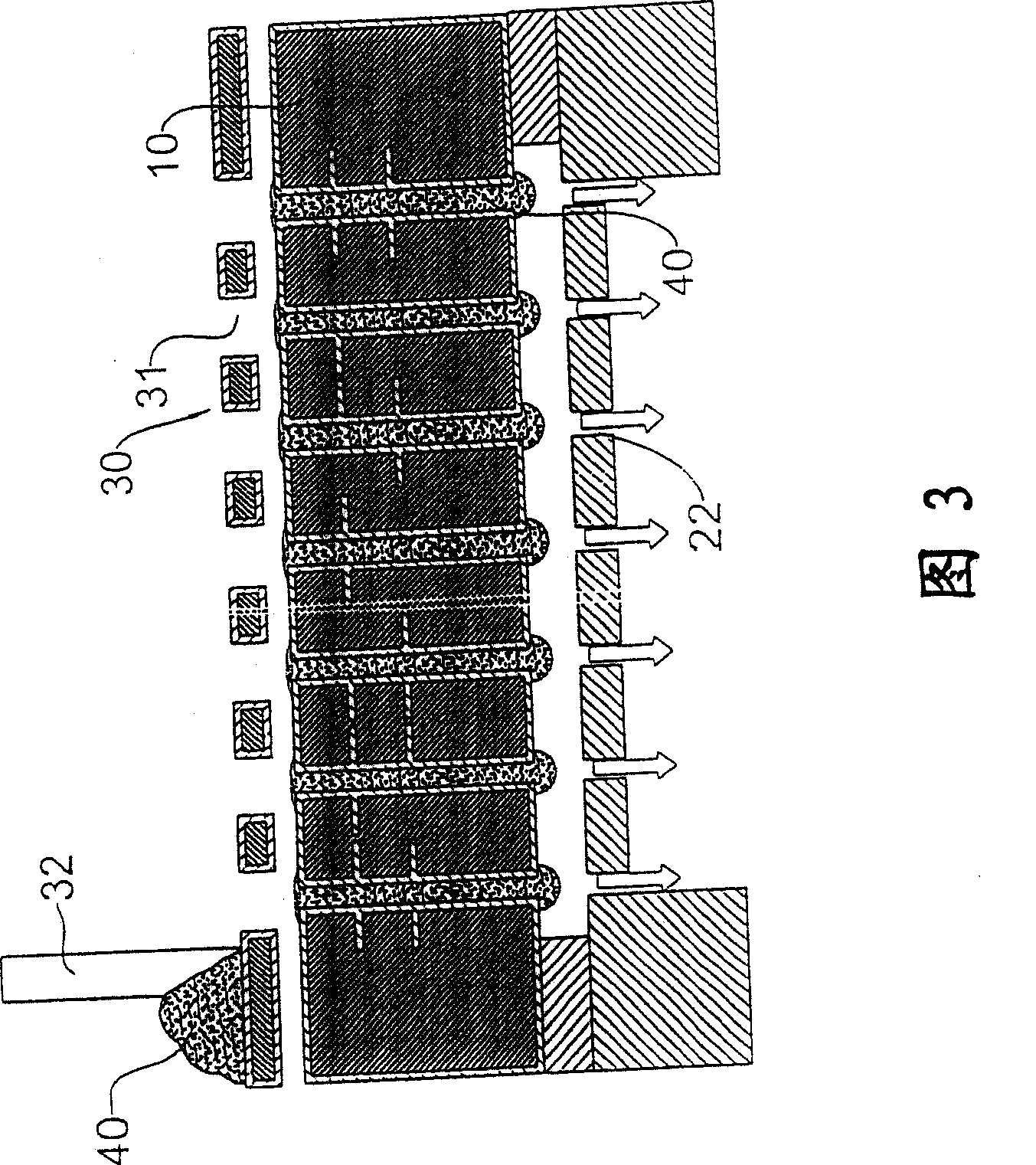

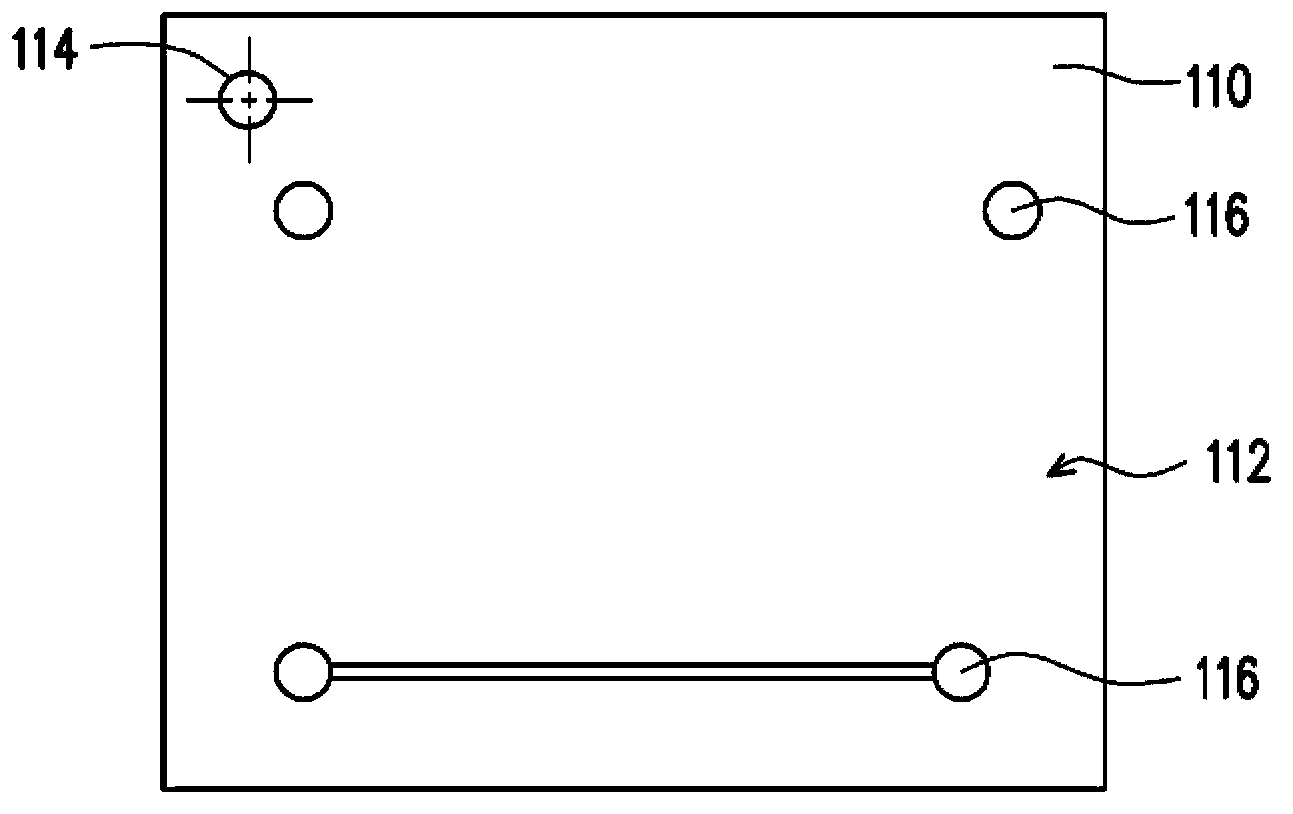

Circuit board air-pumping ink-penetrating hole-filling method and device thereof

InactiveCN100493303CReduce sag varianceImprove production process yieldMultilayer circuit manufactureAir pumpWidth ratio

The invention discloses an air exhaustion ink penetration plug method of circuit board, and a relative device, wherein the upper and lower sides of a circuit board are respectively provided with a network plate and an air absorber, the network plate is provided with a stuff inlet relative to a conductive hole of the circuit board, and the invention uses network plate print method to stuff ink into the conductive hole, and engaged with the exhaustion of an exhauster to fill ink completely into the conductive hole, therefore, the conductive hole with high length / width ratio can avoid foam, concave or break, to improve quality.

Owner:COMPEQ MFG

Multilayered circuit board structure with buried element and manufacturing method

ActiveCN103547088AReduce manufacturing process stepsImprove alignment accuracyPrinted circuit assemblingMultilayer circuit manufactureEngineeringDielectric layer

The invention discloses a multilayered circuit board structure with a buried element and a manufacturing method. The manufacturing method comprises the following steps of providing a substrate with a first surface and first contraposition marks; arranging semiconductor elements on the substrate; forming a dielectric layer, which covers the semiconductor element, is provided with a second surface and has second contraposition marks, on the substrate; enabling the second contraposition marks to correspond to the semiconductor elements; forming a first through hole group which comprises a plurality of through holes extending to the first surface from the second surface and a second through hole group which comprises a plurality of second through holes extending to the semiconductor elements from the second surface by using the first contraposition marks and the second contraposition marks as contraposition references; forming a wire group on the second surface; and patterning the wire group in two stages so as to respectively obtain a first wire group and a second wire group which are connected with each other.

Owner:TRIPOD WUXI ELECTRONICS

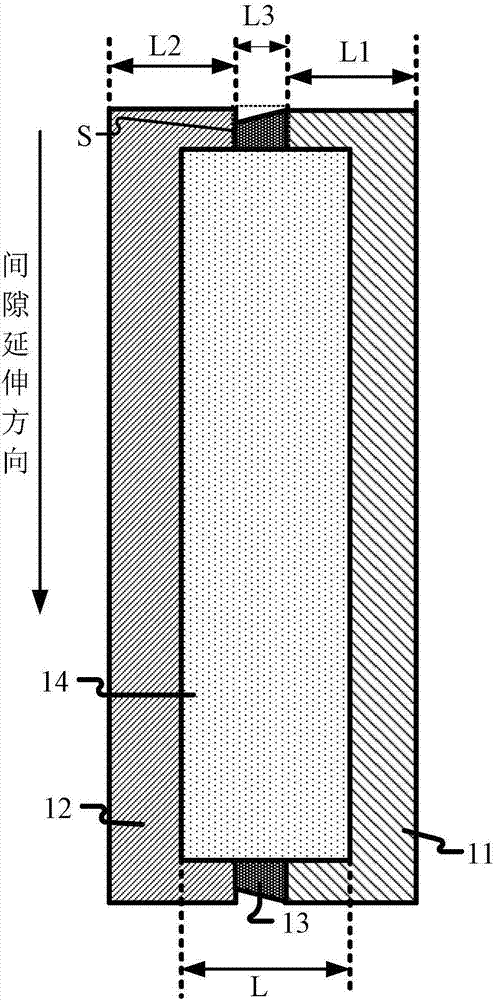

Liquid crystal display panel and making method thereof

The application discloses a liquid crystal display panel and a making method thereof. The liquid crystal display panel comprises a display area and a packaging area arranged around the display area; the liquid crystal display panel also comprises an array substrate, a color film substrate arranged opposite to the array substrate, and first encapsulation adhesive and second encapsulation adhesive which are respectively used for fixing the array substrate and the color film substrate, wherein the first encapsulation adhesive is positioned in the packaging area; the liquid crystal display panel comprises a plurality of side faces, and the second encapsulation adhesive is arranged on the at least one side face of the liquid crystal display panel; in the side faces provided with the second encapsulation adhesive, the second encapsulation adhesive covers the side faces of part of the array substrate, the side faces of part of the color film substrate and a gap between part of the array substrate and part of the color film substrate. After the scheme provided by the embodiments of the application is adopted, the probability of liquid crystal leakage is reduced, and the yield of a preparation technology of narrow-bezel liquid crystal display panels is increased.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

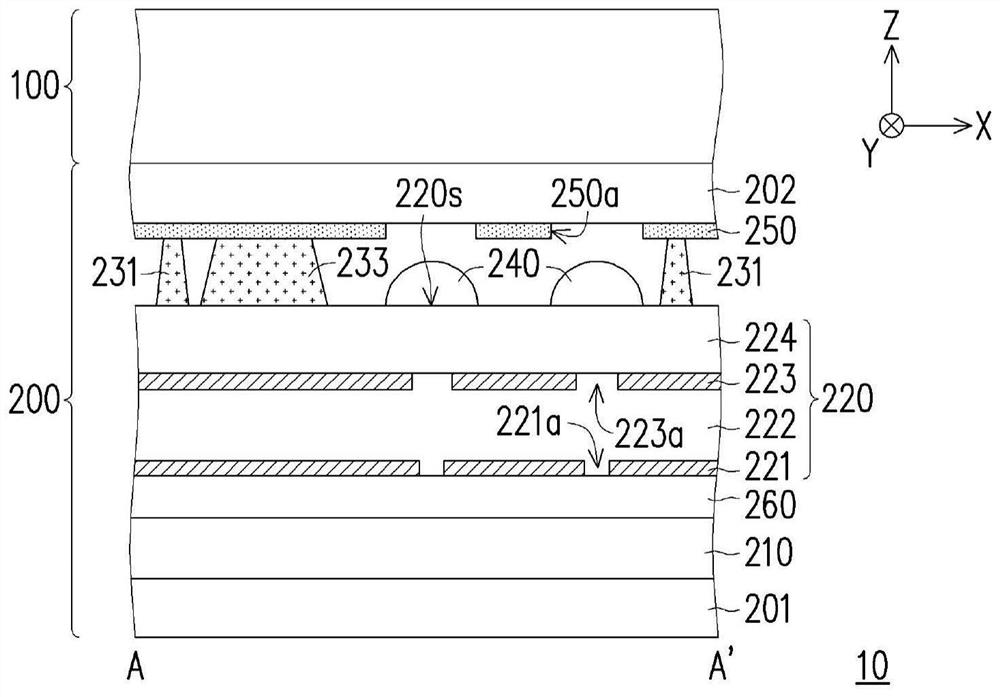

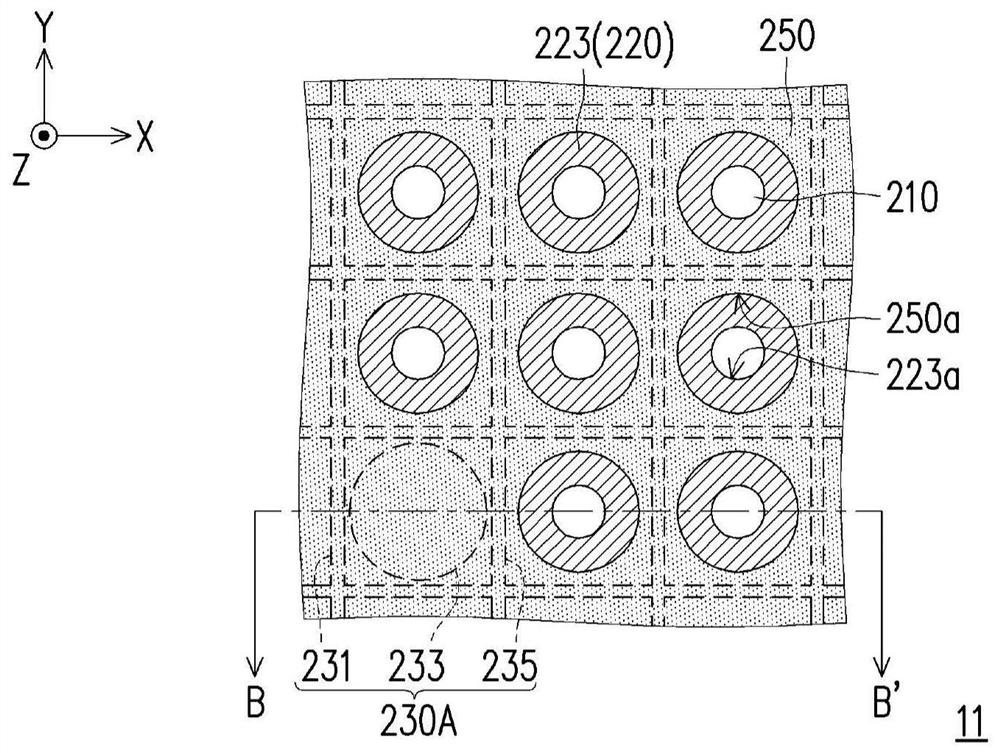

Light-emitting device

PendingCN113394321AAvoid electrical abnormalitiesImprove cooling efficiencySolid-state devicesSemiconductor devicesEngineeringLight emitting device

Owner:陈冠宇 +2

Chip package

InactiveCN102509761AReduce the diffuse effectImprove production process yieldSolid-state devicesSemiconductor devicesEngineeringLead frame

The invention discloses a chip package, which comprises a pre-molded lead frame, a chip, a plurality of leads, a barricade and a molding compound. A chip carrier and a plurality of pins of the pre-molded lead frame are wrapped by a pre-molding unit in an integrally forming manner, a first portion of each pin extends outside the pre-molding unit, the barricade is disposed on the pre-molded lead frame and connected with the pre-molding unit so as to form a cavity for holding the chip and the leads, the barricade and the pre-molding unit can be made of different materials, and the molding compound is filled into the cavity to cover the chip and the leads.

Owner:ADVANCED SEMICON ENG INC

Display panel and electronic equipment

ActiveCN108231845AIncrease opening ratioReduce the difficulty of manufacturing processStatic indicating devicesSolid-state devicesComputer scienceElectronic equipment

The invention provides a display panel and electronic equipment. The display panel comprises a plurality of sub-pixels and a plurality of pixel units, wherein the sub-pixels include at least one firstcolor sub-pixel and at least one second color sub-pixel; and the sub-pixels are arranged in one-to-one correspondence with the pixel units. According to the display panel provided by the invention, the difficulty of a preparation process is greatly reduced when a high aperture opening ratio is guaranteed, so that the yield of the preparation process of the display panel is increased, the preparation cost of the display panel is remarkably lowered, the display performance of the display panel can be greatly improved, and the comfortable user experience is provided.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

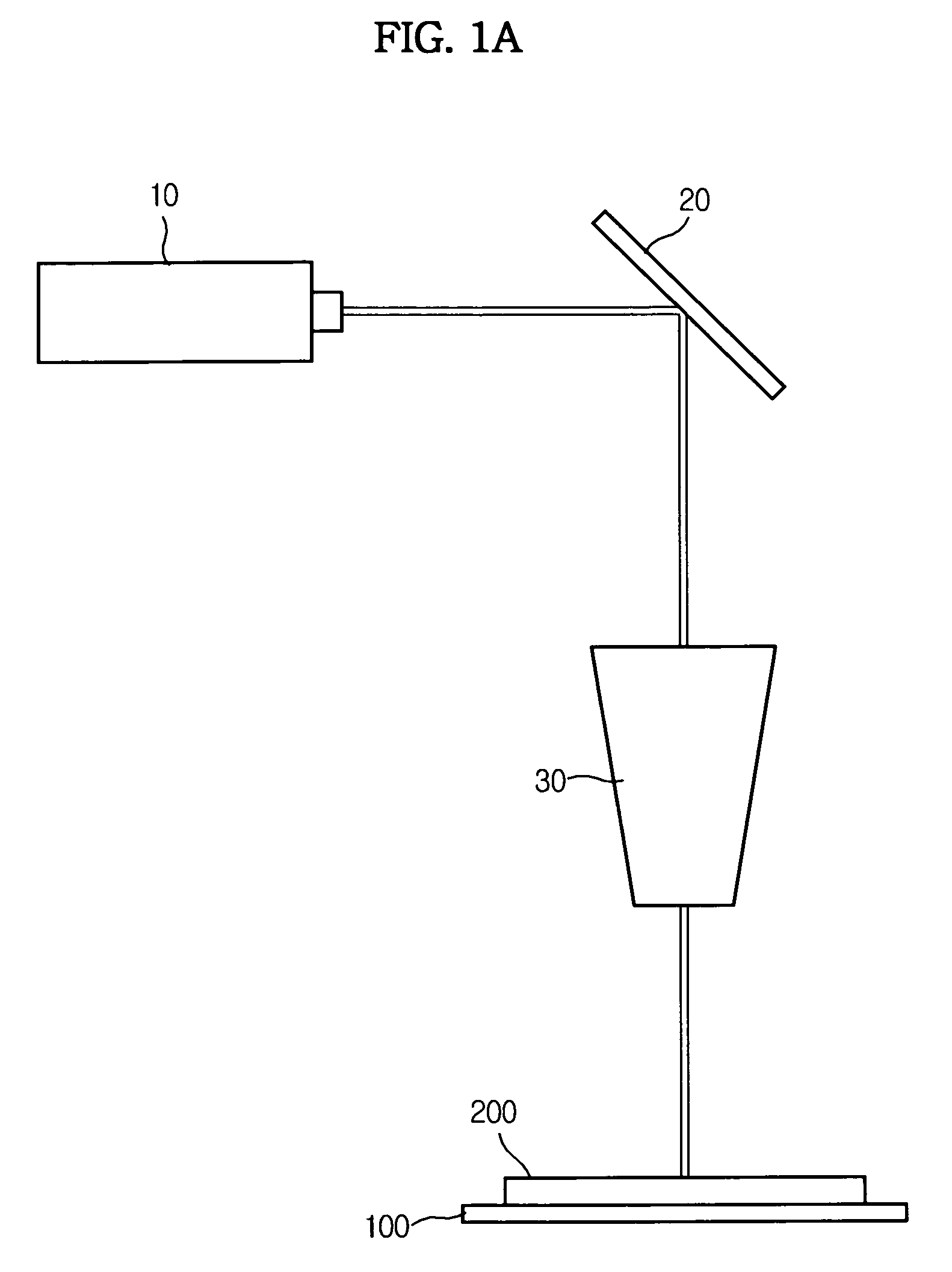

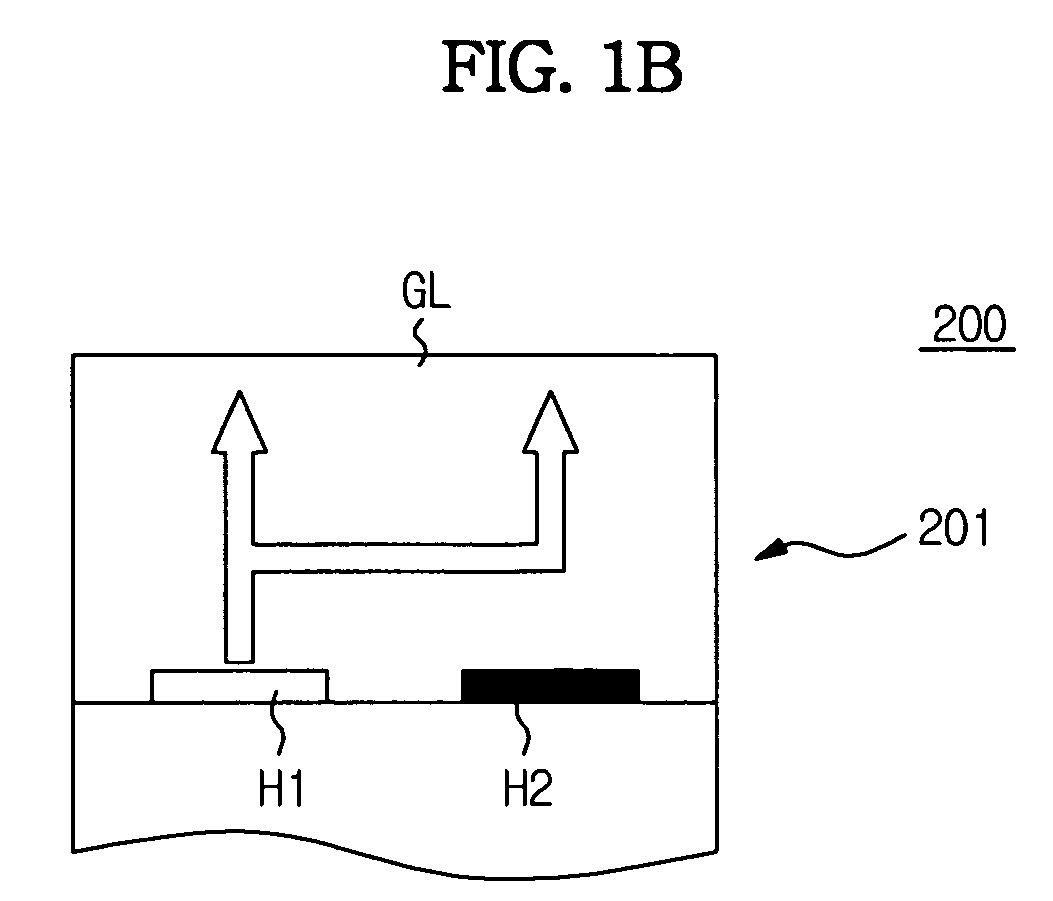

Fluid jet device and method for controlling jet quality of fluid jet device

InactiveCN1769049AAccurate control of thicknessImprove production process yieldLiquid surface applicatorsCoatingsEngineeringComparator

The invention provides a liquid ejecting device and a method for controlling the ejecting quality. The inventive device comprises a liquid chamber with the first layer to contain the liquid; at least one foam generator arranged on the first layer and opposite to the liquid chamber; a sensor to measure the thickness of first layer; second layer formed on the first layer to cover foam generator and sensor; a ejecting hole near the foam generator and through the second, first layers and liquid chamber. The invention compares the thickness of structural layer measured by sensor with the inside data base via a comparer, to support optimizated liquid ejecting driving conditions and improve the ejecting quality.

Owner:BENQ CORP

A clean production process of m-ureidoaniline hydrochloride

ActiveCN103539705BEmission reductionAvoid reactionUrea derivatives preparationOrganic compound preparationReaction temperatureSodium cyanate

The invention discloses a clean production process of m-carbamidoaniline hydrochloride. The clean production process comprises the following steps of: dissolving m-phenylenediamine into a sodium chloride salt water reaction system; adding an auxiliary agent into the reaction system; controlling a reaction temperature at -5 DEG C to 25 DEG C; then adding sodium cyanate and hydrochloric acid for reaction; and after the reaction is completed, carrying out post-treatment on a resulting substance to obtain m-carbamidoaniline hydrochloride, wherein the auxiliary agent is nitric acid or nitrate. According to the clean production process, salt water, instead of pure water, is used as base water, m-carbamidoaniline hydrochloride produced in the reaction can be separated out in time by using salt precipitation effects of sodium chloride, a byproduct diurea is not generated, the purity of the obtained m-carbamidoaniline hydrochloride is more than 98%, the yield is more than 95%, the content is 75%-80%, the sewage quantity is reduced by 50%, and the process is simple and high in automation degree.

Owner:ZHEJIANG RUNTU INST

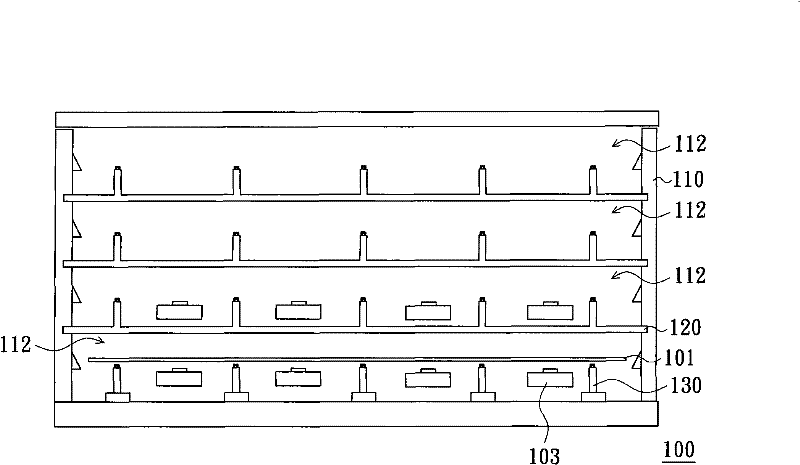

Substrate storing box

InactiveCN101913465BImprove transportation efficiencyReduce the chance of breakageContainers to prevent mechanical damageDamagable goods packagingEngineeringCantilever

The invention discloses a substrate storing box which comprises a frame body, a plurality of hollow cantilever supporting rods and at least one vibration absorber, wherein the hollow cantilever supporting rods are arranged in the storing space of the frame body, and each hollow cantilever supporting rod is provided with a free end and a fixed end fixed on the frame body; the hollow cantilever supporting rods respectively have a first vibration frequency in the first direction; the vibration absorber is arranged in at least one hollow cantilever supporting rod and is close to the free end of the hollow cantilever supporting rod; and the vibration absorber has a second vibration frequency in the first direction, wherein the second vibration frequency is different from the first vibration frequency.

Owner:AU OPTRONICS CORP

Circuit board packaging structure and manufacturing method thereof

ActiveCN106793555AImprove electrical performanceImprove production process yieldPrinted circuit assemblingElectrical and Electronics engineeringInternal zone

The present invention discloses a circuit board packaging structure and a manufacturing method thereof. The circuit board packaging structure comprises a substrate, an annular magnetic element, a first stack-up layer, a plurality of external conduction columns, a plurality of internal conduction columns, a plurality of second stack-up layers and a plurality of conductive slots. The substrate comprises an annular groove, and a first surface and a second surface which are opposite with each other. The annular groove is arranged at the first surface. The annular magnetic element is arranged in the annular groove. The first stack-up layer is arranged on the first surface. The external conduction columns and the internal conduction columns run through the substrate and are respectively located at the external area and the internal area of the annular groove. The external conduction columns are electrically connected with the corresponding internal conduction columns. The second stack-up layers are respectively arranged on the first stack-up layers and the second surface. The conductive slots are arranged at the periphery of the substrate. The conductive slots run through the substrate, the first stack-up layer and the second stack-up layer.

Owner:TRIPOD WUXI ELECTRONICS

Fingerprint sensing module

PendingCN113792571AIncreased force toleranceIncrease manufacturing process marginSolid-state devicesPrint image acquisitionEngineeringMaterials science

Owner:AU OPTRONICS CORP

A display panel, an electronic device

ActiveCN108231845BIncrease opening ratioReduce the difficulty of manufacturing processStatic indicating devicesSolid-state devicesEngineeringComputer science

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD +1

Flat display panels, methods and apparatuses to repair the same

ActiveUS8384844B2Suppress light leakageImprove production process yieldNon-linear opticsDefective tube/lamp repair/regenerationOptoelectronicsLaser beams

When a defective pixel causing light leakage is detected in a flat display panel, an optical modulation region is formed in a substrate by emitting a laser beam such that a virtual image is displayed at a position corresponding to the defective pixel. Accordingly, quality of the flat display panel may be improved thereby increasing manufacturing process yield.

Owner:SAMSUNG ELECTRONICS CO LTD

Electrophoretic display and manufacturing method thereof

ActiveCN102109727BExtended service lifeImprove production process yieldNon-linear opticsActive componentFlexible circuits

The invention relates to an electrophoretic display and a manufacturing method thereof. The electrophoretic display comprises a first base plate, an active component array, a driving circuit, a flexible printed circuit, an electrophoretic display layer, a second base plate and a driving chip. The first base plate is provided with a first surface which is provided with a display region and a line region. The active component array is arranged in the display region, the driving circuit is arranged in the line region and is electrically connected to the active component array, and an electric conduction flexible circuit is partially arranged on the first base plate and is electrically connected to the driving circuit. The electrophoretic display layer and the second base plate are arranged on the active component array and the driving circuit sequentially, and the sealing compound is adhered between the second base plate and the electric conduction flexible circuit to tightly seal the electrophoretic display layer between the first base plate and the second base plate. The driving chip is connected with the diving circuit, and the electrophoretic display layer comprises an opening to expose the driving chip. The invention also discloses a manufacturing method of the electrophoretic display.

Owner:E INK HLDG INC

Multilayer circuit board structure with embedded components and manufacturing method

ActiveCN103547088BReduce manufacturing process stepsImprove alignment accuracyPrinted circuit assemblingMultilayer circuit manufactureEngineeringBoard structure

The invention discloses a multilayer circuit board structure with embedded components and a manufacturing method. The manufacturing method includes: providing a substrate having a first surface and a first alignment mark. Semiconductor components are placed on the substrate. A dielectric layer is formed on the substrate. The dielectric layer covers the semiconductor element and has a second surface and a second alignment mark. Each second alignment mark is provided corresponding to each semiconductor element. Using the first and second alignment marks as alignment references respectively, first and second via hole groups are formed. The first via hole group includes a plurality of first vias extending from the second surface to the first surface. hole. The second via hole group includes a plurality of second via holes extending from the second surface to the semiconductor element. Form wire groups on the second surface. The conductor groups are patterned in two stages to respectively form first and second conductor groups connected to each other.

Owner:TRIPOD WUXI ELECTRONICS

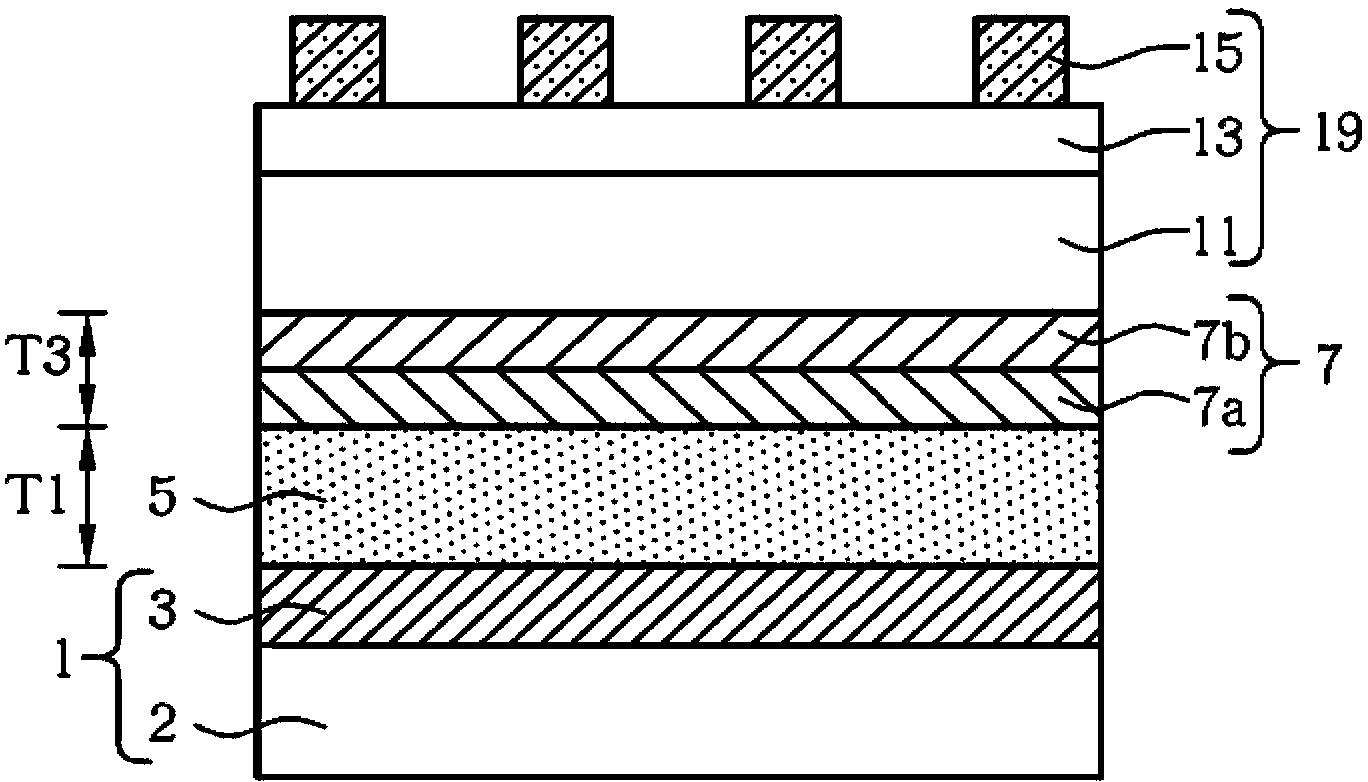

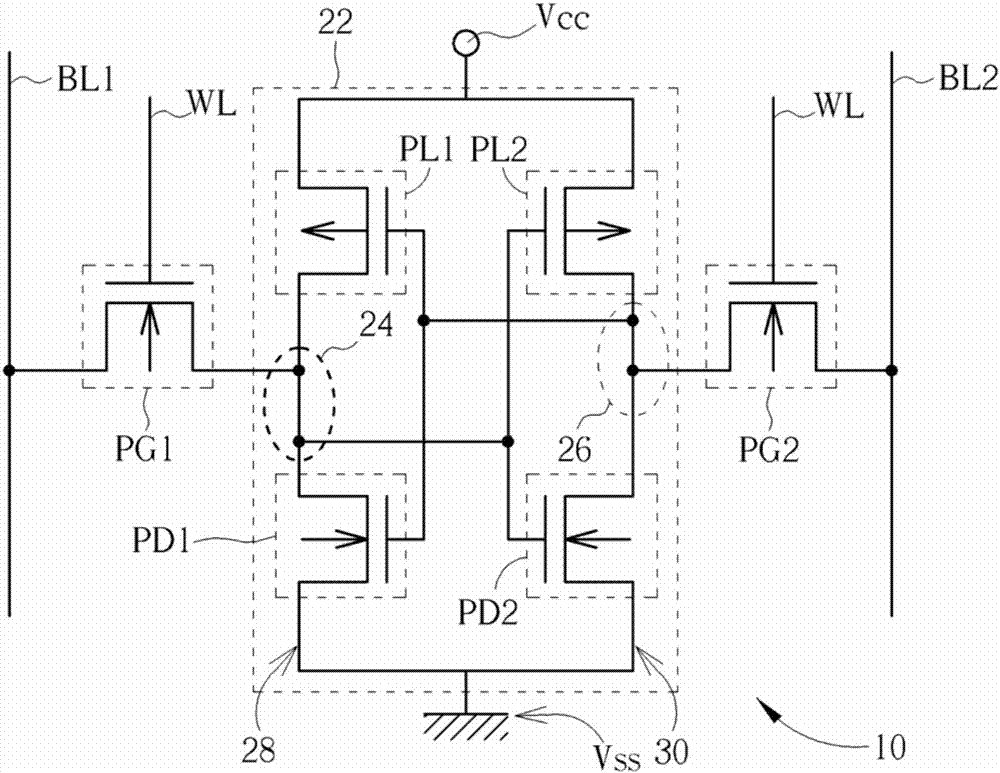

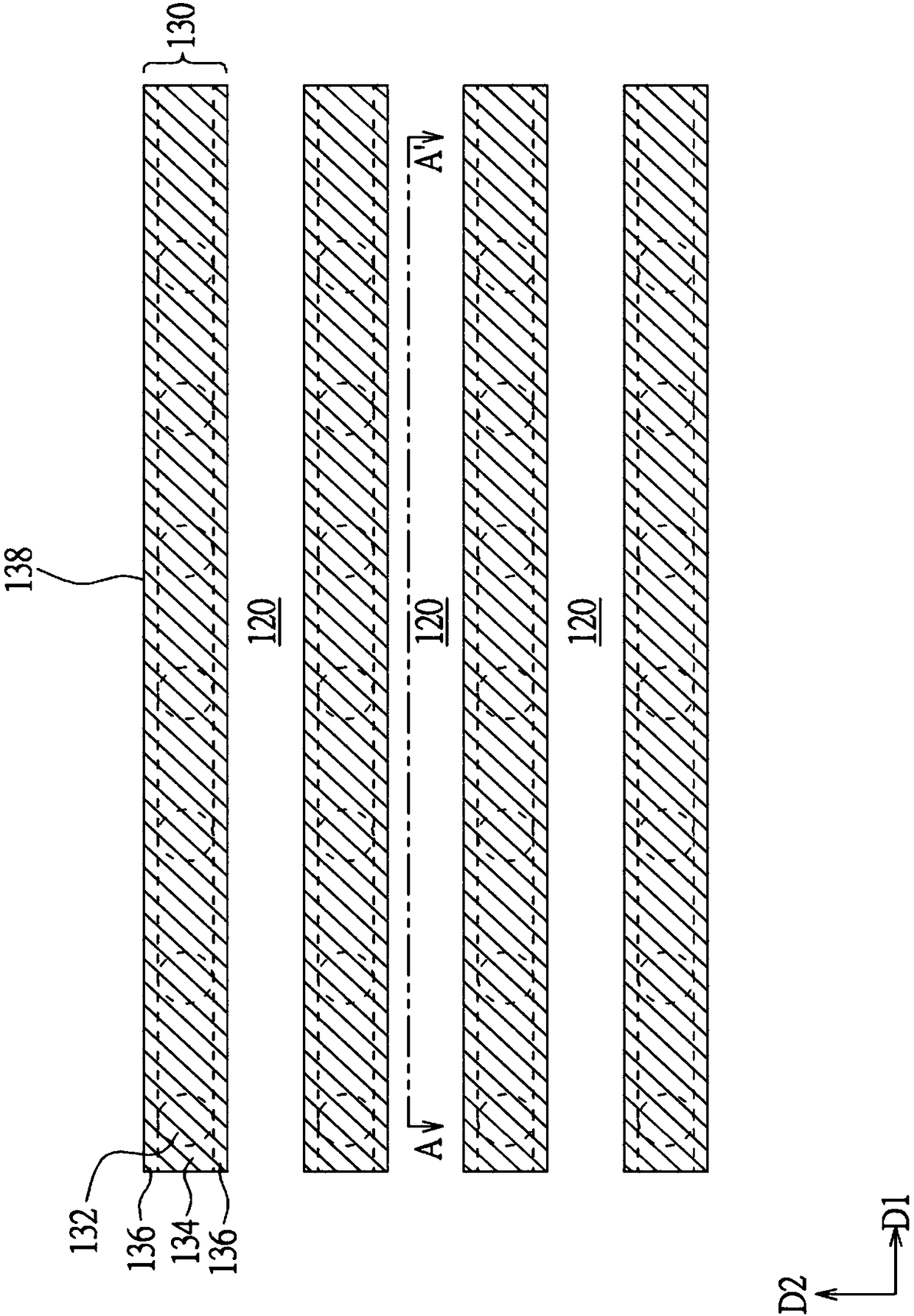

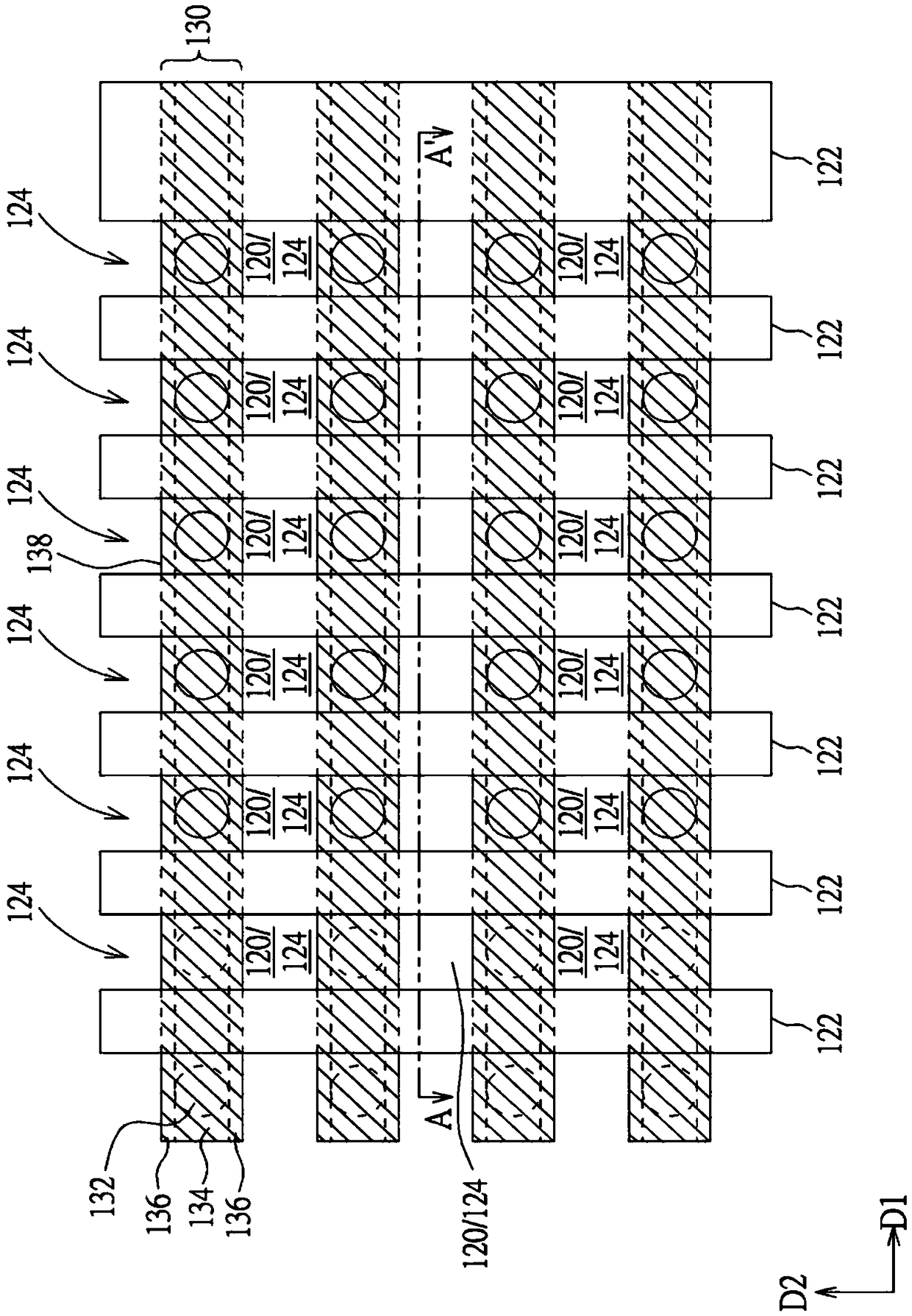

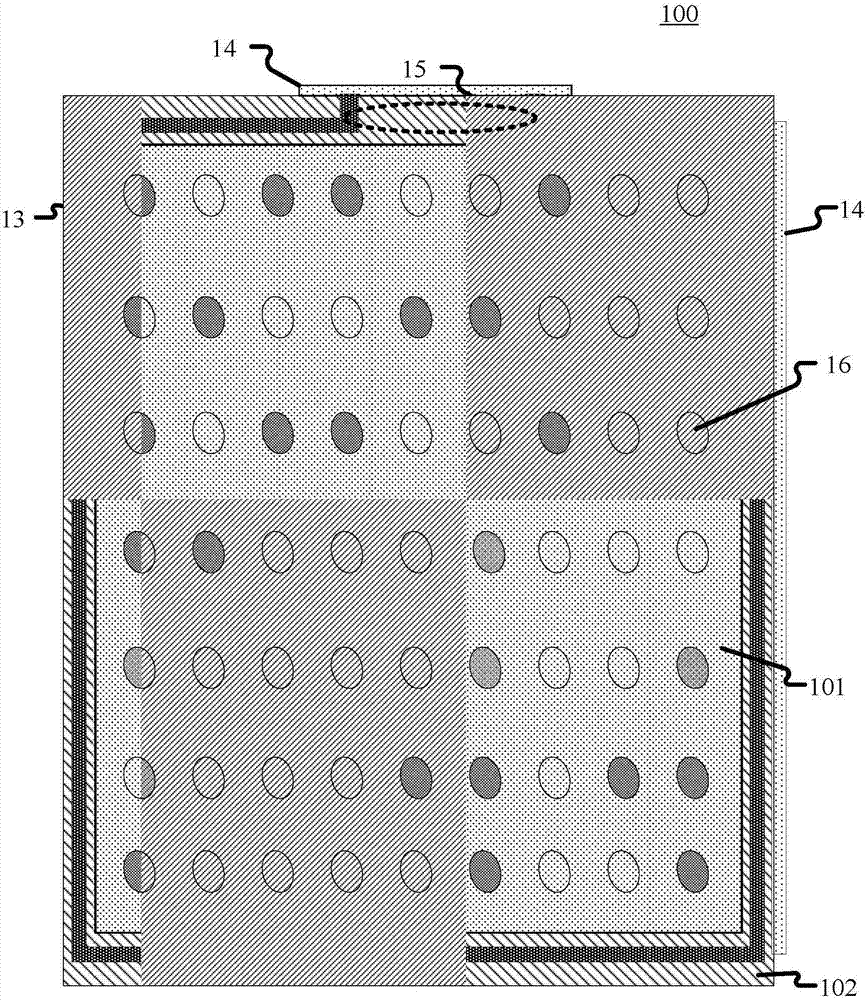

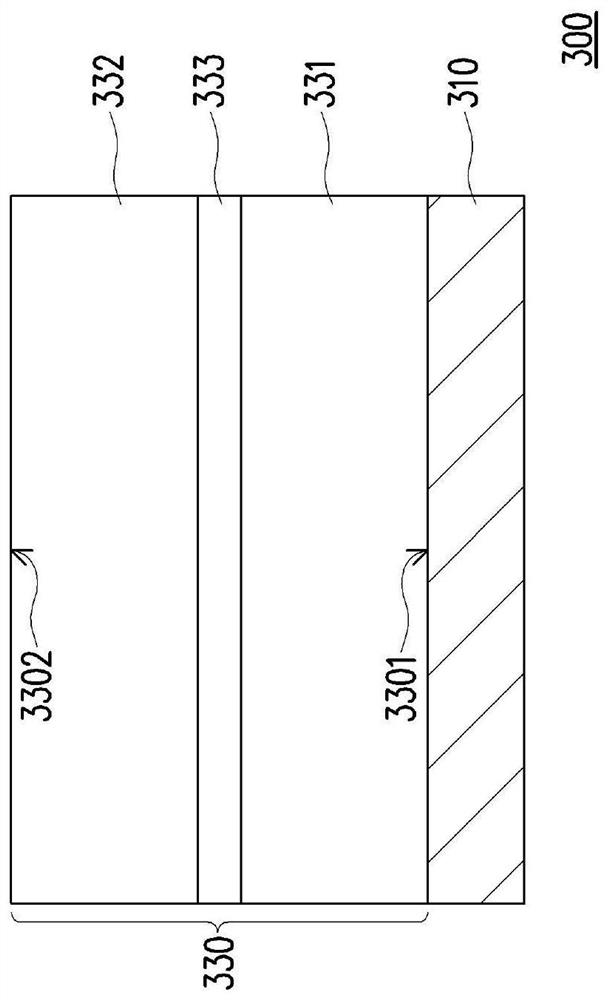

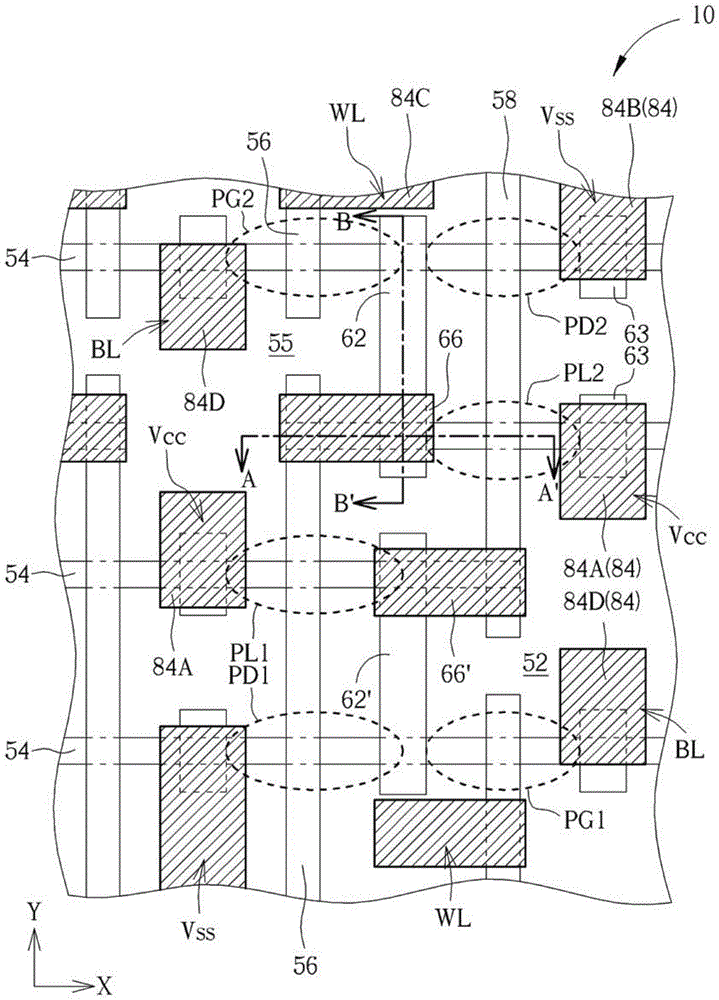

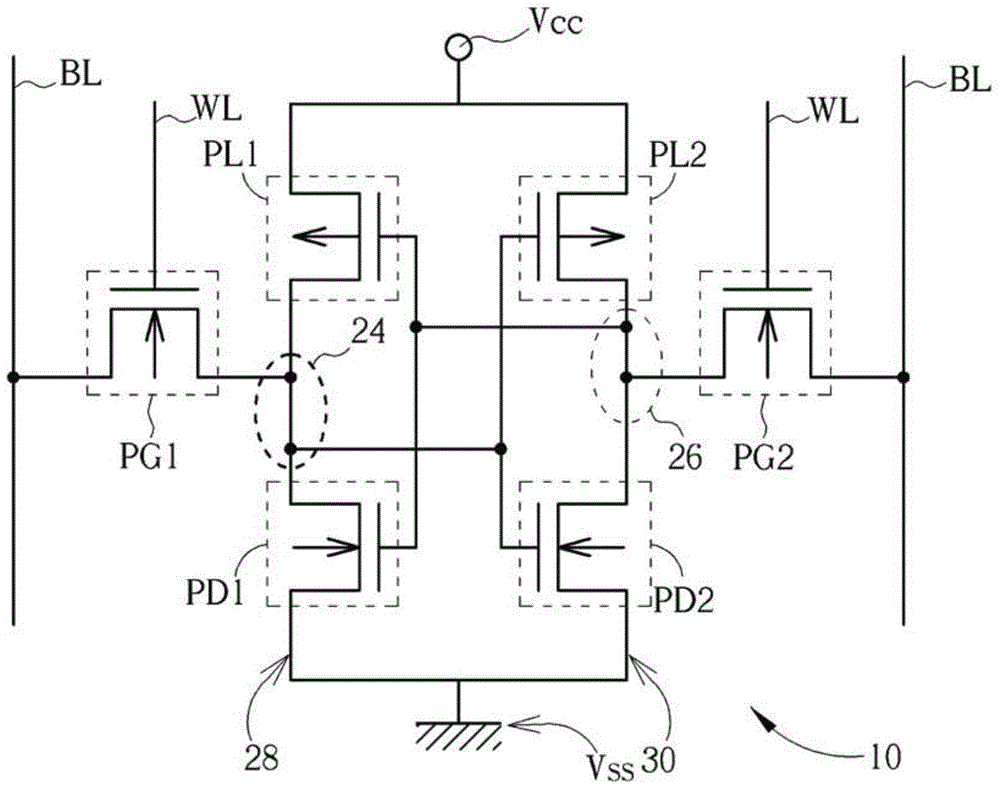

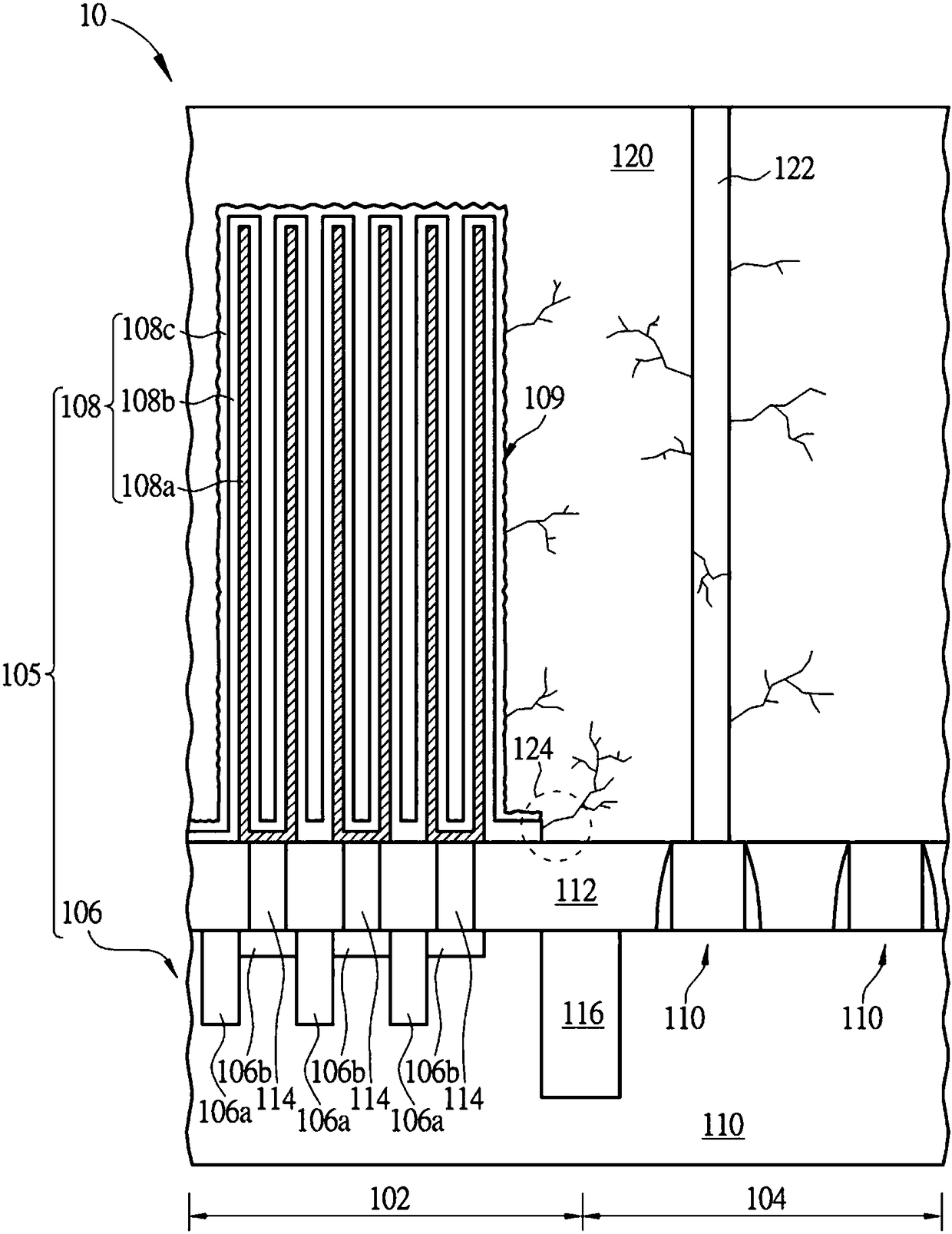

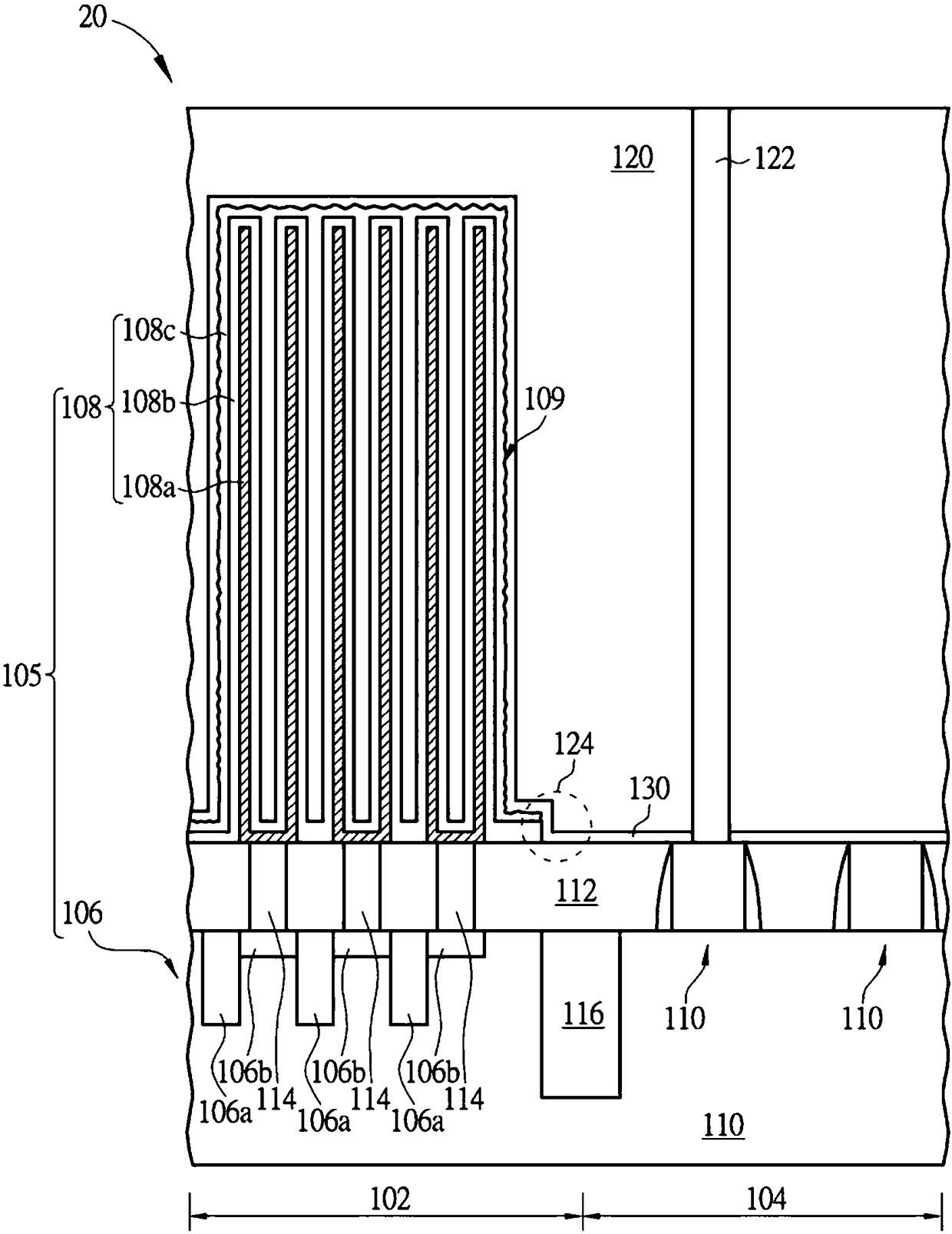

Static random access memory

ActiveCN106298782ALow densityImprove production process yieldSemiconductor/solid-state device detailsSolid-state devicesStatic random-access memoryRandom access memory

The invention discloses a static random access memory, which comprises a plurality of static random access memory units arranged on a substrate, wherein each static random access memory unit comprises at least one grid structure arranged on the substrate, a plurality of fin structures located on the substrate, a first interlayer dielectric layer surrounding the grid structure, a first contact plug arranged in the first interlayer dielectric layer, and a second interlayer dielectric layer arranged on the first interlayer dielectric layer, wherein the arrangement directions of the fin structures are vertical to those of the grid structures; and each first contact plug is in a long strip form and is in contact with two corresponding fin structures at the same time.

Owner:UNITED MICROELECTRONICS CORP

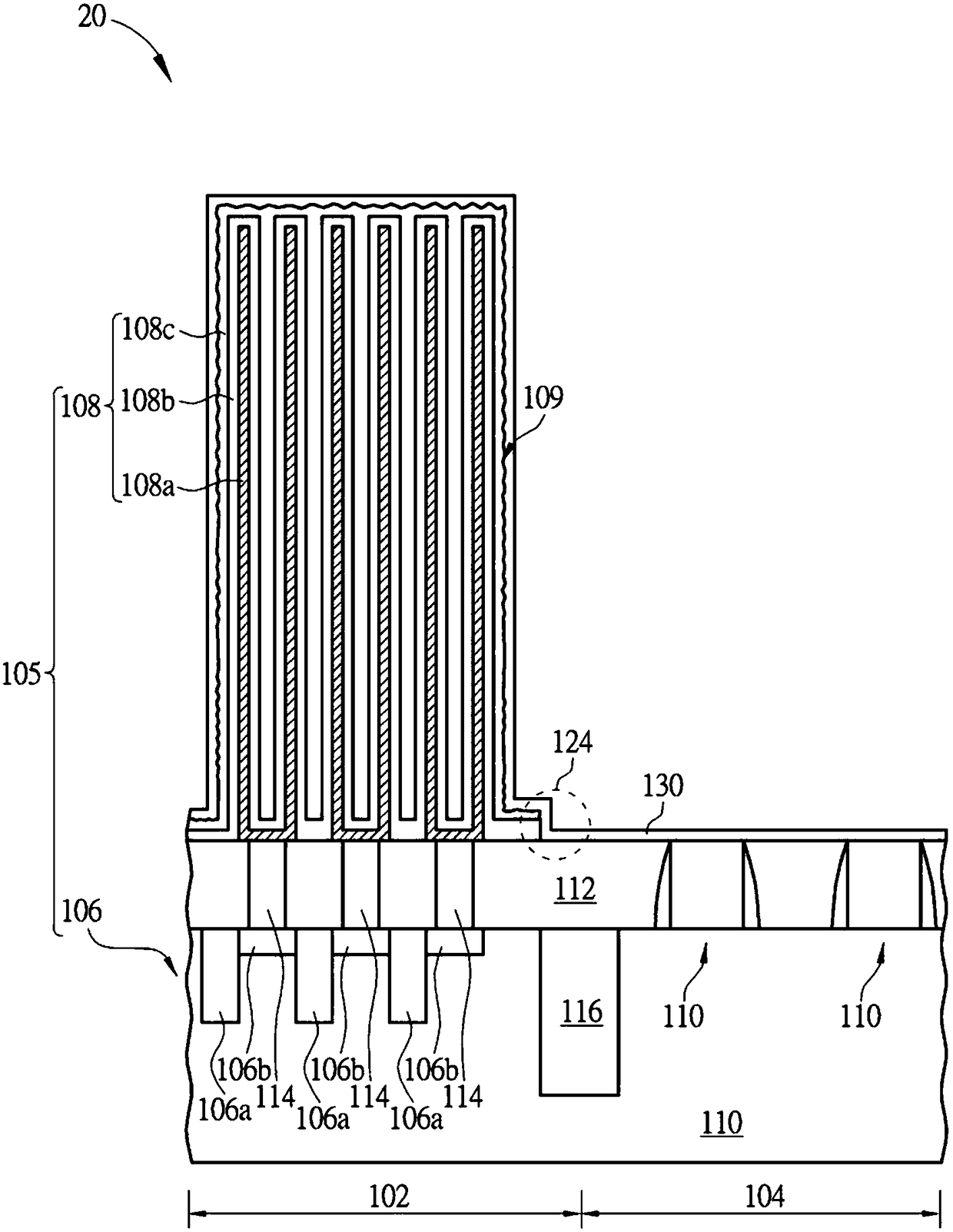

Manufacturing method of semiconductor element

ActiveCN108269807AReduce chippingOffset compressive stressTransistorSemiconductor/solid-state device manufacturingCapacitanceEngineering

The invention discloses a manufacturing method of a semiconductor element, which at least comprises the steps of firstly providing a substrate, wherein the substrate is internally defined with a storage region and a peripheral region, the storage region contains a plurality of storage units, each storage unit at least comprises a first transistor and a capacitor structure, the peripheral region contains at least one second transistor; then forming a first insulating layer in a mode of atomic layer deposition in the storage region and the peripheral region, wherein the first insulating layer atleast covers the capacitor structure of each storage unit in the storage region and the second transistor in the peripheral region; then forming a second insulating layer which covers the first insulating layer; and forming a contact structure in the second insulating layer in the peripheral region, wherein the contact structure is at least electrically connected with the second transistor.

Owner:UNITED MICROELECTRONICS CORP +1