Manufacturing method for embedded type semiconductor package piece of element

A manufacturing method and embedded technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of carrier board and multilayer circuit board deformation, increase the defect rate of non-core manufacturing process, etc., and achieve simplified manufacturing process, increasing the yield of the manufacturing process, and the effect of thin package thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

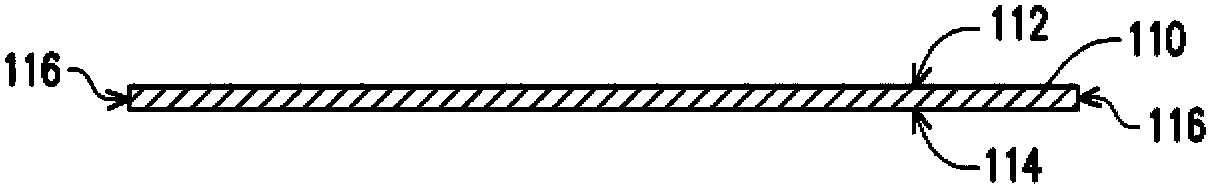

[0054] Figures 1A to 1J It is a schematic cross-sectional view of a manufacturing process of a device-embedded semiconductor package according to an embodiment of the present invention. Please refer to Figure 1A , in this embodiment, the fabrication method of the component-embedded semiconductor package includes the following steps: First, please refer to Figure 1A , a metal substrate 110 is provided. Specifically, the metal substrate 110 has a substrate upper surface 112 and a substrate lower surface 114 opposite to each other, and a substrate side surface 116 connecting the substrate upper surface 112 and the substrate lower surface 114 . In this embodiment, the material of the metal substrate 110 is, for example, aluminum or stainless steel.

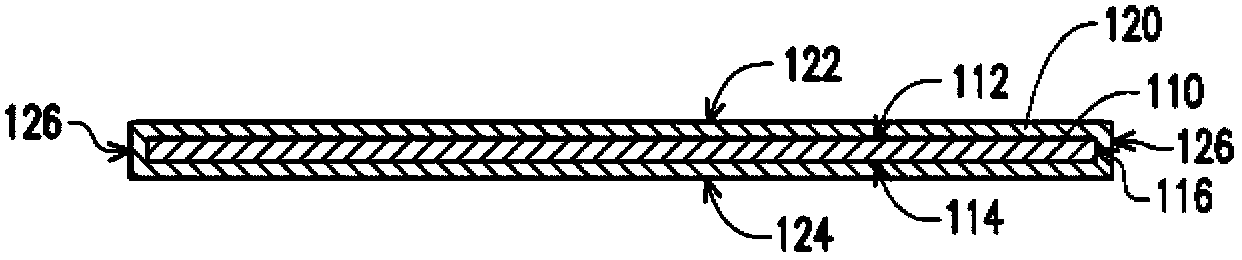

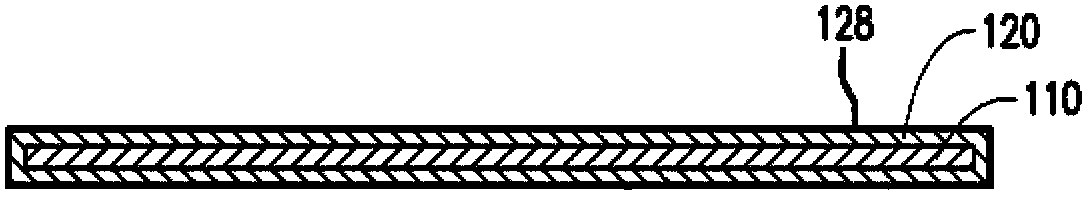

[0055] Next, please refer to Figure 1B , forming a metal layer 120 on the metal substrate 110 , wherein the metal layer 120 completely covers the metal substrate 110 . In this embodiment, the method for forming the metal layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More